# Purcease of the second second

# Distinctly different.

Our books are written by recognized industry experts. At around 8,000 words, they are unique in that they are able to be incredibly focused on a specific slice of technology.

> "I-007ebooks are like water in the desert ...it's up to you to drink it in order to survive!"

> > Stephen V. Chavez PCEA Chairman, MIT, CID+

#### **VISIT OUR LIBRARY**

# The heat is on!

## Thermal Management with Insulated Metal Substrates

Didier Mauve and Robert Art Ventec International Group

#### JULY 2022 • FEATURE CONTENTS

Thanks to the "left shift" of signal integrity functionality too early in the design cycle, more designers are using field solvers than ever before. But even experienced SI engineers risk "garbage in, garbage out" if they input the wrong data. This month, we focus on the proper use of field solvers and how to avoid getting hurt by GIGO.

52

#### FEATURE INTERVIEWS & ARTICLES

10 Surveying the Land of Field Solvers Interview with

Todd Westerhoff and Bill Hargin

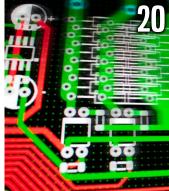

- 20 The Great Divide in PCB Simulation Software by Zach Peterson

- 34 Cadence Provides 'Clarity' in Design Tool Interview with Brad Griffin

The Practical Side of Using EM Solvers

**FEATURE ARTICLES**

**Using EM Solvers** by Heidi Barnes 繠

#### **FEATURE COLUMNS**

26 Field Solver Finesse for Modelling Transmission Lines by Martyn Gaudion

40 2D Field Solver—An Essential Tool for High-speed PCB Design by Barry Olney

## Candor Circuit Boards

# Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

#### www.candorind.com | (416) 736-6306

#### JULY 2022 • ADDITIONAL CONTENTS

# DESIGNOOT

#### SHORTS

24 BOOK EXCERPT: The Printed Circuit Designer's Guide to... Thermal Management with Insulated Metal Substrates, Volume 2

HFI D

- 39 Infographic: EV Battery Critical Materials

- 45 IPC Issues Call for Participation in IPC E-Textiles 2023

- 61 University of Illinois Researchers Create Low-cost, High-yield Plastic Microprocessors

- 65 All Systems Go: Accelerate Your PCB Designs with Machine Learning

#### DEPARTMENTS

81 Career Opportunities

94

- 95 Advertiser Index & Masthead

- 6 DESIGNO07 MAGAZINE I JULY 2022

#### ARTICLES

58 Final Finishes— ENIG and ENIPIG by Anaya Vardya

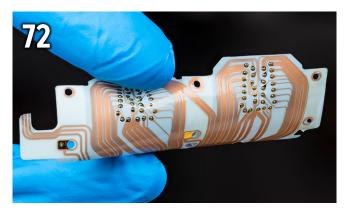

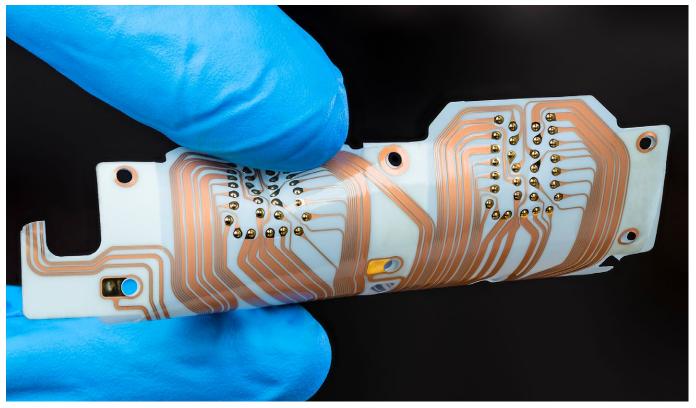

72 The Importance of Rigid-Flex PCB Design Guidelines

by Cody Stetzel

#### COLUMNS

8 With Field Solvers, GIGO Hurts by Andy Shaughnessy

46 Supply Chain Resilience, Part Two: The Solution by Stephen V. Chavez

- 62 Can Solvent-free UV-Cure Coatings Increase Stability and Throughput? by Saskia Hogan

- 66 Manufacturing Documentation: Keep the Builder in Mind by Tim Haag

#### HIGHLIGHTS

- **32** PCB007

- 56 MilAero007

- 70 Flex007

- **78** Top Ten Editor's Picks

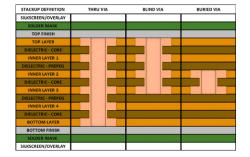

### Shift Stackup Planning into Design

Siemens' Z-planner Enterprise software provides detailed stackup planning early in the initial design process, allowing you to optimize your PCB stackup early. Conduct pre-layout signal-integrity simulations based on the actual materials your fabricators will use. By shifting this awareness 'left' in the NPI process, you will eliminate the expensive delays typically experienced after a design has been released.

Shift left with Z-planner Enterprise today.

SIEMENS

siemens.com/Zplanner

# With Field Solvers, GIGO Hurts

#### **The Shaughnessy Report**

by Andy Shaughnessy, I-CONNECT007

The "left shift" concept has been underway for at least five years, as EDA tool providers offer more powerful functionality earlier in the stages of PCB design and layout. This month, we focus on one tool that's been shifting leftward for some time now: the field solver.

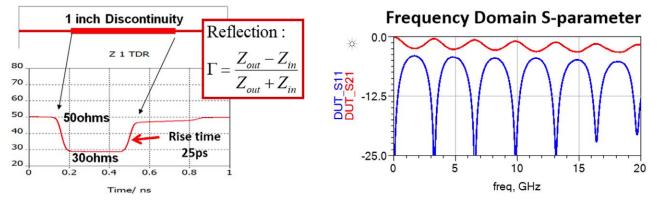

Once the domain of the experienced SI engineer, these computational tools—or at least some of their functions—are now available in PCB design software tools. With improved user interfaces, field solvers are being used by PCB designers and design engineers, many of whom have not mastered electromagnetics theory. Electromagnetic theory all starts with James Clark Maxwell, whose four differential equations form the framework for understanding e-mag theory. Field solvers are complicated programs that solve a subset of Maxwell's equations. Field solvers come in 2D, 2.5D, and 3D formats, and use several methods, such as the finite element method (FEM), finite difference (FD), and boundary element method (BEM) to extract parasitic circuit models.

When we first started planning this issue on field solvers, one thing became clear right away: Field solvers can be fairly difficult tools to use, even for veteran SI specialists, and it's

even tougher to make sure that you're using the correct data so that you get the results that you need. Signal integrity experts we spoke with said that even experienced engineers could wind up with "garbage in, garbage out" (GIGO) if they aren't careful.

There are hundreds of ways to go wrong with a field solver. As we see in this issue, some cases of GIGO derive from plugging in the wrong data, such as using IPC spec sheet info about board thickness instead of the "as pressed" number from your fabricator. Other designs have gone awry when field solver users didn't account for Dk changing with temperature. We heard a chorus of engineers saying, "Don't trust datasheets."

This particular left-shift is happening for a reason: There just aren't enough full-time signal integrity experts with advanced degrees and decades of experience in the industry. And if you can find them, they (rightly) charge a lot of money for their services. There are far more PCB designers than there are SI experts, so left-shifting computational horsepower into the hands of the PCB designer is a great way to mitigate this shortage of SI gurus.

But for a non-degreed PCB designer, using a field solver might feel like drinking from a firehose.

Design tool companies would love to develop a field solver with "PhD" (Push here, dummy) functionality. But we're not there yet. You still must know something about Maxwell's equations, or you're going to have problems.

So, for this issue, we asked our expert contributors to share their thoughts on field solvers, and what new users need to know to get up to speed. Todd Westerhoff and Bill Hargin discuss the evolution of field solvers and offer some handy tips and techniques for new users. Zach Peterson focuses on the divide between typical field solvers and layout software, and the need for the two to converge into one environment. Columnist Martyn Gaudion details a bit of "field solver finesse" for the modeling of transmission lines. Brad Griffin and Nolan Johnson explore Cadence's Clarity field solver functions, and columnist Barry Olney digs deep into cutting-edge techniques for the 2D field solver. Heidi Barnes takes a look at "the practical side" of field solvers and offers tips for avoiding GIGO.

We also bring you columns from Stephen Chavez, Tim Haag, and brand-new Electrolube columnist Saskia Hogan. We have an article by Cody Stetzel on flex guidelines, and another installment in Anaya Vardya's continuing DFM101 series.

It's summertime, but it doesn't look like this industry is taking much of a vacation! See you next month. **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 20 years. To read past columns, click here.

# Surveying the Land of Field Solvers

Feature Interview by the I-Connect007 Editorial Team

Electromagnetic field solvers have traditionally been used by a small slice of engineers the full-time signal integrity experts—and their use has been limited to the most demanding designs. But as design speeds increase, problems requiring field solvers are becoming more mainstream and field solvers are popping up all over the place, including free or inexpensive solvers available through an internet search. Many companies are claiming that their field solvers can be used by hardware design engineers without the SI background that solvers once required.

We asked Todd Westerhoff, product marketing manager for Siemens EDA, and Bill Hargin, CEO of Z-zero, to cut through the fog of field solvers and explain how engineers can ensure they avoid a "garbage in, garbage out" (GIGO) scenario when using field solvers to analyze their designs. **Andy Shaughnessy:** Let's start by defining a field solver. What exactly does a field solver do?

**Bill Hargin:** I think the simplest answer, Andy, is that a field solver is a black box that converts mechanical design parameters and material properties into a simulatable electrical model using Maxwell's equations. You give a field solver a precise dimensional description of a structure you plan to build, along with the materials it will be built from, and it gives you back a model that you can either examine directly or use as part of a system simulation.

There are two broad classes of field solvers used in PCB design: 2D solvers, which are used to predict transmission line (signal trace) behavior under specific conditions, and 3D solvers, which are more complicated to use, but provide accurate answers under gen-

## **Don't Overthink Your Prototype Builds**

### Go with the team that can make your ideas a reality...

#### • MICROWAVE • HIGH-SPEED • QUICK TURN EXPERTS

Accurate Circuit Engineering 3019 Kilson Dr Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: James Hofer (714) 227-9540

www.ace-pcb.com

Bill Hargin

eral-case conditions. 2D solvers have become mature enough that designers performing simulations may be using them without realizing it; they're embedded parts of simulation processes in some tools.

**Todd Westerhoff:** Let's take a step back. Why do we simulate our designs? Why do we simulate anything?

**Hargin:** So that we can predict the electrical behavior of our designs—the performance of our designs in advance.

**Westerhoff:** Precisely. We use simulation to predict whether something will work before we build it, so that we can debug and optimize our designs before we commit them to prototype fab. There's really only one question, or two, that we ever care about: Will it pass or fail against requirements, and by how much? The "by how much" part is operating margin and it's critically important. No simulation is ever 100% accurate; no matter how careful we are, we can't model and predict everything. Every simulation and every simulation result has a margin of error associated with it. When we simulate, we're looking to prove that the operating margin at the system level is substantially more than the margin of error in the simulation we performed. That's when we can say the design will work with room to spare.

When we talk about field solvers, we need to remember it's the margin at the system level that we care about. We need to model the structure in question (a transmission line, a package breakout, a differential via, etc.) as accurately as required to ensure adequate margin at the system level. But we don't want to model things more accurately than required, because that takes additional time and effort that isn't really moving the design forward; it's just analytical overkill.

There's a huge temptation to model everything as accurately as possible because we're engineers and we want to be precise—the hard part is knowing when that extra accuracy is required and spending our time judiciously. That's a hard call when we're dealing with field solvers. Eric Bogatin says the level of accuracy you need in your interconnect model goes up as your system operating margin goes down. I think that's a great way to frame it.

Hargin: At faster speeds, system margins decrease and the number things you need to worry about increases. You need to take a lot more care and consider the details in your design, because you need to precisely model the design as it will be built, not as you wish it could be built. That's the focus of my company, Z-zero, and our product, Z-planner Enterprise. We allow designers to model their PCB stackups more precisely, instead of just designing to an approximate stackup and hoping the new product introduction (NPI) engineer can work with a fab house to create a stackup that matches whatever we used for design simulations. There's really not much point in running detailed design simulations if you don't have an accurate description of the board stackup and material properties.

**Nolan Johnson:** Bill, when you said margins are dropping, are you talking design margins, constraint margins, or something else?

**Hargin:** Actually, both. Let's take PCI Express as an example because it's widely known. The data unit interval (UI) and its associated sampling region gets smaller from one generation to the next, because the data rate typically doubles. That means the signaling margin you must work with goes down, which ultimately means that the physical constraints on the layout have to become tighter.

Consider this analogy: You're driving through a course marked with traffic cones in a parking lot. If you're driving at 10 miles an hour, it's easy to stay on the path and avoid the cones. If you double your speed, it gets harder; if you double your speed again, it starts to get tough. That analogy assumes the cones stay in the same place; in the case of PCI Express, we'd not only be driving faster, but moving the cones closer together as well.

**Happy Holden:** Are all field solvers created equal? Is it true that the faster they operate or the more accurate they are, the more expensive they are?

**Johnson:** And how do you determine which field solver is the right one for you?

**Westerhoff:** Great questions. It depends on what you're trying to model, and the level of accuracy that you need. There are three different fundamental kinds of field solvers: 2D, hybrid, and 3D.

2D solvers are used when you have interconnect that has a constant cross-section, usually signal traces and cables. A 2D field solver provides the electrical characteristics per unit length, which are used as inputs for corresponding trace or cable elements in a circuit simulator. 2D solvers are well established, and they're built into many different simulation tools. If you've ever run any kind of post-layout

Todd Westerhoff

simulation from a layout database, chances are you've used a 2D solver whether you knew it or not.

3D solvers are used when you want to solve an arbitrary three-dimensional structure with high accuracy, usually vias, package breakouts, or high-speed connectors. 3D solvers discretize (mesh) the structure's entire volume and solve Maxwell's equations, which requires prodigious amounts of compute power and memory. 3D solvers present the most demanding technical challenges and generate the most discussion, so when someone says "field solver," that's usually what they're talking about. There are multiple types of 3D solvers, but for our current purposes we can just say that 3D solvers are used when the structure to be modeled can vary arbitrarily in the X, Y, and Z dimensions.

Finally, hybrid solvers are in-between 2D and 3D solvers. They're best suited to large structures that are essentially planar, like printed circuit boards. They use a variety of different techniques to identify and solve the different regions and behaviors in a structure, then integrate those results to provide the interconnect's overall behavior. They're well suited

for modeling large sections of boards where good, but not ultimate, accuracy is required, so they're often used for power-aware simulations and PDN analysis. Hybrid solvers are sometimes called 2.5D solvers, but that's really a misnomer.

**Hargin:** No matter which field solver you're using, providing an accurate description of the structure to be modeled is essential. There's no point of doing a detailed 3D simulation if the structure doesn't match what you will build. We're well past the point where we can get away with guesstimating important parts of the design like the stackup, and leaving the details to the manufacturing folks to figure out later.

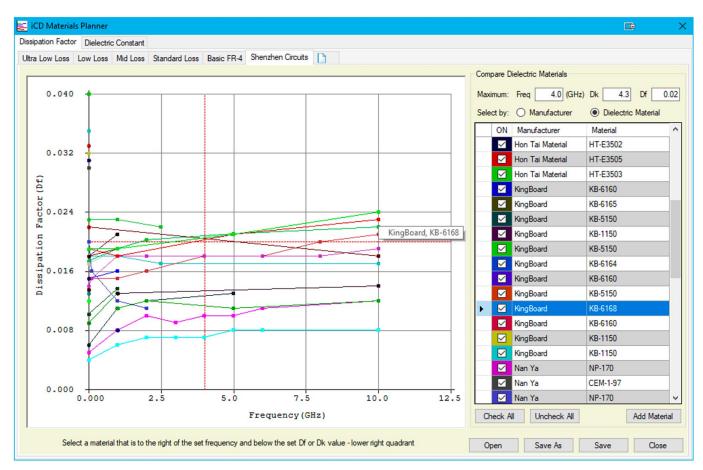

Traditionally, the NPI engineer took direction from SI experts on what trace impedances were required, then worked with the fab house to create a stackup that would meet those targets. Most fab houses used 2D field solvers like the Polar 2D solver to develop the stackup and document the resulting impedances. Key to this process was an accurate library of PCB materials and their electrical properties, and each fab house maintained their own.

With Z-planner Enterprise, we've gathered that material data and made it available to the system designer, so they can generate accurate stackups themselves. That means the design simulations they perform are more accurate, because they reflect a real stackup, instead of a hypothetical one. Designers can also use it to share stackups back and forth with their fab house and collaborate on potential changes. Z-planner is integrated with HyperLynx for SI and PI simulation, so designers can use accurate data for their design and verification work.

People commonly compare results from the Hyper-

Lynx 2D field solver to the corresponding ANSYS and Polar tools. These three provide very similar results and I think that provides a high degree of confidence in their accuracy. If you're using a different 2D field solver, it would be wise to compare it to one of these tools. As tempting as it is to say simulated results should always be verified against measurement, in cases like this, it's better to compare results to known good field solver results, because bench measurements introduce other issues.

For instance, when I measure a board, am I really measuring what I thought I was measuring? Let's say I'm measuring impedance and I want to compare two field solvers to a bench measurement. How do I know what the dielectric constant (Dk) of the laminate used in my bench measurement really is? There's typically a  $\pm 10\%$  variance on Dk values, so if I'm going to correlate a field solver to measurement, I must figure out the exact material properties for the particular board I'm measuring first. In this case, comparing to another known good field solver is a better way to validate how good a field solver is.

**Westerhoff:** Field solvers and simulators assume structures can be manufactured with precise material properties and physical dimensions, which they can't. If you want to predict how a

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

#### For more information visit downstreamtech.com or call (508) 970-0670

structure will behave in production, you need to add another process around the solver itself, so you can predict a real-world distribution of design behavior. That's tricky with a 2D solver, where the simulations run fast, and really tough when you start using 3D solvers, because the run times are much longer and the number of experiments you can run is limited.

We think an important (but under-discussed) issue with field solvers is accessibility to everyday users. Field solvers have traditionally been expert tools and there aren't enough SI experts to go around. The "expert crunch" has been a problem for years, and it isn't getting better. We've reached the point where even mainstream designs require the use of field solvers, and our SI experts only have time to spend on the most demanding designs. That means most designs won't get expert SI attention, so what are the rest of us supposed to do?

**Shaughnessy:** Signal integrity skills are sort of like a pyramid, aren't they? You have the experts at the top, a small number of people who are full-time SI engineers. Those are the people using field solvers today. You've got a bigger group in the middle who are skilled system designers, who'd like to be able to run analyses themselves but can't, because they don't have the right tools and processes. Finally, you've got the largest group at the bottom, who don't have access to simulation tools or enough understanding of SI principles to know how to apply them.

**Westerhoff:** That's especially true for 3D field solvers. There are lots of technical details associated with setting up and running a 3D simulation that produces meaningful results. The key word here is "meaningful." 3D solvers are complicated and it can be tough to get a simulation to just run in the first place. We can fall prey to the temptation to assume every result is valid simply because the solver itself is "known good." That's not true; correct simulation setup is critical to producing a good result and setting up 3D simulations is an expert user skill.

Here's a recent example of real-world "garbage in, garbage out." A customer was comparing our 3D solver to one they considered "known good." The two simulators weren't producing similar results, and the user assumed the problem had to be the HyperLynx 3D simulator. They contacted our AE and asked what was wrong with HyperLynx. Our AE realized the problem was actually with the simulation setup in the other tool; the signal traces were too close to the crop boundary, and that was throwing the results off. Once that was corrected, the two solutions correlated well. Interestingly, HyperLynx had set up the simulation correctly. The mistake occurred because the other solver just did what the user told it to. The lesson is that you must know how to set up a 3D field solver correctly, or it's "garbage in, garbage out."

The big challenge is this: How can we make these powerful simulation tools accessible to system designers? We can't expect system designers to take the time to learn all the ins and outs of setting up a 3D field solver.

**Shaughnessy:** It seems like some of the new field solvers coming out are aimed at this group.

**Westerhoff:** They claim to be. The challenge here is accessibility, not technology. The issue with 3D field solvers is that their development has always been driven by designs at the state of the art. The expert modeling the interconnect for 224G serial link design has very different needs than the system designer that just wants to validate a PCIe-5

board that was laid out using rules that supposedly guaranteed it would work. SI experts at the state-of-theart care about performance, capacity, and

accuracy first and foremost. It doesn't matter if the solver is hard to use; they can make it work no matter what. The system designer with PCIe-5 is literally the inverse: performance, capacity, and accuracy have to be good enough to produce a meaningful result, but the driving issues are integration, workflow, and usability. System designers need tools that they can deploy without having to become SI experts. If you walk into the cockpit of a Boeing 737, your first impression is probably, "This is really complicated. I could never fly this!" The fact is, that plane has an autopilot, and with minimal training and common sense, you could fly that plane.

Most field solvers are still like flying that 737 without the autopilot, so they require a SI expert. We've integrated the HyperLynx solvers with our SI tools and put a layer of automation around them so that process of identifying the area to be modeled, setting the crop boundary, defining signal ports, and setting up solver options is done for you. It's like using a 3D field solver on autopilot.

The challenge has been taking this sophisticated technology and developing algorithms that will let system designers generate meaningful results, then ensuring that automation works for a variety of real-world designs. We want to bring 3D field solvers to mainstream design by changing 3D analysis from an art practiced by a few skilled craftsmen to something more like 3D EM for production use.

> Shaughnessy: Are you trading off some level of accuracy for accessibility?

Westerhoff: With some of the automated flows, yes. If you really need that last few percent, you're probably an SI expert already and will turn off the autopilot to fly the plane manually, so to speak. Remember, the goal here is to enable a larger audience to run analysis themselves, reducing the demands on those overloaded experts. There are a lot of designs to get out the door, only a few of which require ultimate capacity and accuracy. That last few percent comes at an incredible cost in tool complexity and user expertise; we want to reserve SI experts for those cases where they are really needed.

**Shaughnessy:** So, you're looking to enable system designers who want to run analysis themselves. What advice would you give to a recent grad who has just started using field solvers? What's the takeaway for those guys?

**Westerhoff:** I think it's important to start with your ultimate goal. If you're trying to figure out whether your design works (and you should be), then everything else is a supporting detail. You need to know if your design passes or fails and by how much. You should therefore consider each element in the design in the context of system margin. Ask, "What process am I using to model the entire design? What process am I using to simulate it and assess success or failure?" When you need to use a field solver, ask, "What's the overall workflow? How will the field solver help me get my job done?" There needs to be an established workflow that someone who's not a SI expert can follow.

**Shaughnessy:** Bill, do you have any advice for anyone facing challenges using a field solver?

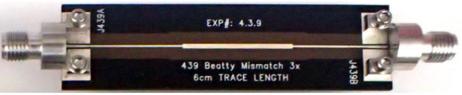

**Hargin:** You mentioned young engineers figuring out what's what. As I said earlier, you need caution and experience when comparing field solver results to bench measurements. Simulations assume everything is defined exactly, and the real world doesn't work that way. If you're comparing to bench measurements, you need to determine the correct material properties and dimensions for the as-manufactured device, and that can be difficult. If you're simply putting spec data into a field solver and getting different results from what you measure, that's probably why.

If you're new to the subject and asking about a good field solver, I cited three known good ones that correlate well enough that everything else should be compared to them. Finally, beware the free field solver, because we all know that you can go broke saving money.

**Shaughnessy:** Good advice. Thank you both, guys. This has been great.

Westerhoff: Sure. Thank you, Andy. DESIGN007

Bill Hargin is the author of The Printed Circuit Designer's Guide to... Stackups: The Design Within the Design.

MEETINGS Jan. 21-26 COURSES Jan. 21-26 CONFERENCE Jan. 24-26

# A D V A N C E IN A N E W E R A

ita analytics

cyber secu

automation

networking

backaging

substrates

innovation

transformation

## **CALL FOR PARTICIPATION**

**Factory of the Future**

You asked. We listened. Abstract submission deadline for IPC APEX EXPO 2023 has been extended to Monday, August 8.

IPC is accepting abstracts for technical paper presentations, posters, and professional development courses at IPC APEX EXPO 2023 in San Diego, the premier event for the electronics manufacturing industry!

#### **TECHNICAL TRACKS**

- Factory of the Future Implementation

- Enabling Future Technologies

- Meeting Extreme Requirements

- PCB Fabrication and Materials

- Design and Component Technologies

- Quality, Reliability, Test and Inspection

- Assembly Processes

- Electronics Materials

- Conscientious Engineering

ABSTRACTS DUE MONDAY, AUGUST 8, 2022

View more details

## **The Great Divide in PCB Simulation Software**

Feature Article by Zach Peterson NORTHWEST ENGINEERING SERVICES

Today's PCB design engineers have more layout and analysis tools at their disposal than ever before. Over the years we've seen layout tools become more automated, rules-driven, and more integrated. Now we even have integration between design tools from different vendors and ranging across domains, starting with basic circuit design, and spanning up to PLM and ERP integration. It really is a great time to be a designer.

But there is one area that continues to be a bit disconnected from the rest of the design process: simulation and analysis. Those of you who know me will know that I love simulation, and I love analyzing interconnects to death. If you're like me, then you probably prefer to do all this by hand. If not, there are plenty of electronics and electromagnetics simulation software suites to help you along the way. The problem with today's simulation software options is not their capabilities; if you shop around enough, you'll find a simulation for just about anything. The problem with the industry-standard simulation tools lies in where they fit into the standard PCB design workflow, as well as the user experience. Simulation software used in electronics and PCB design generally falls into one of the following categories.

- Circuit or schematic simulation tools (e.g., SPICE)

- 2D interconnect simulators implementing BEM or MoM

- Electromagnetic field solvers implementing FDTD, FEM/FEA, or a similar numerical method

## UP TO \$500 FREE EVERY MONTH Have one (prototype) on us!

### **Our free offer:**

When you order 6 prototypes (or more) within a calendar month, you will earn one FREE prototype (up to \$500- 1 to 6 layers) with our standard 5 business day delivery.

Offer ends 12/31/2022. Terms and conditions apply.

**GET STARTED**

MILTRONIX mil-tronix.com

All engineers and designers are probably familiar with SPICE; if you're not, you should be. I consider the ability to run a SPICE simulation a mandatory skill for any PCB designer. Advanced applications will go far beyond SPICE and should use some level of simulation to verify signal integrity, channel compliance, and EMI.

#### **2D Simulators**

Not all PCB design applications include a 2D interconnect simulator that can return impedance, reflections, crosstalk, and return path tracking in a PCB layout. Applications that do include these simulators will not have it running in the online DRC engine. For everyone else, there are both free and paid calculator applications that will give you a rough estimate of crosstalk and reflections.

Within the standard workflow, 2D simulators can work as a verification tool for interconnects once layout and routing are completed.

Within the standard workflow, 2D simulators can work as a verification tool for interconnects once layout and routing are completed. In most of these tools, the user interface is suboptimal. These are not point-and-click simulation tools that operate like DRCs. Some configuration is needed, and you need to know some inputs with high certainty to gain meaningful results. For this reason, these simulators are not often accessed while the design is being created; you'll find that users wait until the design is near completion to use these if they are used at all.

#### **Electromagnetic Field Solvers**

Field solvers are great for back-end verification once a design is completed, or for demonstrating feasibility of a circuit/interconnect on the front end. In between, while you're actually creating the design, they are practically absent. In any case, they are practically absent from the workflow for most designers. There is another challenge here; users of these applications need to be well-versed in methods for solving Maxwell's equations in all their various forms. That usually entails a graduate degree in engineering, physics, or mathematics.

The results from these programs are very accurate, but only as long as all the input data for simulations are also accurate. These programs suffer from "garbage in, garbage out"; if the input data used in a field solver do not match reality, then the field solver results won't match reality either. They also follow the same antiquated workflow you find in ECAD/ MCAD collaboration; you have to export the design from your ECAD software, then import it into the field solver.

So, what should simulation tools of the future look like? How can the CAD vendors and simulation software providers do better?

### Where PCB Simulation Tools Can Improve

Clearly, there is a lot of room for improvement in terms of user experience and workflow integration. Because the user experience for these tools can be difficult to manage for less-experienced designers, they get pushed to the beginning or the end of the design process; there is little simulation happening in the middle.

It would be great to see a simulation toolset that is built into PCB design applications and that can be invoked like your DRC engine. Personally, I would love to see something that is invoked like DRCs, but that is qualifying the design against a broader range of SI/PI/EMI metrics than just impedance, reflection, and crosstalk.

#### autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

#### venteclaminates.com

The best possible feature for the high-speed PCB designer would be instant qualification against signaling standards at the click of a button. This is a simple pass/fail type of evaluation tool. I'd like to know whether my DDR4 routing is actually going to comply with DDR4 standards before I get too far along in a design, otherwise we risk ripping up tracks and adjusting placement.

To be fair, some simulation platforms are working toward automating common field solver-based analyses that are required to evaluate SI/PI/EMI, as well as channel or standards compliance. Still, these tools come with a huge price tag, so the individual designer is effectively priced out of the market. A stripped-down, highly automated PCB simulation suite inside ECAD software would help level the playing field for designers of all skill levels. **DESIGN007**

Zach Peterson is the founder of Northwest Engineering Solutions and an Altium consultant.

#### BOOK EXCERPT

#### The Printed Circuit Designer's Guide to... Thermal Management with Insulated Metal Substrates, Volume 2

As the second in a two-part series, this book from Ventec builds on the material presented in the first by describing up-to-the-minute products and design techniques for thermal management with IMS.

The first volume comprehensively covers prin-

ciples of heat transfer and modeling of thermal systems to help engineers quantify the thermal-management challenges in the application at hand, the nature of IMS, typical material parameters, and the choices available for designers to reach the desired performance.

We recommend reading the first book in order to understand the issue from first principles, how to navigate the many material choices offered, and appreciate how adjusting the various combinations of material types and thicknesses can help you arrive at a solution that meets your requirements from all standpoints,

particularly system reliability, size, cost, and manufacturability.

The Printed Circuit Designer's Guide to... Thermal Management with Insulated Metal Substrates, Volume 2, covers additional use cases and materials, including those used for high-temperature applications as well as high-emissivity surface treatment that can significantly enhance thermal

<section-header><section-header><section-header><text>

size of baseplate needed to achieve the desired thermal performance in the smallest possible volume—much smaller than would be possible using a suitably sized heatsink.

performance. A web-based thermal calculator

is demostrated, which helps arrive at the exact

Volume 2 delves deeper into issues such as test methods and how these can affect assessments of IMS materials and analyzes the effects of tolerances in material properties and thickness on the overall thermal conductivity. Understanding this can critically influence measurement error, ultimately determining whether or not an accurate result for reliability can be calculated. The authors look at how problems such as solder cracks affect thermal performance, and share application examples showing design with multilayer IMS. As application challenges have

evolved, and new component types and thermal materials have entered the market, there is more to say about thermal management and the options available to designers striving for an effective, economical, and compact solution to meet systemreliability targets.

#### Download this title today!

#### **BENDING THE POSSIBILITIES**

BY TAIYO

#### AVAILABE IN TWO COLORS

AMBER

BLACK

🐨 Excellent bendability

$\bigcirc$  High Resolution by photolithography

- 😵 High Reliability

- Simplified process

- **W**UL94 VTM-0 certified

- S Low spring back force

- Resolution Line/Space=50/50µm

- Solder mask defined opening (30µm diameter)

#### **OUR BIGGEST FLEX YET!**

Contact your local sales representative today!

Visit www.taiyo-america.com for more information.

# Field Solver Finesse for Modelling Transmission Lines

#### The Pulse

Feature Column by Martyn Gaudion, POLAR INSTRUMENTS

When I-Connect007 asked me to contribute to this issue on field solvers, I wondered what more could be added to this subject. But as a supplier and developer of field solvers, Polar is still asked some of the same questions—both by experienced customers who are perhaps exposed to a new scenario and, as is most welcome, by new entrants to the industry.

I will start by saying that all field solvers are accurate; they solve Maxwell's equations by one or another of the available mathematical methods. When all are fed with the same data, all should generate very similar results, and any differences observed will be orders of magnitude less than the variations in the PCB transmission lines caused by the composite nature of PCB substrate dielectrics and the variations of the plating and etching processes.

However, field solver is a very generic term for a range of tools in this application for pre-

dicting the behavior of PCB transmission lines. It is important to remember that some areas of field solvers are not actually field solving. Calculating the loss owing to surface roughness of copper is a prime example of this. The surface nature of plated copper is so complex that full field solving would be impractical, so most commercial "solvers" will overlay the core field-solving function with empirical techniques: Hammerstad, Groisse, Huray, and Cannonball-Huray, to name just a few. These empirical extensions extend the capability of the field solver into modelling parameters that are:

- Vital to model insertion loss

- Impractical to field solve given the complexity of the surface profile and the available compute power in the hands of even the best equipped SI engineers

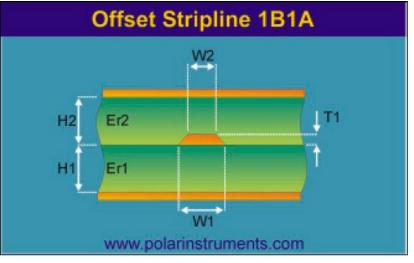

Feeding the solver with the correct dimensions is vitally important, as no tool will give an accurate result if fed with incorrect start parameters. Customers frequently ask whether the transmission line structure height should include the trace thickness in the total height. This is easy to answer if you are working "backward from a microsection" but if you are imagining the finished PCB from a simulation, then it's less obvious.

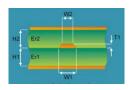

My question in Figure 1 is set as a puzzle as it is one of the most frequently asked items

Figure 1: Does H2 include the copper or not?

### QUICK TURN PCB & ASSEMBLY

All Under One Roof!

#### FRUSTRATED DEALING WITH MULTIPLE SUPPLIERS?

Hundreds of customers have taken advantage of our "One-Stop PCB Solution"

Get a Free SMT stencil on your 1st Assembly order (when you mention this ad)

6 0 m

#### PRECISION ADVANTAGE

For the past 25 years, we have been helping PCB Designers, and Engineers avoid unintended design flaws and prevent costly errors. With our technically knowledgeable team and expertise in time sensitive, quick turn PCB Fabrication and Turnkey PCB Assembly services, we guarantee the highest quality and reliability of your products.

#### Let us help you get your products to market today!

#### sales@eprotos.com 1-888-228-9440

Precision Technologies is certified and registered: UL94V-0, ISO-9001:2015, ROHS & ITAR, CAGECode 7T6D9 DUNS 092237267

#### STRATEGIC SOLUTIONS

| 1 | Avoid Communication Gaps   |  |  |  |

|---|----------------------------|--|--|--|

|   | Prevent Engineering Delays |  |  |  |

- Single Point of Contact from Sales through Delivery

- Streamlined Process Fab to Assembly

- Consistent Quality Results

- Prototype and Production

LEADING THE WAY SINCE 1998

GET A QUICK QUOTE NOW!

regarding transmission line modelling. The H1 dimension represents the core thickness, and the H2 dimension is that from the top of the core to the foil. You can see H2 is denoting prepreg as the trapezoid is pressed into the Er2 region. By how much? Well, if you work from a microsection, the dimensions will be clear to see. But when modelling with a solver before the board is built, you must make a prediction as to how much the T1 will impact the H2 dimension.

Think about it: If there is a lot of copper on the signal layer, most of the T1 will need to be added to the pressed thickness of the prepreg; if the routing density is low, then far less. This is where a stackup tool comes in handy, as a good stackup tool will virtually press the prepregs and consider the Cu density on the signal layer to calculate the optimum value for H2 to feed into the solver. This is the point I was stressing earlier: Commercial PCB transmission line field solvers must possess a variety of tools and capabilities over and above the core solver engine to feed it with good mechanical data to solve.

As you look at Figure 2, consider the question posed by Figure 1. By using Speedstack to pre-process the material data, the pressed height of H2 and the impact of T1 have been calculated to feed into the solver engine. The left-hand side of the image shows the raw prepreg thicknesses. The signal trace (shown in blue) has a 5-mil core below and two sheets of 3-mil prepreg above. Another core is placed above the two prepregs at the top extent of the highlighted area. Now look at the structure on the right-hand side of the picture. This is an offset stripline located with the signal on the blue layer on the LHS.

As you would expect, H1 = 5 mil—the lower core thickness—but H2 does not equal 6 mil (3 mil plus 3 mil prepreg). H is calculated as 6.28 mils, the combined thickness of the structure when the two sheets of prepreg are pressed into the copper distributed on the signal layer. Taking care of this type of pre-processing is

|    |     | edstack Stack Up Buil | 5                              | .ayer_Step5_CI.stk Project : FlexRigic | l_12Layer_Step5_Cl.sci                  |                                      |                                                                                  |                              |            | ;   |

|----|-----|-----------------------|--------------------------------|----------------------------------------|-----------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|------------------------------|------------|-----|

|    |     | View Tools U          |                                | eep                                    |                                         | 777                                  | 1 T 🕫 🗓                                                                          | 🗮 🍠 🗂                        | <b>É</b> 1 |     |

|    |     |                       |                                |                                        |                                         |                                      | Stack Up Editor DRC : 10 Cont                                                    | trolled Impedance CI Results | 1          |     |

|    |     |                       |                                |                                        |                                         |                                      |                                                                                  | 1 of 1                       |            | GHz |

|    |     |                       |                                |                                        |                                         |                                      |                                                                                  | Offeet Stripline 1B1A        |            |     |

|    |     |                       |                                |                                        |                                         | 1.4000                               | -                                                                                | .W2                          |            |     |

| SI | м   | Liquid Photolmagea    | able Mas <b>k</b> 4.000/0.0000 | - In a north                           | and a                                   | A CONTRACTOR OF                      | H2 812                                                                           |                              |            |     |

| Fo | bil | Copper Foil           |                                | JAN CEEEE                              |                                         | 1.4000<br>5.0000<br>1.4000           | <u>,</u>                                                                         |                              |            |     |

| PF | P   | PrePreg 1080          | 4.200/0.0000                   |                                        |                                         | 3.0000                               | н1 вп                                                                            |                              | 1°         |     |

| C  | ore | FR4 Core              | 4.200/0.0000                   |                                        |                                         | 1.4000<br>5.0000<br>1.4000           |                                                                                  | arinstruments.com            |            |     |

| PF | P   | PrePreg 1080          | 4.200/0.0000                   | Wenner and and                         | en and l                                | 3.0000                               |                                                                                  | W1                           |            |     |

| Co | ore | FR4 Core              | 4.200/0.0000                   |                                        |                                         |                                      | Substrate 1 Height                                                               | H1 5.0000                    | _          |     |

| P  | P   | PrePreg 1080 NF       | 4.200/0.0000                   |                                        | /////////////////////////////////////// | 1.4000<br>5.0000<br>1.4000           | Substrate 1 Dielect<br>Substrate 2 Height                                        | H2 4.4000                    | _          |     |

| C  | ore | Polyimide Film        | 4.200/0.0000                   |                                        |                                         | 3.0000<br>1.4000<br>5.0000<br>1.4000 | Substrate 2 Dielect<br>Lower Trace Width<br>Upper Trace Width<br>Trace Thickness | W1 2.5625                    | _          |     |

| PF | P   | PrePreg 1080 NF       | 4.200/0.0000                   |                                        | //                                      |                                      | 11000 1110111000                                                                 |                              |            |     |

| C  | ore | FR4 Core              | 4.200/0.0000                   |                                        |                                         | 3.0000<br>1.4000<br>5.0000<br>1.4000 | Impedance<br>Target Impedance                                                    | Zo 50.12<br>50.00            | _          |     |

| PF | Р   | PrePreg 1080          | 4.200/0.0000                   | 1                                      |                                         | And the second second                | Target Tolerance ?                                                               | 6 10.00                      |            |     |

| C  | ore | FR4 Core              | 4.200/0.0000                   |                                        |                                         | 3.0000<br>1.4000                     |                                                                                  |                              |            |     |

| PF | P   | PrePreg 1080          | 4.200/0.0000                   |                                        |                                         | 1                                    |                                                                                  |                              |            |     |

| Fo | oil | Copper Foil           |                                | 700 700                                |                                         |                                      |                                                                                  |                              |            |     |

| SI | М   | Liquid Photolmagea    | able Mask4.000/0.0000          |                                        |                                         |                                      |                                                                                  |                              |            |     |

|    |     |                       |                                |                                        |                                         |                                      | 1                                                                                | 8000 V22.01.01               |            | _   |

Figure 2: Auto virtual pressing and calculation of H2.

### Integrated Tools to Process PCB Designs into Physical PCBs

Use manufacturing data to generate a 3D facsimile of the finished product.

nsure that manufacturing data is accurate for PCB construciton.

Verify and Optimize PCB Designs for Successful Manufacturing BluePrint-PCB Create Comprehensive Documentation to

Create Comprehensive Documentation to Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 downstreamtech.com ©2019 DownStream Technologies, Inc. All rights reserved.

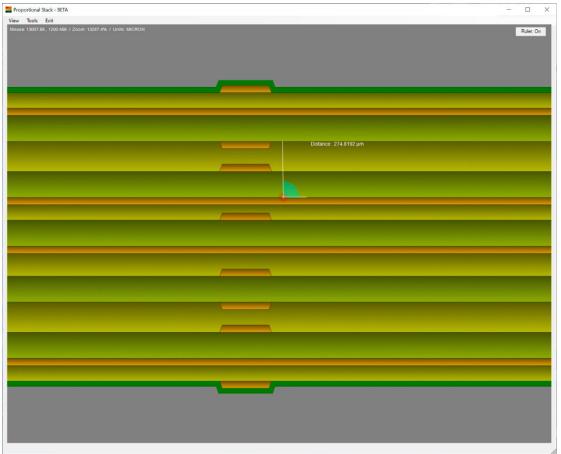

Figure 3: As a "sanity check" a proportional view lets you view real dimensions.

the key to obtaining accurate predictions from your solver.

Viewing the stack in Figure 2 as a schematic view with fixed size layers for materials is ideal from a planning perspective, but once the stack is complete and pressed, a proportional view makes it plain to see if you have added incorrect materials in error—in the blink of an eye.

#### Conclusion

I have used a small sample of the techniques you need to deploy to ensure that a field solver engine is fed with accurate data. Quality material data from the supplier is also key in this process, but the key takeaway is that, when looking at the appropriate field solver for your requirements, you must always remember that all solvers are accurate; it is the pre-processing of the data being fed to the solver which unlocks its full potential. This is true for lossless lines up to around 2GHz on through to ultra highspeed lines where insertion loss needs serious consideration too. You should also take care that measurement data is validated, but that is the topic of another article—already partially covered in my April 2022 column in *Design007 Magazine*, "Using Touchstone Files to Build Measurement Confidence." DESIGN007

Martyn Gaudion is managing director of Polar Instruments Ltd. To read past columns, click here.

#### Additional content from Polar:

- The Printed Circuit Designer's Guide to... Secrets of High-Speed PCBs, Part 1 by Martyn Gaudion

- The Printed Circuit Designer's Guide to... Secrets of High-Speed PCBs, Part 2 by Martyn Gaudion

- View other titles in our full I-007e book library here

# Better Together.

These books can help you streamline your process.

l<mark>·007</mark>e Books

# PCB007 Highlights

#### Review: Institute of Circuit Technology 2022 Annual Symposium ►

The British Motor Museum in Warwickshire, housing the world's largest collection of historic British cars, was venue for the 2022 Annual Symposium of the Institute of Circuit Technology, which attracted a substantial gathering of manufacturers and suppliers from the UK printed circuit industry.

#### Happy's Tech Talk #8: Copper Etchant Regeneration >

Copper has become a valuable metal, and with the growth of EV has come higher currents needed with increasing weight of copper in PCBs. This creates the need for increased copper etching and consumption of copper etchants.

### FTG Circuits Fredericksburg Requalifies for IPC-1791 QML ►

Firan Technology Group Corporation announced that IPC's Validation Services Program has awarded requalification for IPC-1791, Trusted Electronics Fabricator Requirements Qualified Manufacturers Listing (QML) to FTG Circuits Fredericksburg, Virginia.

#### The Chemical Connection: How Industry 4.0 Shapes PCB Wet Processes ►

Earlier this year, I had the opportunity to attend IPC EXPO 2022 where I was able to network with many great people in our industry. Although that might have been my main takeaway, there was another trend that I couldn't ignore: the fourth generation of the industrial revolution is alive and well in the industry.

#### Atotech Sells 1,000th Horizontal Electrolytic Copper Plater >

Atotech, a market leader in advanced electroplating solutions, announced the sale of its 1,000th horizontal equipment for electrolytic copper plating.

#### IPC Establishes European Subsidiary ►

To better support our European members' interests, IPC announces the formation of IPC Electronics Europe GmbH. The subsidiary was officially registered with the German government on May 4, 2022. The new entity's main office is located in central Munich.

### Mike Carano Joins the Averatek Team as Vice President of Quality ►

Averatek is pleased to announce that Michael V. Carano has joined our corporate leadership team as vice president of quality. Mike brings 40 years of electronics industry experience, with special expertise in manufacturing, chemicals, metals, semiconductors, medical devices, and printing.

#### Calumet Students Take First Place in 'Michigan Girls Future Flight Challenge' >

Two Upper Peninsula girls recently took the Michigan aerospace industry by storm! CLK Washington Middle School students Jordan Hicks and Kristen Ylitalo outperformed more than 20 teams throughout the state in the "Michigan Girls Future Flight Challenge," hosted by the Women of Aerospace Industry Association of Michigan.

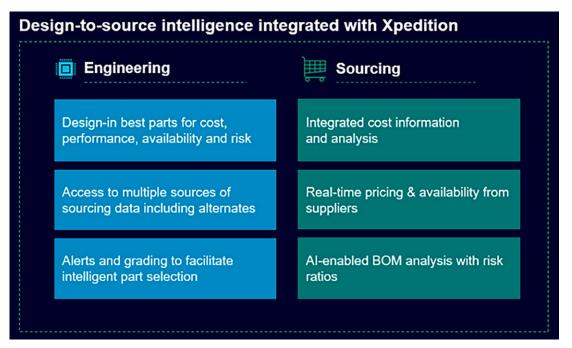

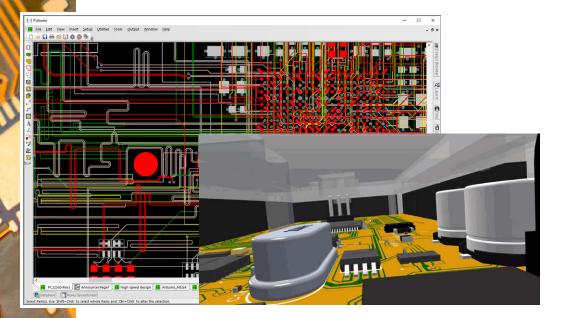

## Integrated PCB Design, Effortless Collaboration

#### Collaborate From Anywhere, Innovate From Everywhere With OrCAD for Teams

Optimize every part of your design process with the only real-time PCB design and data management platform built to scale with you and your team. From automated supply chain insights and constraint-driven, high-speed design and analysis to one-click release-to-manufacturing, OrCAD for Teams is architected to help you work more efficiently and effectively than ever before.

Get OrCAD for Teams >>>

# Cadence Provides Clarity in Design Tool

Feature Interview by Nolan Johnson I-CONNECT007

Nolan Johnson recently spoke with Brad Griffin, product marketing director for Cadence Design Systems, about Cadence's Matrix solver technology. They discuss its use as a multi-disciplinary field solver as well as Cadence's focus on thermal analysis and utilizing the power of the cloud.

**Nolan Johnson:** Brad, now more than ever you must make decisions in design that are going to impact manufacturing.

**Brad Griffin:** I agree with you. Cadence is very uniquely positioned because we've always had PCB and IC packaging design tools. So much of what we used to do on a printed circuit

board is now done in silicon on a silicon interposer. The tools that are used at the board and package level have had to evolve to be able to support the new types of designs.

We're engaged through the whole process. That's where field solvers come in because if you're a printed circuit board designer and you're laying out a board, you may not even think about a 2D field solver running in the background, calculating impedance for you to tell you that you've met the 50 ohms of impedance that you were trying to get to. Those tools are embedded in the design tools, and the users don't even know they're running an EM solver. But as you get into more involved work, where you're sending 64 bits simultaneously at

# Is Your Current PCB Supplier Pushing Out Lead Times That Are Unthinkable? APCTPICASE

# APCT Values Being A Partner, Not Just A Supplier

- Operational Support to Assure Availability & Required QTA Lead Times

- Engineering Expertise to Advise on New & Emerging Technologies

- Customer Service "That Is Best In Class"

### The Solution Is APCT

#### Work With A Partner, Work With APCT

APCT.com 408.727.6442 714.921.0860

APCT Santa Clara HQ APCT Anaheim APCT Orange County 714.993.0270

APCT Wallingford 203.269.3311

**APCT Global** 203.284.1215

five gigabits per second on a DDR5 bus, things get to a point where you need to look at the signal, the power, and the ground because now they all interact. That's the same, whether on a board, on the package, or whether you're on an interposer; you just may use different material properties to be able to model the interconnect.

A sophisticated, full wave 3D field solver can work in all those types of applications if it has the speed, the capacity, and the ability to crunch that large of a problem. That's where Clarity 3D Solver comes in. It's unique in the industry in its ability to apply Maxwell's equations to make accurate, full-wave 3D assessments of how the interconnect is going to behave, do so on a very large scale, and in a timeframe that allows an engineer to make a decision based on that simulation results.

**Johnson:** Not in post-processing, but during the design process?

**Griffin:** Again, it's always going to vary, but you're right. For example, if somebody is routing that differential pair and they really

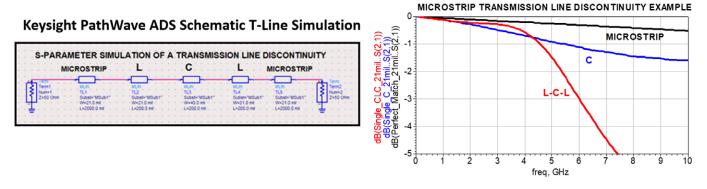

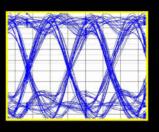

don't want to put any vias in place because they know it's going to cause some discontinuity, but they need to find out if it will work, then this is where, in design, you can call on Clarity in the middle of design. Clarity can give you an S parameter. You can plug that S parameter into a circuit simulator, and you can look at the eye diagram and determine whether it will work. You can make that decision in design instead of waiting until the end, with your fingers crossed hoping that it's going to work.

That's the case where you probably get your answer back in minutes. There are other cases where you're looking at something bigger and you're saying, "I'm willing to let

this run overnight." Again, I think this is where Clarity comes into play, where other field solvers might be running for weeks before they get the answer. The speed and the capacity of Clarity is really opening up what signal integrity and power integrity engineers can do in the design process.

**Johnson:** I've been hearing a lot about Sigrity X. Tell us about it.

**Griffin:** Sigrity X is what we call the new version that has the 10X faster simulation capabilities. That's where the matrix solver comes in.

**Johnson:** Are we still living in a world where you can have these processes running for days and weeks?

**Griffin:** Oh yes, absolutely. We see this all the time. If the compute power is there, people will use it. They must simulate this altogether as one structure, and they're willing to wait a week for that answer, if that's what it takes. Then we show them they can get it done in 10 hours now. That's a big difference.

It's amazing how much faster some of these solvers are, but once they've got that, they'll just make the simulation bigger, so our customers will still run the Clarity solver for days. We've connected Clarity to the cloud through AWS, so now you have almost unlimited computing resources, but there's always a cost associated with it. While the solver can run much faster, maybe they don't want to use all the licenses required, so they might say, "I can get it done in 10 hours, I'm okay with that, even though I could use 10 times the licenses to get it done in one hour."

**Johnson:** You do get to trade that off: how much resource you want to pay for vs. how fast you want to get your results. Is Clarity standalone up on the cloud now?

**Griffin:** It's a hybrid. You do all your setup locally from your machine because that's interactive. It's not really compute intensive; you're making decisions. Then, when you hit the simulate button, specify to simulate in the cloud. It just packages everything up, encrypted, and runs the simulation in a secure chamber where nobody has access to it. When complete, it then ships it all back to your machine. To you as the user, they don't really see a difference. I think that's the real power of what we've created with the cloud version of Clarity.

**Johnson:** How is this going to change the engineers' way of doing their job?

**Griffin:** Engineering is a game of "get me the best answer you can as fast as you can." What we've done largely before Clarity is we've seen many of our customers rely on what is called a hybrid solver. For some of these jobs I was talking about that are taking hours, the hybrid solver might take 10 or 15 minutes. You can get a basic idea of how things are going. Engineers will continue to use different tools at different times. The biggest breakthrough is that with all these compute resources now available—

either on-premises or in the cloud—there's software written to take advantage of that. The main thing that Clarity brings to the table is that the other tools on the market were written when people still used single-core machines.

I think it's just so empowering for an engineer to have this capability when they want it. They're still going to make the quick changes, quick decisions in-process. But at some point, they're going to run their simulation overnight.

**Johnson:** I am hearing a series of iterations in the design process: quick checks while working with small sections, transmission lines, etc. You want to make sure that everything is maintaining spec, piece by piece, and then move up to a module within your entire design. Even though you were in-spec at the transmission line level, it still behaves and within spec when put all together.

We're finding most thermal tools are bent toward the mechanical engineer. But really, the electrical power is what's causing thermal issues in the first place.

**Griffin:** And no surprises when you get that prototype back; that's what you're aiming for. We're seeing the same thing in thermal because all these processors are so power intensive these days, especially as things get smaller.

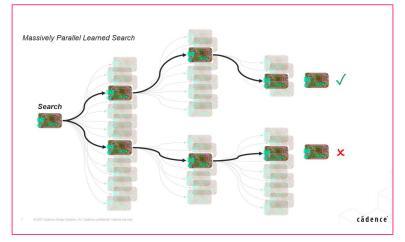

We're finding most thermal tools are bent toward the mechanical engineer. But really, the electrical power is what's causing thermal issues in the first place. If you can take all the detail of the power delivery network and make that part of your simulation, that's thanks to what we call a massively parallelized matrix solver, that we use in Clarity. We also use it in our thermal tool called Celsius. And so the massive parallelization of being able to break that problem apart and solve it in parallel and then bring it all together and give accurate results. That's what really empowers us to do that.

We have this massive parallelization because they solved this on the IC side a long time ago for the Voltus power delivery network tool. That matrix solver was developed to solve a much bigger problem. And then as these system problems become the bigger problems, the technology is waiting for us, ready to be reused in the PCB space.

Johnson: Where else is it being used?

**Griffin:** PDN power integrity. The main areas are SI, PI, thermal, and then the chip level power as well. We had a customer call us, and he was using the version of our tool from two years ago. He said, "It's taking five days to solve this." This was with the version I told you normally happens in 15 minutes. This guy was running a really big problem and it was taking five days. We said, "Well, have you tried the new version?" He said, "Oh, I don't have a license for that." So, we got a demo license for everything. He ran the simulation, and results came back in eight hours.

**Johnson:** Five days down to eight hours. That's nice.

**Griffin:** It works. It basically works across all the different tools that we have. We have all this technology in the IC side, we've brought it into the system tools. It's no longer a feature thing. Engineers are empowered. It's just so frustrating when these full wave 3D field solvers force you to break it down to something so small that your computer will actually solve it. Then when you solve it, you don't know if the results are right. It's so frustrating. With us, you just don't break it down. You just put the whole thing in, you solve it. It uses potentially more computing resources, but it's also more efficient.

We used to talk about the three types of simulations for signal integrity matters. The first is while you wait; push the button, get your answer back. Then we have the coffee break because you talk to somebody for a few minutes, while your answer comes back. Then there was overnight. What happened is the problems got more and more complicated; overnight became over the weekend and over the weekend became over the week. Now what we've done in many cases is brought it back to overnight.

**Johnson:** Right. And six and a half days into a seven-day run and it crashes.

**Griffin:** That can certainly happen when you're consuming the amounts of memory that these tools are. I don't want to say we're perfect. But we do hear from customers that the other tools crashed six times, but the Clarity tool worked. With limited resources to simulate within his boundaries we were able to solve this problem.

**Johnson:** That's the magic. Anything else about this that we should talk about?

**Griffin:** I think we talked through the cloud, and we talked about Celsius. We talked about Sigrity X, which is what we call the new version that has the 10X faster simulation capabilities. And that's where the matrix solver comes in. So those are the three things that I would like to highlight.

Johnson: Excellent. Brad, thank you.

Griffin: Sure. My pleasure. DESIGN007

Download *The System Designer's Guide to... System Analysis* by Brad Griffin along with its companion book *The Cadence System Design Solutions Guide.* You can also view other titles in our full I-007e book library here.

# **The EV Critical Battery Materials Boom**

### WHERE DOES THE LITHIUM ORE COME FROM?

## 1000%

Expected growth in demand for minerals needed to make EV batteries by 2050

Source: PBS

Source: Atlassons Business Services Private Limited

# The average 70 kw/h EV battery pack contains

77 lbs.

31 lbs.

Source: Energy X

**18 lbs**.

### AS EV SALES INCREASE, MORE LITHIUM WILL BE NEEDED

# **2D Field Solver**—An Essential Tool for High-speed PCB Design

### **Beyond Design**

Feature Column by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

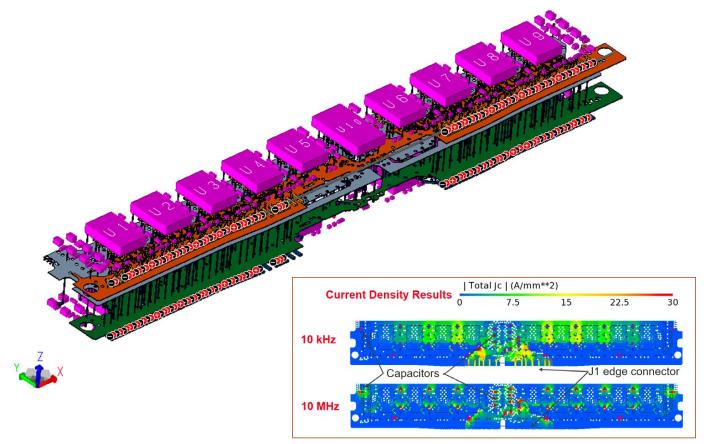

A field solver is the engine behind signal and power integrity analysis. You never see it, but it performs all the magic of simulation. In its elementary form, the field solver can employ Maxwell's equations to calculate the parasitic elements of a solution space. This method is referred to as 2D extraction and is used to analyze and synthesize a stackup to achieve a target single-ended or differential impedance. The velocity of propagation can also be extracted to perform signal integrity analysis. A field solver can be used as a stand-alone tool or as part of a simulation environment. In this month's column, I will look at 2D field solvers. An electromagnetic (EM) field is produced when a logic driver delivers a high-speed, fast rise-time pulse into a transmission line. The EM wave propagates along the length of the trace radiating into the surrounding dielectric material and coupling energy to nearby trace segments. These EM fields are not restricted to the multilayer substrate and if proper care is not taken may emit radiation causing electromagnetic interference. If the impedance of the driver and load do not match the transmission line, then reflections occur, and radiation is created. Hence, the need for impedance control.

| ile         | Edit  | Export                | Import To          | ols Setu      | p Help                                                       |                 |                         |                     |                    |                |        |                                  |                                      |                                         |

|-------------|-------|-----------------------|--------------------|---------------|--------------------------------------------------------------|-----------------|-------------------------|---------------------|--------------------|----------------|--------|----------------------------------|--------------------------------------|-----------------------------------------|

| 12          |       | 20                    | 2 9 23 4           |               |                                                              | -               |                         |                     |                    |                |        |                                  |                                      |                                         |

|             |       |                       |                    |               |                                                              |                 |                         |                     |                    |                |        |                                  |                                      |                                         |

|             |       |                       | Planner CPW Pla    |               |                                                              |                 |                         |                     |                    |                |        |                                  |                                      |                                         |

| Laye        | r 41  | Layer 6 L             | ayer 8 Layer 10    | Layer 12      | Layer 14 Layer 16 Layer 18 Layer 12 La                       | yer - Isola 370 | HR [                    |                     |                    |                |        |                                  |                                      |                                         |

| UNIT        | S: mi | il                    |                    |               | 6/1/20                                                       |                 |                         |                     |                    |                |        | Total Bo                         | ard Thickness: 62                    | .74 mil                                 |

|             |       |                       |                    |               | Differential Pairs > 50/100                                  | Digital 40/8    |                         |                     |                    |                |        |                                  |                                      |                                         |

| ayer<br>lo. | Hole  | a Span &<br>e Diamete | Description        | Layer<br>Name | Material Type                                                |                 | Dielectric<br>Thickness | Copper<br>Thickness | Trace<br>Clearance | Trace<br>Width | (Amps) | Characteristic<br>Impedance (Zo) | Edge Coupled<br>Differential (Zdiff) | Broadside Couple<br>Differential (Zdbs) |

|             |       |                       | Soldermask         |               | PSR-4000BV / CA-40BB LPI (1GHz)                              | 3.3             | 0.5                     |                     |                    |                |        |                                  |                                      |                                         |

| 1           | 8     | 4 8                   | Signal             | Тор           | Conductive                                                   |                 |                         | 2.17                | 13.2               | 4              | 0.43   | 51.96                            | 99.99                                |                                         |

|             |       |                       | Prepreg            |               | 370HR: 1080; Rc= 64% (10GHz)                                 | 3.76            | 2.8                     |                     |                    |                |        |                                  |                                      |                                         |

| 2           |       |                       | Plane              | GND           | Conductive                                                   |                 |                         | 1.4                 |                    |                |        |                                  |                                      |                                         |

|             |       |                       | Core               |               | 370HR; 1-106BC; Rc=71% (10GHz)                               | 3.6             | 2                       |                     |                    |                |        |                                  |                                      |                                         |

| 3           |       |                       | Plane              | VDD           | Conductive                                                   |                 |                         | 1.4                 |                    |                |        |                                  |                                      |                                         |

|             |       |                       | Prepreg<br>Prepreg |               | 370HR; 1080; Rc= 71% (10GHz)<br>370HR; 1080; Rc= 66% (10GHz) | 3.63<br>3.72    | 3.5<br>2.9              |                     |                    |                |        |                                  |                                      |                                         |

| 4           |       |                       | Signal             | Signal        | Conductive                                                   |                 |                         | 0.7                 | 13.2               | 5.12           | 0.23   | 50.38                            | 99.31                                |                                         |

|             |       |                       | Core               |               | 370HR: 1080/2113: Rc=56% (10GHz)                             | 3.9             | 6                       |                     |                    |                |        |                                  |                                      |                                         |

| 5           |       |                       | Plane              | GND           | Conductive                                                   |                 |                         | 1.4                 |                    |                |        |                                  |                                      |                                         |

|             |       |                       | Prepreg            |               | 370HR; 1652; Rc= 48% (10GHz)                                 | 4.09            | 5.3                     |                     |                    |                |        |                                  |                                      |                                         |