# DESIGNATINE 2018

Connect

# Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

### View our eBook library

1<mark>.007</mark>e Books

### Get signal integrity into your next product's DNA.

The most effective designers are those with a firm grasp of the essential principals of signal integrity. If you do not consider how interconnects will affect signals coming off the chips from the beginning, there's a good chance your product will not work.

This book explores six essential signal integrity principles by example, using leading-edge processes, giving you practical knowledge you'll be able to use immediately.

### THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

### **Signal Integrity by Example**

**Download Now**

i-007ebooks.com

#### JUNE 2018 • FEATURED CONTENT

# DESIGNOOT MAGAZINE

# Multi-board Design

Over the past few decades, we've seen a gradual expansion of the number of multi-board electronic devices. Products are more complex now, plain and simple. There's no way that anyone could build a car, not to mention an autonomous car, with a single PCB in 2018. For our June issue, we have a variety of features that are chock-full of multi-board design information.

- 10 Dave Wiens Discusses Multi-board Design Techniques by Andy Shaughnessy

- 20 3D Convergence of Multi-board PCB and IC Packaging Design by Bob Potock

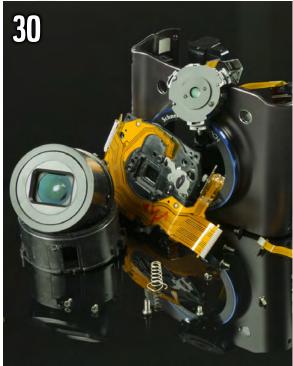

### **30** Multi-board Design with Altium's Ben jordan

by Andy Shaughnessy and Stephen Las Marias

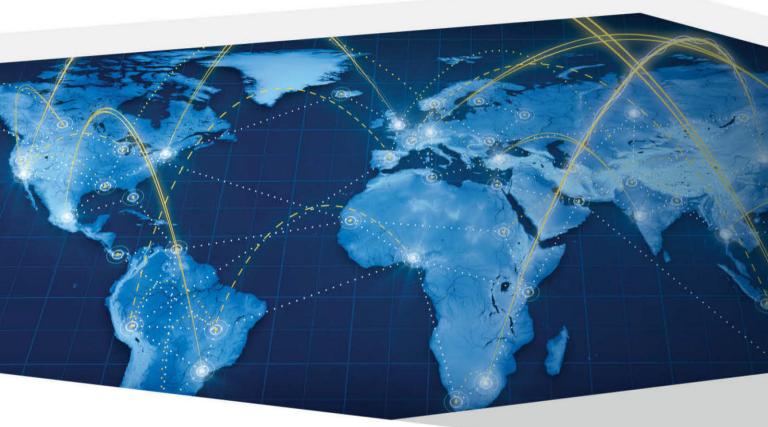

### Your signal needs to get around the world fast... Why go halfway around the world to get your high-speed PCBs?

# ACE: your high-speed experts right here at home, specializing in microwave and hybrid PCBs.

Accurate Circuit Engineering 3019 Kilson Dr Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: James Hofer (714) 227-9540

www.ace-pcb.com

RoHS & WEEE compliant • Certified AS9100, ISO, ITAR, MIL-PRF-31032 & 55110

# DESIGNOOT MAGAZINE

### **SHORTS:**

- 9 A Laser that Can Smell like a Hound

- 18 Light-bending Nano-patterns for LEDs

- 28 Turbocharge for Lithium Batteries

- 36 Robots Learn by Checking in on Team Members

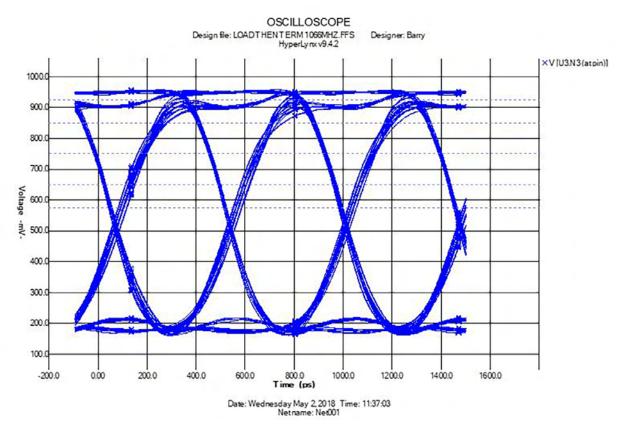

- 46 Silicon Provides Means to Control Quantum Bits for Faster Algorithms

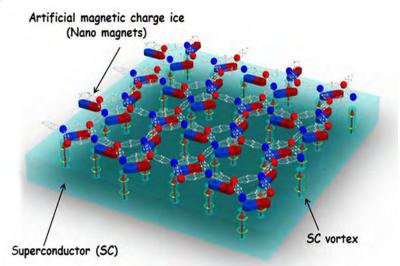

- 55 Designing a Better Superconductor with Geometric Frustration

### **ARTICLE:**

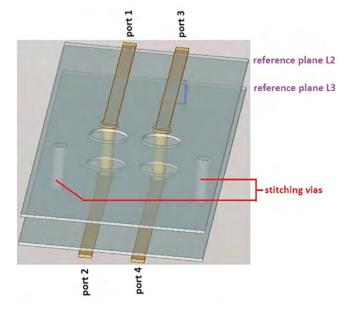

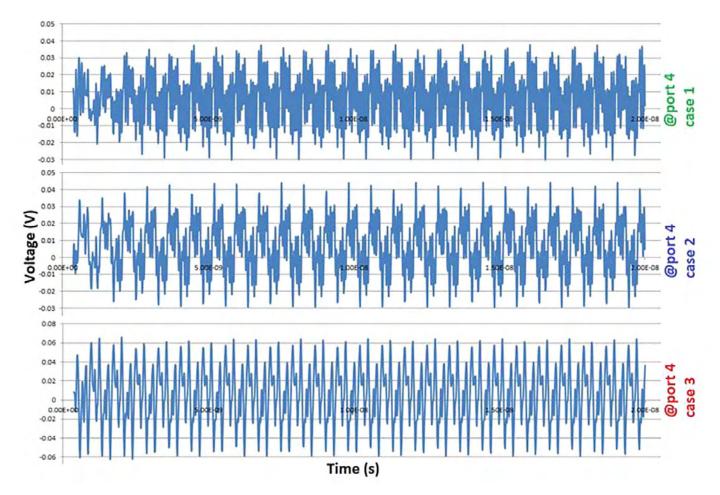

58 Achieving Optimum Signal Integrity During Layer Transition on High-Speed PCBs by Chang Fei Yee

### COLUMNS:

- 8 Multi-board Design: Multiple Challenges? by Andy Shaughnessy

- 40 DDR3/4 Fly-by Topology Termination and Routing by Barry Olney

- 48 Considerations for Comparing Material Data Sheets by John Coonrod

- 52 Thermal Management Materials: Easing the Decision-Making Process by Jade Bridges

### **HIGHLIGHTS:**

- **38** PCB007

- 56 MilAero007

- 64 Top 10 PCBDesign007

### **DEPARTMENTS:**

- 68 Career Opportunities

- 74 Events Calendar

- 75 Advertiser Index & Masthead

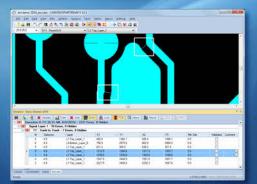

## How to Get OrCAD Capture & PCB Editor

See Ad

Pay \$430

Get OrCAD

**Design PCB**

Get OrCAD Capture & PCB Editor for Free When You Purchase a Year of Maintenance

Get OrCAD For Free

Schematic | PCB | Perpetual License | No Size Limits

### Multi-board Design: Multiple Challenges?

#### The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

If one PCB is good, aren't two or more boards even better? That is the question!

For most of the PCB's history, electronic devices contained a single circuit board. But that was back in the "olden days," and that time has passed.

Over the past few decades, we've seen a gradual expansion of the number of multiboard electronic devices. Products are more complex now, plain and simple. There's no way that anyone could build a car, not to mention an autonomous car, with a

single PCB in 2018.

Multi-board devices are here to stay. But multiboard PCB design brings with it even more challenges for the designer and design engineer. It's all about management. It reminds me of a juggler trying to keep half a dozen balls in the air.

Every aspect of the design process is different, from schematic through data hand-off. Design teams, sometimes working in different time zones or countries, must become fluent in system-level management of a variety of interconnects, and ECAD and MCAD collaboration is more critical than ever with multi-board designs.

Designers are constantly making trade-off decisions throughout the multi-board design cycle, especially regarding reliability, thermal

> management, signal integrity and power integrity. The final product's form factor weighs heavily on the design process,

and a good 3D EDA tool is a requirement for laying out multiple PCBs today.

Fortunately, most of the EDA tools of today have multi-board design capabilities, and 3D functionality plays a big role. Interconnect management, data management, concurrent design, and ECAD-MCAD co-design functions also help bring multi-board design into the mainstream.

For our June issue, we have a variety of features that are chock-full of multi-board design information. In our first interview, Dave Wiens of Mentor discusses multi-board design techniques, from a 30,000-foot view down to a nuts-and-bolts board level, including the various trade-offs that occur throughout the design cycle. Zuken's Bob Potock provides a technical article on the 3D convergence of multiboard PCB and IC packaging design, and the importance of ECAD and MCAD collaboration. Finally, we interviewed Ben Jordan of Altium, who breaks down many of the challenges related to multi-board design, and some of the techniques that can simplify complex designs. As Ben says, "It's not a complicated concept."

From our monthly contributors, we have Barry Olney of In-Circuit Design who explains DDR3 and DDR4 fly-by topology termination and routing, while John Coonrod of Rogers Corporation discusses exceptions designers might encounter when comparing material data sheets. And Jade Bridges of Electrolube shines a spotlight on the selection of thermal management materials.

To wrap things up, we have an article from Chang Fei Yee of Keysight Technologies that outlines the best methods for achieving signal integrity during layer transition in high-speed boards.

As we head into the summer, take the time to download a PDF of *Design007 Magazine* to read on the beach. We'll keep bringing you all of the design news and technical information that you need! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 18 years. He can be reached by clicking here.

### A Laser that Can Smell like a Hound

University of Adelaide researchers have created a laser that can "smell" different gases within a sample. Applications for the new device lie not just in environmental monitoring and detecting industrial contamination, but may eventually be used to diagnose disease by "smelling" the breath.

The researchers liken the ability of the laser to differentiate between different gas compounds in a sample to the sensitive nose of a bloodhound. But rather than smell, the device uses patterns of light absorption to measure the composition of the sample.

From the University's Institute for Photonics and Advanced Sensing (IPAS), the researchers report in the journal Physical Review Applied that the laser can measure the amount of carbon dioxide in a gas sample in under one second, with high accuracy and precision.

"The ability to rapidly measure gas composition to such high accuracy is cutting edge," says lead author Sarah Scholten, PhD candidate.

The device exploits a Nobel-prize winning technology, developed by US and German scientists, called an "optical frequency comb." This laser comb generates millions of different light frequencies or colours at once.

The researchers pass this special light through a sample of gas where each gas molecule absorbs a distinctive set of colours. The pattern of light absorption is a unique fingerprint of the gas composition of the sample.

"This first work aims at atmospheric monitoring, however, the technique is broadly applicable and offers an avenue for near-universal concentration measurements," says Dr. Chris Perrella, postdoctoral fellow.

### Dave Wiens Discusses Multi-board Design Techniques

#### Feature by Andy Shaughnessy I-CONNECTO07

Today, many products contain two or more PCBs, and multi-board design has become the rule rather than the exception for quite a few PCB designers. For this multi-board design issue, I recently interviewed Dave Wiens, product marketing manager for Mentor, a Siemens business. We discussed how the multi-board design technique differs from laying out single boards, along with the planning, analysis and verification processes required to design multiboard systems.

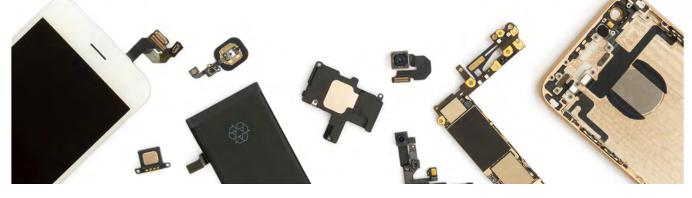

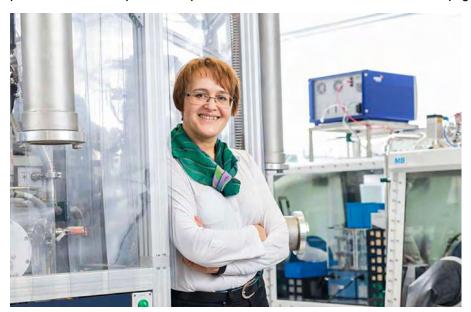

**Andy Shaughnessy:** Dave, what are some of the typical end products that might use multiple PCBs?

**Dave Wiens:** The easy answer is that almost every end-product that includes electronics is a multi-board system, even small products like your mobile phone. If you look up your phone model on iFixit, you'll see a teardown that has multiple boards. At a minimum, there'll be a separate board for the camera or for the audio or for the external connections. Those are all separate functions and, in some cases, when somebody's designing they won't necessarily design all those pieces. They might, for instance, be acquiring the camera from somebody else, and that basically represents a component. It is a complete PCB, but to them it's a component because they didn't design it. We're not necessarily talking big back planes, with tons and tons of data cards on them. Certainly, that's a multi-board system, but pretty much everything you see today is multi-board.

I don't know about you, but when something in my house stops working, I tend to tear it apart. Sometimes I'm trying to figure out if I can fix it, but often I just want to see how they designed it. Really, when you're designing something and making decisions to make it into multiple boards, you start thinking about things like size and space. Should I put this all on one board? Should I break it up into multiple boards for space reasons? Should I do it because of reliability reasons? If this data board fails, it's easier to plug

### IT'S BEEN QUITE A YEAR AT ASC.

### **Sharing our Expertise**

Everyone can tap into the decades of combined experience and expertise of our in-house experts on our recently launched ASC Experts website.

#### **Meet the ASC Experts**

#### Award-winning technology

We were recently presented with the 2017 Brilliance in Business Award for **Outstanding Design and Innovation** by the City of West Chicago.

#### Learn More

We followed our first eBook on Flex and Rigid-Flex with a guide to creating **RF/Microwave PCBs which has been** called the "RF and microwave engineer's PCB fabrication bible".

#### Download our eBooks

At ASC, we're not just building boards, we're building the future. Let's build it together!

### American Standard Circuits

Creative Innovations In Flex, Digital & Microwave Circuits

CIRCUIT DESIGNER'S CUIDE TO...

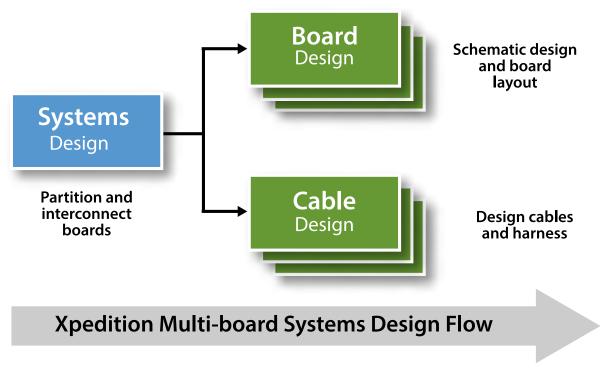

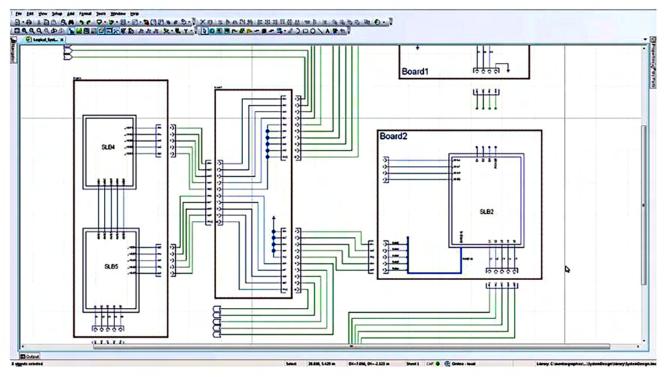

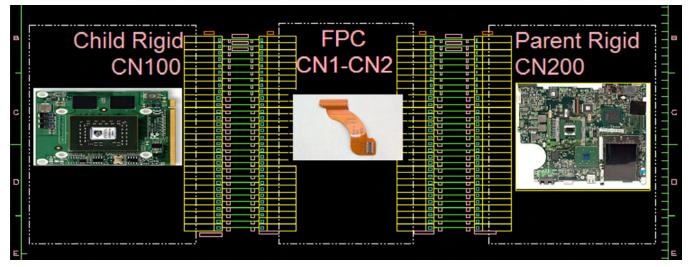

Figure 1: A fully integrated process for designing multiple PCBs and associated cables.

and play it with something else versus throwing away the whole system. Should I do it for cost reasons? Performance reasons? And then there's the make versus buy decision, right? For this function of my system, should I just buy a board and connect it to my system? Or should I design it into the system?

You see that with your home PC. It's got dedicated graphics built into it now, but you still may want to put an add-on graphics card, but those used to be things that weren't necessarily integrated into one system. They've done that over time.

**Shaughnessy:** It sounds like some of the biggest challenges are the trade-offs make. Like, should you add another board? What are some of those challenges?

**Wiens:** I'd loosely group the design challenges into four categories: managing design complexity, enabling multi-disciplinary team collaboration, optimizing product reliability, and leveraging IP across the organization. Regarding design complexity, yes, the trade-offs are a huge one and, frankly, because of that a lot of people kind of avoid it. I mean, they make decisions very early on to segment something. They take their high-level requirements, and then they start building an architecture from that. They decide what's going to be hardware, what's going to software, and how that's going to interplay with mechanical structures, cabling structures, all of that is decided way up front, and then the question is: Do they ever revisit that? If they don't revisit it, then they were either really good and they got it right up front, or as the design progressively refines itself, as the engineers refine it from that highlevel architecture down into the physical implementations, they may find things.

For instance, the architecture indicates, "I decided to put these two boards over here." But maybe they don't fit. Maybe they are too far apart for those high-speed signals from the driver on one board to the receiver on another board. There are things that you don't know at that top level that as you progressively refine you get smarter and smarter, and so you want to make those trade-offs progress through the design. If you locked and loaded your design way up front, then you've lost that alternative. That's the case of most teams. Because it's so painful to make changes after that initial archi-

tecture was decided, they don't tend to do a lot of revisiting it in the form of trade-offs, in the form of any ECOs.

When the design gets bigger, it becomes nearly impossible to use that form of collaboration, so that's an impact because of complexity. Also, because of that complexity and the density of designs, the performance of designs, you've got to think about trade-offs like form factor or performance where before maybe the box was big enough. You really didn't care what went where or you were operating down at much lower speeds, and so you didn't care about performance across boards, but as those changes happen, it becomes more critical to do design trade-offs.

Regarding the second challenge, to address complexity, teams need to be able to communicate or collaborate across multiple disciplines. I was just talking about the box, and so I'm talking about the mechanical guy and the guy doing the PCB being able to collaborate. Maybe the high-speed engineers are collaborating with the PCB guys, and so this multidiscipline collaboration needs to be managed more efficiently, again, to enable them to do those trade-offs to avoid any redundant efforts. Because a lot of times when they pass data from one person to the next, they're doing it again through some manual means, maybe email. It may be a whiteboard. There are lots of ways to do it that are very inefficient, so somebody receives that data and they basically must redundantly design whatever that person communicated and, of course, that introduces lots of fun errors.

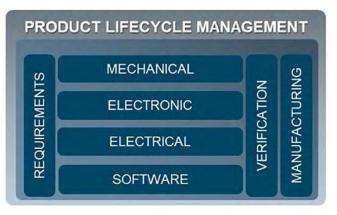

We're really trying to find ways to break down what we talked about, black box design or silo design processes. There are silos really across the spectrum. If you think about a process from left to right, on the left you've got requirements and, by the way, left to right you could think about it in terms of a V diagram, too, if you wanted. On the left, though, you've got your basic requirements. Those marketing people they come in and say, "Here's what we want to build." It has requirements, and then somebody takes those requirements and they progressively refine it down into an architecture, and then at some point it ends up as PCBs. At the back end of the left-to-right process, we at Mentor have been leveraging the Valor technology to optimize what we call the lean NPI process to handle the transfer and the collaboration between the PCB design team and the manufacturing team. There's also top to bottom, where you have the multiple disciplines. You've got hardware and inside hardware there's multiple PCBs that have packages on them, which have silicon on them, and then there is software, cabling, and maybe the networking on what's being communicated across that cabling, and the mechanical infrastructure. These are all different disciplines that, at some point, are being designed concurrently after the design has been partitioned up for those disciplines.

Those guys need to collaborate more efficiently as well, top to bottom, and we've talked in the past about things like ECAD/ MCAD collaboration, right? How do you optimize those guys working across disciplines? The same thing happens between electronics and electrical. Is it in the wiring? How do I optimize?

To put on my Siemens hat now, we talk about a continuous digital thread. The idea of a digital thread is from that initial point of requirements capture, where everything is continuously created and communicated in a digital form, eliminating any redundant efforts and optimizing the communication between steps. That's the Holy Grail.

Figure 2: Optimizing electronic systems design with a continuous digital thread from requirements through manufacturing, and across multiple domains.

The third challenge is optimizing product reliability. I'm designing this system and I've worked across the teams efficiently, but I still may not be catching all the errors, and as I build larger and larger systems the chances of designing in errors increases, and so the need for technology to validate designs throughout the process increases. Validation starts with the connectivity between the multiple boards—simple things like connector pin mismatches can cost millions to identify and redesign. It also includes system-level schematic checking and system-level modeling for signal and power integrity, thermal and mechatronic behavior.

The last challenge is leveraging the IP generated during the design process across the organization, and that partly gets into that digital thread of data passing throughout the flow, but it also says, "Hey, look. If I design a piece of circuitry, I want others to be able to reuse it." At the single board level, I've seen upwards of 80% of a design reused from one generation of a product to the next. You want to enable that efficiently, but that's not multi-board design. When it comes to multi-board, people are reusing entire boards.

"Hey, look. If I design a piece of circuitry, I want others to be able to reuse it." At the single board level, I've seen upwards of 80% of a design reused from one generation of a product to the next.

**Shaughnessy:** Well, it sounds like there's a lot going on at the very front end.

**Wiens:** Yes. It's at the front end and it's also really throughout the whole process because,

again, you want to enable that guy at the front end to make smart decisions, but you also want to enable progressive refinement with optimization. As the thing goes through and you realize, "Hey, this either won't work or it won't work as well as it could have. Hey, what changes can we make? Can we put this set of functionalities onto this board? You know, onto board A instead of board B?" Can we, in some cases, say, "I want a really, really fast connection; can I have a fiberoptic cable connection between these two boards instead of going through a whole bunch of physical connectors across back planes and things like that?"

Those are the kinds of decisions that somebody is going to sit there and try to think through, once they start seeing the physical incarnation of the board being built.

**Shaughnessy:** Speaking of the front end, I've heard of designers who want the schematic to represent multiple boards. Is a multi-board schematic that different?

Wiens: It certainly is. We certainly have had customers who started there. Most modern EDA tools have a hierarchical schematic system. That just means you have high-level blocks, you design at a high level, and then you start to poke into a block and you can see more data, and you can progressively go down multiple levels of that. Engineers naturally said, "Well, okay. So if at the top level today my high-level schematic is just one board, well, what if I go one level above that? Now, I'm looking at multiple boards." That is possible, but it gets back to the complexity of managing all that data, managing the connections, and really at that level the schematic tool is really a documentation tool, not an architecture optimization tool, if you know what I mean.

In addition, system engineers don't normally know or really use schematic capture tools. They use higher-level abstraction tools, like Visio, which is basically just a hopped-up version of PowerPoint drawing tools. I'm underselling it, but you know what I mean if you've ever used Visio. But of course, they want that high-level abstraction to transfer directly to

# VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

### **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

©2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

### Visit downstreamtech.com or call 800-535-3226

Figure 3: Connectivity defined across a multi-board system.

lower-level boards, without having to re-draw or re-design.

**Shaughnessy:** Well, it sounds like the multiboard is just one more option, really. Is it just another option in the toolbox?

**Wiens:** Yeah. I think we're talking about the same thing. In the world of EDA, the big word is automation. We try to find areas in the design process that are inefficient and optimize them and automate them as much as possible so that we improve the productivity of the overall team. That's what we're doing here.

People are designing multi-board systems today. They've just been doing it very inefficiently, and just saying, "Well, this is part of the design process. We have to suck it up." It takes longer. It produces lots of errors. It generates designs that aren't necessarily optimized, but, oh well, we don't have a better way, so we're going to keep doing it. It's kind of a new frontier for us EDA vendors to try to go after to optimize that. We're working to optimize that process from left to right. We've got technology that goes all the way back to requirements capture, and we have a lot more on the right side, too, in terms of manufacturing automation, and we're looking top to bottom, across multiple domains like ECAD, MCAD and electrical.

**Shaughnessy:** That's another thing I was wondering about. It seems like the MCAD side would be a little more involved than normally with multi-board. Is that accurate?

**Wiens:** MCAD's involvement often depends on the complexity of the enclosure the electronics are going into. If it's a simple box, with a lot of room, there's not much collaboration needed. Of course, most teams want to minimize material waste and try to optimize the enclosure. That requires close collaboration between ECAD and MCAD teams throughout the design process, not just at the beginning and end. To answer your question, regardless whether it's a single-board or multi-board system in the enclosure, the frequency of iterative collaboration depends on the complexity of the enclosure relative to the boards inside. **Shaughnessy:** Is there any difference in how you run signal integrity and EMI simulation and analysis, other than having to just do it more than one time? What do you think?

**Wiens:** I could answer that question a couple of different ways. Let's just look at a single board scenario. I'm only designing a single board system, and let's say I have an RF section on that board. Well, suddenly, I'm putting up via arrays around that section within the board. I'm putting a metal can on top of that section. I mean, you've seen an RF board, right? They look cool, like little walled cities. That's an example of EMI control on a single board. The same thing, you can imagine, happens on a multi-board scenario. One board radiates onto another, and if you've got two boards sandwiched on top of each other, there's a lot of that going on between the two. But you use the same kind of isolation approaches to optimize it.

It's the same thing with signal integrity. Signal integrity is about a signal traversing from a driver through some kind of topology to a receiver. It's easy to think about on a single board. You've got a driver on one chip that goes through a package, comes out through the pin. It goes through traces on the board, maybe through some vias, pops up somewhere else, goes back up to another chip that receives the signal. Multi-board is just an extended topology. It starts bringing in things like connectors. That's why you have companies like Molex and Samtec selling expensive connectors that are optimized for performance, because highspeed signals traverse multiple boards. You need to be able to model that connector.

Some of that gets into 3D electromagnetics to efficiently model what the connector looks like, and maybe you've got some cabling between boards. You've got to model that as well. Engineers have been able to manually model a multi-board system for quite a while – but it meant manually re-creating the topology model in a simulation environment—again breaking the digital thread and potentially introducing errors and delays. To try to automate that process, using that 'A' word in EDA, means looking at the overall topology. We extract that topology automatically into Hyper-Lynx and build all those topology models for them so that they don't have to do it all manually. That's something that we can do today in a multi-board environment.

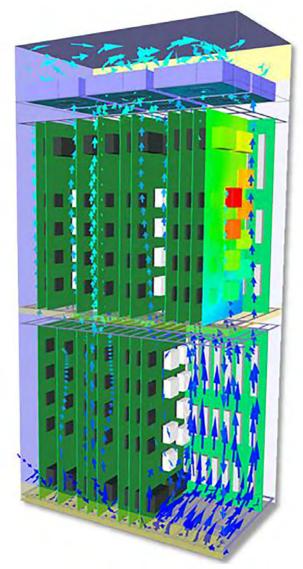

You asked about EMI and SI, and thermal is another case that's very common. We've got a technology called FloTHERM that's integrated within the flow. With FloTHERM, you can model at the chip level. You can model the chip inside a package. You can model that package on a board. You can model multiple boards inside an enclosure, and all the way up to that enclosure inside a room.

Figure 4: Virtual prototype multi-board system for mechatronic behavior, signal/power/thermal performance and manufacturability.

There are other things like schematic integrity, being able to model to do checks on schematics at the single board or multiple board level. I mean, there are just lots and lots of examples of validation that people have always thought of as a single board problem, but it naturally transfers itself up into the multiboard scenario.

**Shaughnessy:** On multi-board design, is it typically a team working on it? That seems like the best way to go, having a couple of guys working on it at the same time doing concurrent design.

**Wiens:** Yep, absolutely. There is concurrency in that left to right spectrum in the sense that you might have, say, a system engineer designing multiple blocks of multiple boards, and they may say, "Okay. I think this board is pretty much locked down. Hey, you PCB design engineers. You can start working on the schematic for this one board." After those guys have started laying down the schematic, they can hand it off to the layout guy who can start doing basic layout. This is all happening concurrently, right? It's no longer a serial process, and then the big thing is if a change is needed, if an ECO is required, initiated from one side or the other, how efficiently does it pass from one person to the next?

So that's concurrency in what was traditionally a serial process from one discipline to the next, but we've also enabled concurrency within disciplines. We started with layout concurrency more than a decade ago. We've since added concurrency to the rest of the core flow of things like the schematic, so design engineers can work concurrently. They can enter constraints concurrently. They can layout concurrently. They can simulate concurrently. Then, for multi-board we added the capability for multiple system engineers to collaborate concurrently in designing that architecture as well. It's really concurrency across multiple disciplines.

**Shaughnessy:** It's been great talking to you, Dave. Thanks for your time.

Wiens: Thank you, Andy. DESIGN007

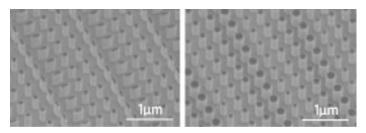

### **Light-bending Nano-patterns for LEDs**

Nanoscale patterns designed to bend, deflect and split light can now be fabricated directly on light-emitting diode (LED) surfaces using an innovative etching method

"We have demonstrated that metasurface -surfaces patterned with features typically smaller than the wavelength of emitted light-can be fabricated directly on a stan-

developed by A\*STAR researchers. A new fabrication scheme creates new possibilities for the facile control of light output.

The light-emitting component of LEDs is a surprisingly simple structure, typically a thin layer of a dielectric material such as gallium nitride (GaN) on a crystalline sapphire substrate.

Egor Khaidarov and colleagues from A\*STAR's Data Storage Institute and Nanyang Technological University have now found a way to pattern GaN with nanoscale features that can control the behavior of light. dard GaN-on-sapphire platform," says Khaidarov.

Metasurface modifications of LEDs have been attempted in the past. These included patterning an additional layer with a very different refractive index than the underlying GaN-on-sapphire substrate to keep the light in the metasurface layer and enhance the light-matter interactions.

The resulting design, however, posed a major challenge for fabrication, requiring the team to develop a precise nanofabrication procedure involving electron beam lithography and fast, high-temperature reactive ion etching.

### FREE BUT PRICELESS SERVICES FOR YOUR PCB FABRICATION

We are a China-based custom PCB fabrication service provider with over 10 years' experience. Except for full feature manufacturing capabilities, we also have multiple free but priceless services to ensure you get superior PCBs within budget!

- Instant Online Quotation

- Advice on Cost Reduction

- Panelization

- Custom Layer Stackup

- Valor DFM Check

- Custom Electrical Test

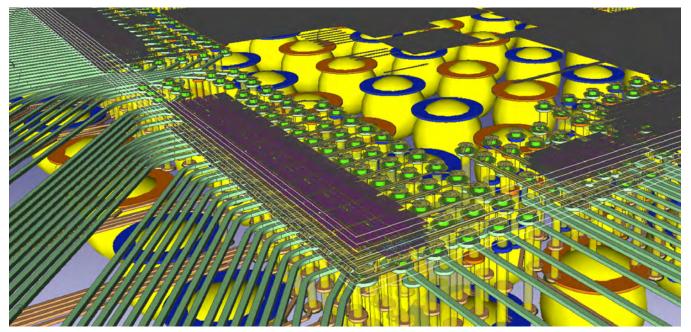

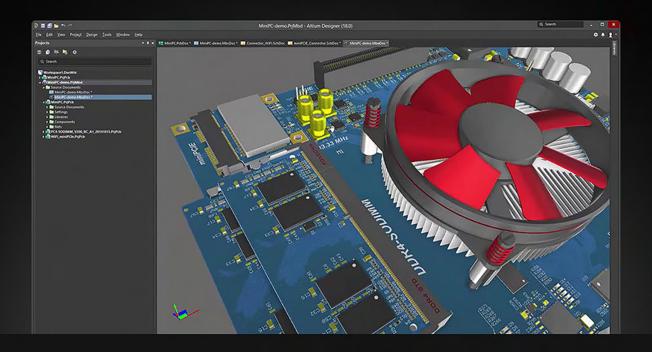

### **3D Convergence** of Multi-board PCB and IC Packaging Design

#### Feature by Bob Potock ZUKEN USA

The electronic product design process is being challenged like never before, with the need to develop feature-rich, light, compact products at a lower cost, in less time. To address these challenges, designers are combining chips and boards in new configurations, such as complex 3D stacked structures, or new packaging technologies like package-on-package (PoP) and system-in-package (SiP). They are also embedding passive and active components on inner layers, inside cavities and within the dielectric of the board stack-up.

Traditional 2D PCB design systems are used to design one PCB at a time in isolation from the other PCBs within a product, and also in isolation from the ICs, packages, and enclosure. Validating connections between the PCBs, collision checking the boards to the enclosure, and reducing interconnection distance to the ICs requires time-consuming manual operations that are error-prone and limit the potential for reuse.

A new generation of 3D multi-board productlevel design tools offer major improvements by managing multi-board placement in both 2D and 3D, and enabling co-design of the chip, package and board in a single environment. Multi-board design makes it possible to create and validate a design with any combination of system-on-chips (SOCs), packages, and PCBs as a complete system. Chip-package-board codesign enables designers to optimize routability via pin assignment and I/O placement to minimize layer counts between the package, chip and board. The new design methodology makes it possible to deliver more functional, higher performing and less expensive products to market in less time.

### **Multi-board Design Challenges**

Today's complex multi-board electronic products create design challenges, such as planning and management of interconnects at Flexible, reliable Supply<br/>Chain Solutionshigh quality copper clad<br/>laminates & prepreg<br/>bonding materials

Ventec International Group is a world leader in the production of high quality and high performance copper clad laminates and prepregs, with full R&D and product development capabilities. Our global distribution means we can readily supply our products to all markets in all geographic areas.

Get your free copy of The Printed Circuit Designer's Guide to...Thermal Management with Insulated Metal Substrates.

DOWNLOAD NOW

### Ventec - wherever technology takes you, we deliver

#### Ventec International Group

ventec

INTERNATIONAL GROUP

**螣**輝雷子

179 Ward Hill Ave, Ward Hill, MA 01835, United States T: 978-521-9700 E: ordersCA@ventec-usa.com Y Follow @VentecLaminates

www.venteclaminates.com

the system level. In current-generation tools, the signal verification process for a multi-board design involves exporting pin lists that include net names for each board connector and correlating the net names to the master list of net names. In many cases, it's also necessary to manually verify each board connector's signal name. With mechanical engineers and board designers working with disconnected systems it's difficult, if not impossible, to intelligently manage connectivity and changes between boards. Using a spreadsheet or some other disconnected document to manage the large number of interconnects between the PCBs in the system is time-consuming and prone to error.

When mechanical engineers have inaccurate information on the electrical design or electrical engineers have inaccurate information on the mechanical design, the result in many cases is that batteries don't fit, mounting screws create shorts against PCBs, and connectors don't mate with packaging openings. Improper management can easily result in wasted product development time, scrapped boards and slipped schedules.

The combination of increasing capabilities, shrinking size and more complex external shapes means that electronics must increasingly consider the shape of the package while the mechanical design is more dependent than ever on the physical aspects of the internal electronics. Multi-board designs make ECAD- to-MCAD translation more difficult because of the need to communicate the position of connectors and other common points between the boards.

Yet in the current generation of tools, the collision-checking process involves exporting placement information, usually in IDF format, for each PCB to a mechanical engineer for assembly analysis. PCB design tools have continued to focus on working in 2D on one PCB at a time, with the electrical work done in 2D and then the 2D design being exported into 3D mechanical design software where the boards are positioned and checked for interference. The PCB designer is unable to, for example, position two boards on top of each other to see how they fit together. This is normally done after the board design has been exported to the mechanical design tool. Interdependencies between interlocking boards and their enclosure in complex products are critical.

The limitation of this approach is that if a problem such as an interference is identified, it's necessary to go back and forth between two different environments—PCB and mechanical design—to try and solve it. The other option is for a PCB designer to use a non-native viewer to conduct their own analysis. It is estimated that 50% of complex products require at least one additional PCB fabrication to address electro-mechanical issues. It is also very awkward to perform a high-level design study, such as

Figure 2: Today's products are competing on style, size, weight, cost, and function. A product-centric design process should be optimized for competitive factors.

### "Wow, APCT Global Handles Everything!"

Complete Custom Program Management Solutions

### A Leading Manufacturer of High Reliability Printed Circuit Boards

APCT Global provides their customers an opportunity to take advantage of the savings associated with global manufacturing without the costs or risk associated with: Qualifying a Supplier, Transferring Proven Design Recipes, Engineering Questions or Quality Concerns, Potential Language Barriers & Logistics Issues, Multiple Time Zones & Exchange Rates and Inventory Management. APCT Global eliminates all the headaches, delays and logistic challenges that comes with managing global procurement.

### Contact Us Today and Let Us Build You A Solution!

APCT, "Where Our People Differentiate Us From The Competition"

evaluating whether a two-board or three-board design is best, and which blocks should be allocated to which board.

### **3D Design Challenges**

To compensate for increasing silicon costs, new packaging technologies have emerged to pack ICs more closely together. PoP structures are being used to connect logic and RAM ICs. SiP integration is being used to integrate multiple chips into a single package. And 3D-IC technology using through-silicon vias (TSV) is being used to reduce interconnect distance in stacked chip configurations. Meanwhile, PCB technology has evolved over the years with high density interconnect PCBs, high density packaging, embedded components and advanced I/O technology.

The greater complexity of these new packaging configurations is creating major challenges for packaging designers as well as for the PCB and IC designers who must integrate the package into their own work. Traditionally, the PCB, the IC and the package are each designed in their own stand-alone 2D environment. PCB design software has been enhanced to address technology advancements with improvements in routing, constraint management, and signal and power integrity analysis. But these improvements have largely been limited in scope to the PCB design process.

With increasing functionality, tighter cost constraints, and the decreasing form factor of today's products, such as portables, wearables and the Internet of Things (IoT), components need to be tightly coordinated with each other so that pin assignments can be optimized for small size and minimum layer count substrates. The overall goal is to align the board, package and chip so that each signal follows the shortest possible path from the chip to the board, resulting in the fewest possible layers in the package. With the lack of tool integration, but increasing design requirements, engineers have reverted to workarounds such as using spreadsheets and generic office productivity tools to perform planning and feasibility studies, and to define the tool interfaces and data transfer.

### **3D Design Tools Address Multi-board Design**

A new generation of 3D multi-board, chippackage-board co-design tools addresses these challenges by providing an environment for system design that integrates 2D and 3D multiboard design along with the chip and package. Designers can manage all of the boards in the system in a single view to define the connec-

tions between them and then highlight the signal across each entity and analyze the entire interconnect length. The number, size, type and configuration

> Figure 3: A product-level multi-board schematic.

Electrical system

main\_board

nical system

Case\_Assy(Case\_Assy(1)

Digital\_Camera

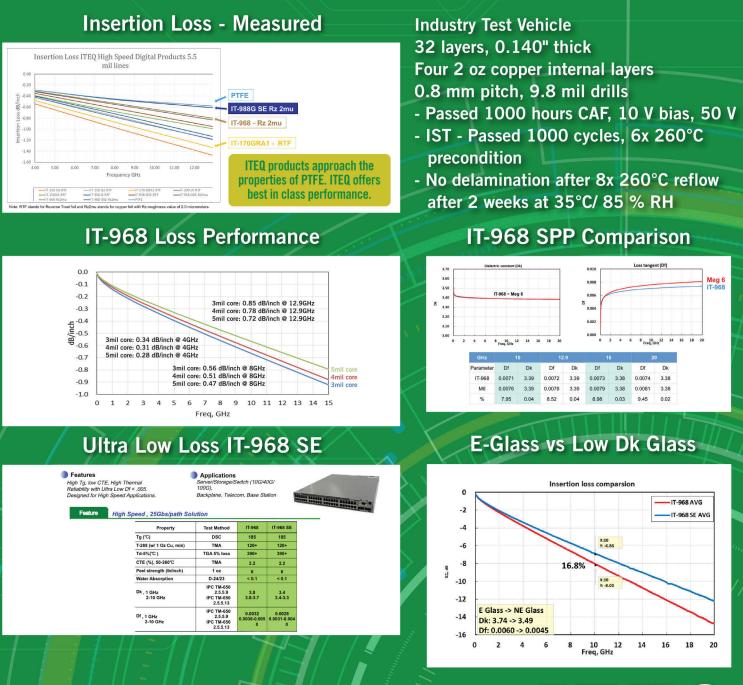

# IT-968 / IT-968 SE

High Thermal Reliability Designed for High Speed Digital Applications - Telecom, Backplane, Base Station, Server, Storage, Switch IT-968 Dk @ 10 GHz - 3.66 Df @ 10 GHz - 0.005 IT-968 SE Dk @ 10 GHz - 3.16 Df @ 10 GHz - 0.0037

of PCBs, along with alternative allocations of

functions across them, can be evaluated collaboratively with the ability to make trade-offs. Functional blocks can be assigned and moved between boards and boards can be reshaped, added and subtracted as necessary. The 3D multi-board design tool can address signal continuity at the system level while simultaneously managing multiple PCB interconnects and understanding board-to-board signal continuity.

PCB designers gain the ability to import the mechanical enclosure directly into the ECAD tool, so they can get single or multi-board designs right the first time. 3D parametric libraries are shared between the ECAD and MCAD systems. During layout, users invoke a wizard to import the 3D enclosure model and specify all the associated PCBs. They then layout the PCBs with the enclosure in real-time, optimizing placement capacity and capturing interference violations earlier in the design process.

Figure 4: 3D collision checking in a native ECAD tool.

Electrical engineers can design to the true native 3D constraints as defined by mechanical engineers while mechanical engineers in turn have access to the true 3D board design, so they can accurately conduct interference checks during board layout. Electrical engineers can design multiple boards within a single model to ensure precise positioning of angles, shapes and cuts needed to avoid interference. Working with the exact product shape makes it possible, for example, to fit more functionality into a package that is curved to conform to interior styling than could be accomplished with an orthogonal approximation. 3D ECAD design enables more accurate alignment of connectors so that they precisely fit openings on the enclosures.

### Chip-Package-Board Co-Design

By integrating planning and final design for PCBs, packages and ICs in a single view, the newest generation of tools makes it possible for engineers to conduct system-level codesign of the PCB, package and chip and optimize I/O placement, pin assignments, redistribution layer (RDL) routing, and bump and ball placements. The benefits are particularly great when working with non-traditional structures with routing complexity in both vertical directions such as PoP, SiP, chip-scale packaging and 3D-IC/3D packaging. The new tools also automate routing of the chip RDL and package escape, reducing pathfinding cycle time and making it possible to optimize die bump placement. The new approach makes it possible to study the trade-offs involved in using different numbers of package layers while simultaneously considering RDL routing on the IC side and the escape route on the PCB side in a single design view. Advantages of the new approach include lower RDL, interposer/substrate and package layer count, improved signal integrity and faster time-to-market.

Each person working on the project can see their piece of the puzzle in the context of the full product, making it easier to optimize pin assignments and avoid connectivity errors. For example, package/IC bump assignment can be performed while viewing the effects on the rats nest at the PCB level. The designer can observe the potential impact at the package and IC level of making automatic or interactive pin swaps at the board level to improve PCB routability. The pin swap operation is automatically communicated between the package and PCB databases, eliminating the need for CSV or other neutral files to communicate the change. Multiple engineers can work simultaneously on a single substrate because the tool enables engineers to lock the package design. If a designer needs to make a pin swap in a locked package design, they can send a notification that the other engineers can accept or reject as an ECO.

#### Simulation

The effects of changes from a signal integrity, power integrity or thermal point of view can be determined by performing multidiscipline, multi-physics analysis with solutions from providers such as Keysight Technologies, ANSYS, AWR, CST and Synopsys. The co-design environment enables signal traceability across the complete system. Signal paths can be reviewed and analyzed as they cross design and component boundaries from drivers through the system interconnect to receivers. Intelligent and integrated schematic- or layout-based simulation environments support multiple design flows.

### Conclusion

The move from coplanar designs to complex 3D stacked structures and embedded devices is driving the need for tools that can accurately render and provide meaningful visual and DRC feedback to enable, rapid right-the-first-time

Figure 5: Co-design environment for chip, package, and board in 3D.

designs. The new generation of 3D multi-board product-level design tools enable real-time 3D hierarchical design, allowing design teams to concurrently create any combination of advanced stack dies, packages and PCBs. With a native 2D and 3D architecture, designers can effectively co-design a chip, package and board to optimize I/Os at each level, embed components in the dielectric of a stack-up intelligently, and verify manufacturing rules in real-time. Next-generation tools manage multiple boards and their associated enclosures simultaneously and provide collision checking directly in the native ECAD tool. The new integrated 3D multi-board chip-packageboard co-design environment makes it possible to holistically optimize the package, board and IC design to a greater degree than was possible in the past with the end result being higher performance and lower manufacturing costs. **DESIGN007**

**Bob Potock** is vice president of marketing for Zuken USA.

### **Turbocharge for Lithium Batteries**

A team of material researchers from Jülich, Munich, and Prague has succeeded in producing a composite material that is particularly suited for electrodes in lithium batteries. The nanocomposite material might help to significantly increase the storage capacity and lifetime of batteries as well as their charging speed. The researchers have published their findings in the journal Advanced Functional Materials.

Lithium-ion batteries are the ultimate benchmark when it comes to mobile phones, tablet devices, and electric cars. Their storage capacity and power density are far superior to other rechargeable battery systems. Despite all the progress that has been made, however, smartphone batteries only last a day and electric cars need hours to be recharged. Scientists are therefore working on ways to improve the power densities and charging rates of all-round batteries. "An important factor is the anode material," explains Dina Fattakhova-Rohlfing from the Institute of Energy and Climate Research (IEK-1).

One way of addressing this problem is hybrid materials or nanocomposites - composite materials that contain nanoparticles. The scientists developed a material comprising tin oxide nanoparticles enriched with antimony, on a base layer of graphene. The graphene basis aids the structural stability and conductivity of the material. The tin oxide particles are less than three nanometres in size - in other words less than three millionths of a millimetre - and are directly "grown" on the graphene. The small size

of the particle and its good contact with the graphene layer also improves its tolerance to volume changes - the lithium cell becomes more stable and lasts longer.

"The nanocomposite anodes can be produced in an easy and cost-effective way. And the applied concepts can also be used for the design of other anode materials for lithium-ion batteries," explains Fattakhova-Rohlfing. "We hope that our development will pave the way for lithium-ion batteries with a significantly increased energy density and very short charging time."

### 2018 Programs

June 4 Boston, MA, USA

ITI and IPC Conference on Emerging & Critical Environmental Product Requirements

June 4–5 Nuremberg, Germany

Automotive Electronics Reliability Forum

June 5–6 Glasgow, UK

**IPC PERM International Meeting No. 36**

**June 6** Chicago Area, IL, USA

ITI and IPC Conference on Emerging & Critical Environmental Product Requirements

**June 7** Frankfurt, Germany

Automotive Executives Roundtable

June 8 Silicon Valley, CA, USA

ITI and IPC Conference on Emerging & Critical Environmental Product Requirements September 13 Des Plaines, IL, USA

**IPC E-Textiles 2018**

October 13–19 Rosemont, IL, USA

IPC Fall Standards Development Committee Meetings co-located with SMTA International

November 13–15 Schaumburg (Chicago), IL, USA

IPC/SMTA High-Reliability Cleaning and Conformal Coating Conference

**December 5-7** Shenzhen, China

HKPCA International Printed Circuit & IPC APEX South China Fair

January 26-31, 2019 San Diego, CA, USA

**IPC APEX EXPO**

#### WISDOM WEDNESDAY WEBINARS — Exclusive for Members

June 13 Ju July 11 Au July 25 Au

June 27 August 8 August 22 September 12 September 26 October 10 October 24 Der November 14 November 28

December 12

For more information, visit www.IPC.org/events

### Multi-board Design with Altium's Ben Jordan

#### Feature Interview by Andy Shaughnessy and Stephen Las Marias I-CONNECTO07

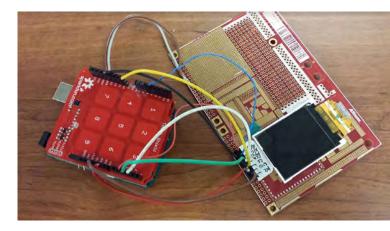

Not too long ago, historically speaking, most electronic products contained only one PCB. But multi-board designs have become almost ubiquitous over the past decade, and EDA software companies are working to improve and simplify the multi-board design process. For this issue of *Design007 Magazine*, Editors Andy Shaughnessy and Stephen Las Marias spoke with Ben Jordan, director of product and persona marketing for Altium, about the company's multi-board design tools, the challenges that customers face, and the numerous tradeoffs that designers must contend with while performing multi-board design.

**Andy Shaughnessy:** Ben, why don't you begin by telling us about multi-board design and multi-board EDA tools.

**Ben Jordan:** Multi-board design is, from my and Altium's point of view, simply the chal-

lenge of designing systems where there is more than one printed circuit board. It's not a complicated concept, and many of Altium's engineers and product managers have come from a background of designing new electronics. We even had

Ben Jordan

our own internal hardware team for some time, doing the FPGA development boards. So we had some pretty high-end designers, people like Dave Jones, who runs the EEV blog now, and some of his colleagues back in Australia. We also had the team in Shanghai for a while doing IoT modular design. This all ended up being multi-board systems design.

One reason engineering firms do multi-board designs is to divide and conquer. We want to partition a bigger product into smaller modules to make the task of designing those modules and testing those modules as individual clusters of functions that sort of make sense

Worldwide Provider of Flexible Circuits & Printed Circuit Boards

### **Unwavering Commitment**

We put the customer first by listening to their needs, allowing our team to maximize accuracy and consistently deliver high quality products.

With our on time delivery record of 94.96%, you can expect your product to be delivered on time and to your standards, making us the best choice in the industry. **Contact us** today for a consultation.

tramontocircuits.com

info@tramontocircuits.com

1.877.777.1977

together. You have the upside of being able to properly test and measure, and control supply chain issues, and design for fabrication and assembly if you have the ability of breaking up a large, complex product into small replaceable units.

This is not just for electronics; this is not a new concept. It's done in every other industry. We know that just about every professional PCB designer at some point is going to be designing a board, if they are not already, that's just one board in a larger system, and they may be involved in designing a larger system and integrating those modules. It makes sense that a mainstream professional development tool should have multi-board capabilities and shouldn't be considered a high-end feature.

It took a while because it required a new 3D modeling engine for doing 3D properly and efficiently; bringing multiple large complex PCB designs into a single editor work-space requires a lot of memory and computing power, otherwise the whole thing becomes unusable. So that was a big challenge for us, and it took some time, but we've finally been able to release that for Altium Designer 18.

We took the company into IoT experimentation in Shanghai. We've implemented stampbased form-factor modules, and we were doing our FPGA development boards, the NanoBoard NB1, the NanoBoard 2, and NanoBoard 3000, which were all multi-board modular systems that could reconfigure the platform. We encountered all the challenges that people have with manufacturing boards of different layer stacks, but how do you optimize that? Is there a way the tools can offer you a way of analyzing and checking layer stack compatibility, so you can consolidate and make the best use of panel space fabrication?

**Shaughnessy:** What are some of the challenges designers typically face in multi-board design?

**Jordan:** One that is a real pain in the derriere is connectivity management.

Connectivity management is a big piece of the problem, because it's so common for a component library in the CAD tool to look at the 3D model and the footprint (or decal or pattern, depending on what CAD tool you come from) with the mating face top down. The footprint for the connectors that you are using traditionally has them all numbered starting at the top left, anti-clockwise. In other words, you have a plug and you have a socket, and when the receptacle is reversed on the bottom side of one of the modules, because it's got it sandwiched down on the baseboard, your pin numbering is mirrored, and it's a problem. These cause headaches with managing pinouts. Then there's the other side of it where you want to be able to swap some things around to optimize the layout and routing on one of the modules,

and you need to be able to propagate changes like that throughout the broader system. So, connectivity management should be a part of pin-swapping as well.

Looking into the future, we've solved the basic pin assignments, connectivity management, and synchronization of pin swaps on the schematic side. What we have not yet done, but it's on our road map, is model the cables. There's a multi-board assembly and there's cable connectivity between them. Maybe a single wire or a multi-point cable or a harness. We don't compete with the MCAD tools which do a fabulous job of modeling cable harness assemblies, and it's not in our plan to try to do what they do; SolidWorks Electrical is fantastic. But the goal is to model wire and cable to a level where a PCB designer can actually make sure they are specifying the basics of it, saying this goes to here and here and joins these boards together, and it has to sit in this kind of envelope in 3D, and it's got these connections, and these signals travel through it, and we can swap pins again.

There's a lot more we could do in this space, in this domain with problem solving, I think. We haven't done anything with power integrity or signal integrity, for example. But that is definitely something that has to be considered with multi-board design. Speaking of power integrity, it's very easy to forget that you have one PCB and if you test that one PCB, it will pass EMI requirements in isolation. You make that a part of a multi-board system where there are signals going across connectors and return paths may be forced around the design through power cables in strange ways, if you can't design your connectivity right.

Individual modules may well pass for FCC regulations or CE regulations, and then completely fail once you integrate the whole system together as a multi-board assembly. So, these are the kinds of issues we have to think about.

**Shaughnessy:** One of challenges that designers talk about with multi-board design is virtual prototyping. What's your take on multi-board virtual prototyping?

**Jordan:** That's kind of a buzz phrase in our industry. The first time I read that was in marketing about three years ago, and it was always related to simulation. But simulation has been around for a long time. Let's call it virtual prototyping today. Maybe it's a little more than that. It's simulating the whole system, and that's really actually very difficult to do. I think on the engineering side, people have been talking about simulation-based design. That's something that MathWorks would talk about with MATLAB and maybe PTC with Mathcad and some of those analysis simulation tools that take a high level programming language. I think there are opportunities for us to integrate that more into the front-end design process. But as a basic starting point, we really do need to consider modeling power integrity.

We do have tools for simulation in Altium Designer. We've had that for a long time, so you can do mixed analog and digital simulation from our regular PCB design schematic editor. It supports Spice 3F5, PSpice models, and Digital SimCode. You can do mixed-mode analysis for actual functional prototyping. Not many people know too much about those features or use them regularly, but the engineers know about it. Front-end engineers use it in small ways if they are designing a new circuit they'll simulate. Most of the time they don't bother, because they're using circuit design principles they have been using for a while, and they know it's good. Or they're just following the data sheet for a chip and hooking it up the way the application note says, and they've prototyped it on the bench and it works.

I could foresee that in the future, we should extend that capability to do DC Power Delivery network analysis across multiple boards and through connectors. That will take a fair bit of work and take us some time, and I'm not promising that that's what we are going to do, but I could foresee that we would endeavor to do that because power supplies in a multiboard assembly are critical. Sending power and having ground returns appropriately assigned to pins on connectors in multi-board assemblies is critical to even the AC function of the design.

**Shaughnessy:** How do designers figure out the cutoff, or the break-even point, for going the multi-board route? It seems like there would be a lot of trade-offs.

**Jordan:** Has anyone ever tried to draw a Venn diagram with all of the trade-offs with PCBs? I think it's impossible. You'd have so many bubbles and some of them would never overlap, so you couldn't actually find that happy medium. At the same time, I can understand why a tool you have developed for yourself would work, but also be complex. I think there's promise there. If one can make some assumptions about the kind of product that you're designing or what its target industry or position is, in the broader system, then there are certain lists of assumptions can be made about some of those trade-offs; and that can simplify the decision making.

**Shaughnessy:** So, how would you sum up what we've discussed regarding multi-board design?

**Jordan:** There are really three elements to this. One is design for proper function and that involves the latest in signal integrity, power integrity, pin assignments on connectors, and making sure you have proper return path designs so that you don't get electromagnetic radiation problems. Coupled with that, we as an industry still need to solve that problem of making sure everything works together as an integrated bundle of boards versus just the individual modules.

The second thing is the 3D assembly and making sure all the parts fit, and that's associated with the bill of materials as well. Design for assembly is an exponentially more complex thing when you're dealing with multi-board systems, because you've got to assemble the individual parts but also the overall system, and I think our industry could improve or augment our existing DFA practices. I think IPC could help with this to define DFA guidelines for multi-board assemblies so that contract manufacturers can do final module integration and test—design for excellence, basically.

And the third thing is integration of the design practice into the broader organization. PCB design is so complex that it's very easy to fall into the fissure of that narrow space of only considering the boards; it's very important to consider the broader implications: We're designing a multi-board system, and it's part

# ROG breaks FR-4 barrier!

#### **Need Better RF Performance? FR-4 No More!**

Demand for wireless data is growing exponentially, driving a need for substantially higher levels of mobile network capacity and performance. This demand will grow further in support of the upcoming 5G IoT ecosystem where

billions of devices will be communicating with each other, and connectivity is immediate and uninterrupted. FR-4 was historically a material choice for many less demanding RF applications, but changes in the wireless infrastructure related to growing performance requirements, especially in small cells and carrier-grade WiFi/Licensed Assisted Access (LAA), have resulted in instances where the properties of FR-4 are lacking, and RF performance and consistency is compromised. There's no longer a need to sacrifice your PCB performance.

#### — Now There's Kappa™ 438 Laminates.

Introducing Kappa<sup>w</sup> 438 Laminates

Wireless circuit designers can enjoy a true breakthrough with Kappa 438 laminates because they feature the performance of "mid-tier" circuit materials and they shatter the performance limits of FR-4, but at affordable prices. Kappa 438 laminates have low loss, excellent Dk tolerance, and tight thickness control and are engineered for outstanding, repeatable wireless performance.

By having similar Dk to FR-4, your design transition to Kappa 438 laminates will be effortless! Visit **www.rogerscorp.com/kappa** to learn more.

| LUE | <b>TYPICAL VALU</b> | PROPERTY |

|-----|---------------------|----------|

|     | 4.38                | Dk*      |

|     | 0.005               | Df       |

|     |                     | Df       |

Method at 2.5 GHz

Advanced Connectivity Solutions

of an overall mechanical assembly or product. We need to be able to document things property for final assembly, and being able to modify individual modules, because this is something that we tend to do now, really. You can move components on modules to interface correctly module-to-module, but you can also do it with the broader enclosure. And that's just really a starting point, but this affects the overall mechanical assembly and that has implications for PLM systems, enterprise resource planning, and production for the broader product; also, in the electronics assembly, there may be contract manufacturer's implications, mechanically. I consider things like custom plates that have to be milled to cover certain areas of the board as it's going through soldering processes, for selective conformal coatings or selective soldering, or these kinds of things. These are all issues.

**Stephen Las Marias:** In our experts' meetings, we often hear about the importance of fabricators and EMS companies talking to designers. It seems like communication would be even more important with multi-board designs.

Jordan: Yes. I have one great example of a

power supply factory that a colleague visited, that was showing us that they were designing PC power supplies. They make hundreds of thousands of these things. And they redesigned the whole PCB just to be able to move one mounting screw and mounting hole half an inch, because it affected the assembly process, and they wanted the factory workers, or robots, to be able to screw the screw in at 90 degrees to the board instead of with a slight angle on the screwdriver.

It's sometimes impossible for the PCB designer to be aware of all the potential issues of assembly, and it has a profound impact on the industry. Having a closed loop from the CM back to the designer is absolutely necessary for improving efficiencies, and it's worth spending an extra day on design if it cumulatively saves many weeks of human labor down the line.

**Shaughnessy:** Well, is there anything we might have missed?

**Jordan:** I'm satisfied that we've covered the main boulders.

Shaughnessy: Thanks for your time, Ben. DESIGN007

### **Robots Learn by Checking in on Team Members**

The software and hardware needed to coordinate a team of unmanned aerial vehicles (UAVs) that can communicate and work toward a common goal have recently been developed by KAUST researchers.

"Giving UAVs more autonomy makes them an even more valuable resource," says Mohamed Abdelkader, who worked on the project under the guidance of Jeff Shamma. "Monitoring the progress of a drone sent out on a specific task is far easier than remote-piloting one yourself. A

team of drones that can communicate among themselves provides a tool that could be used widely, for example, to improve security or capture images simultaneously over a large area."

Abdelkader and the team quickly dismissed the idea of having a central base station that the drones would communicate with. Instead, they custom-built UAVs and incorporated a light weight, low-power computing and wi-fi module on each one so that they could talk to each other during flight.

"Each of our drones makes its own plan based on a forecast of optimistic views of their teammates' actions and pessimistic views of the opponent's actions," explains Abdelkader.

Their algorithm worked well in both indoor and outdoor arenas under different attack scenarios. Abdelkader hopes their software, which is now available as open-source, will provide the test-bed for multiple applications.

## Engineering And Providing Balanced Interconnect Solutions

nechanical environmental

electrical cost

Miraco, Inc. Manchester, NH miracoinc.com 603-665-9449

...connecting technology

SOLUTION

## Unimicron Germany Rises from the Ashes with New Smart Factory >

This is a review of the grand opening of Unimicron's new smart factory in Geldern, Germany. A fire in a PCB shop is an experience we all dread, but still it happens, and the consequences can be devastating. In the early hours of December 28, 2016, the innerlayer production plant at RUWEL International in Geldern caught fire and the whole factory and its contents were destroyed.

## Chin-Poon PCB Plant Fire to Affect 15% of Revenues ►

Chin-Poon Industrial, which has more than 70% of its revenues from the automotive electronics industry, has estimated that losses resulting from a deadly fire at its production site in Taoyuan, Northern Taiwan on the evening of April 28 will amount to about NT\$300 million (\$10.2 million).

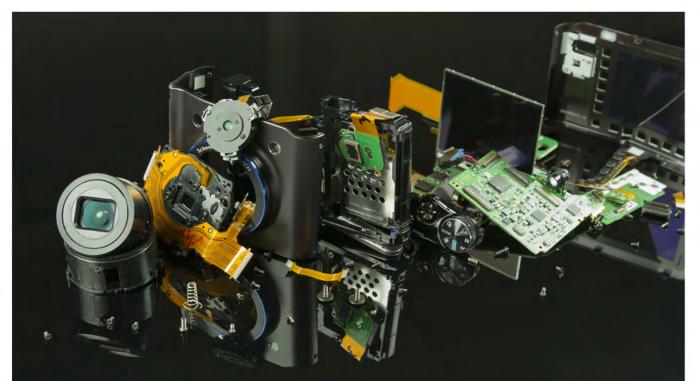

#### Flex Talk: Something New for Everyone >

Whether you are new to single- and doublesided flex, moving into rigid-flex construction, thinking of using bookbinder technology, or investigating an additive process, working with new technology can be both exciting and challenging.

## AT&S Offers a Look into the Future of Connection Technology >

AT&S presented innovative technologies and trends in connection solutions at the 14th AT&S Technology Forum. Numerous interested customers were able to find out about the latest developments in the electronics and printed circuit board industry for areas such as mobile devices, automotive, industrial, communications and medical technology and to exchange views with the AT&S experts.

#### Printed Circuits Upgrades Photo Department ►

Flex and rigid-flex circuit board manufacturer Printed Circuits has added two new pieces of equipment to their photo department including a new Orbotech Paragon 8-watt laser direct imager and a Fusion 22 automatic optical inspection machine with laser via inspection capabilities.

#### It's Only Common Sense: Silence is Not Always Golden ►

A few years ago, I worked with a client that won and then lost 30 customers all in the span of 10 months. They had bought the customer base of a company that was going out of business.

## The Right Approach: the Rebirth of Made in America ►

I have been on the record for the past 10 years saying that jobs we lost overseas may move out of China to a new low-cost country, but they were never coming back. I have never been happier to be wrong! I talk to a lot of CEOs, and the first question I ask is, "How's business?" The answers are overwhelmingly positive, and it is clear that their optimism is at a level not seen for over a decade. America as a low-cost country. Think about that.

#### Nano Dimension Sells Three Printers, Opens Customer Center at U.S. HQ >

Nano Dimension Ltd. has announced new sales of the DragonFly 2020 Pro 3D printer to three prominent American customers. Nano Dimension also announced the opening of its third Customer Experience Center co-located with the company's U.S. headquarters in Santa Clara, California.

## **MULTI-BOARD ASSEMBLY**

## ENSURE MULTI-BOARD ENCLOSURES FIT

Interconnected Multi-Board Assembly in Altium Designer®

For more information please visit: www.altium.com/solution/multi-board

## **DDR3/4 Fly-by Topology** Termination and Routing

#### **Beyond Design**

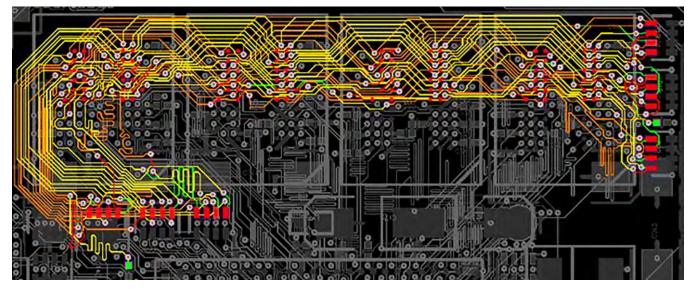

#### by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

DDR3/4 fly-by topology is similar to daisy chain or multi-drop topology, but it includes very short stubs to each memory device in the chain to reduce the reflections. The advantage of fly-by topology is that it supports higher-frequency operation and improves signal integrity and timing on heavily loaded signals. If you are employing high-frequency DDR4, then the bandwidth of the channel needs to be as high as possible. However, with today's extremely fast edge rates, the sequencing of the stubs and the end termination, and the associate load, can make a measurable difference in signal quality. In this month's column I will look at how best to route DDR3/4 fly-by topology.

Reflections occur whenever the impedance of the transmission line changes along its length. This can be caused by unmatched drivers/loads, layer transitions, different dielectric materials, stubs, vias, connectors, terminations and IC packages. By understanding the causes of these reflections and eliminating the source of the mismatch, a design can be engineered with reliable performance. For perfect transfer of energy and to eliminate reflections, the impedance of the source must equal the impedance of the trace, as well as the impedance of the load.

As signal rise times increase, consideration should be given to the propagation time and reflections of a routed trace. If the propagation time and reflection from source to load are longer than the edge transition time, an electrically long trace will exist. If the transmission line is short, reflections still occur but will be overwhelmed by the rising or falling edge and may not pose a problem. But even if the trace is short, termination may still be required if the load is capacitive or highly inductive to prevent ringing.

Series termination is an excellent strategy for point-to-point routes, one load per net.

Figure 1: Fly-by topology for clock, address and command routing.

# We've been delivering quality circuit boards since 1985!

Since 1985, U.S. Circuit has been a premier supplier of both commercial and military Printed Circuit Boards in the United States. We have experienced continued and steady growth in a challenging economy through consistently high performance in on-time delivery, superior quality and an emphasis on the highest level of customer service. We are proud to be the Circuit Board Manufacturer of more than 400 growing companies.

Click to Download Our Brochure

**COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

Whereas parallel (end termination), is preferred for busses with a number of loads in a multi-drop topology. For DDR3/4 layouts, a series termination is generally not required for on-board memory devices. However, if your design has plug-in memory then the data and data mask signal length may be excessive and require a series termination.

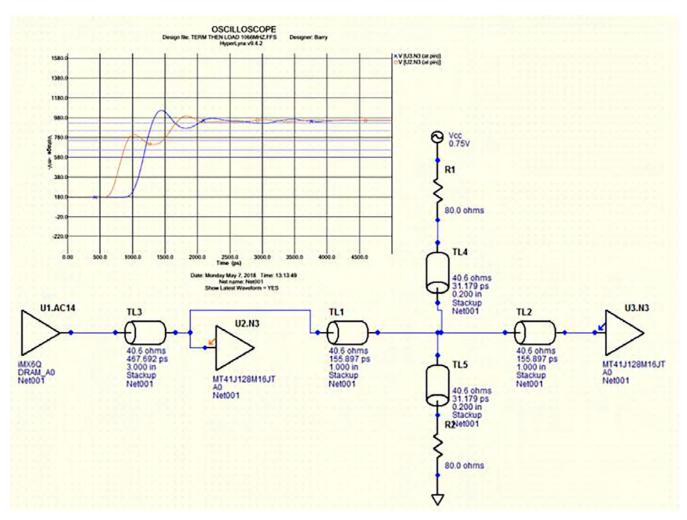

With the fly-by address, control and command (ACC) signals, the traces should be routed as practicable as possible to the memory device pins and the parallel termination placed at the end of the line as in Figure 1. Short stubs can be used to connect the passing signal to each memory device in sequence but the longer the stubs the higher the capacitance. This stub capacitance, along with the parasitic input capacitance of the receiver pin, creates an imperfection in the termination network. When implementing parallel terminations, it is not always possible to place the termination after the final load in a multi-drop topology due to real estate restrictions. Figure 2 shows the schematic of this configuration. If the stub is very short and the signal edge rate is not excessively fast, then this may be acceptable. However, as the edge rate increases, the extra capacitance of the stub is significant and creates reflections.

When the first incident wave arrives from the driver, part of that wave, which is a small pulse, bounces off the imperfection and returns to the driver. This pulse bounces again off the low-output impedance driver and returns one round trip later to the receiver. What we observe at the receiver is the initial rising edge, followed one round trip later by a secondary pulse. If the initial reflected pulse is sufficiently

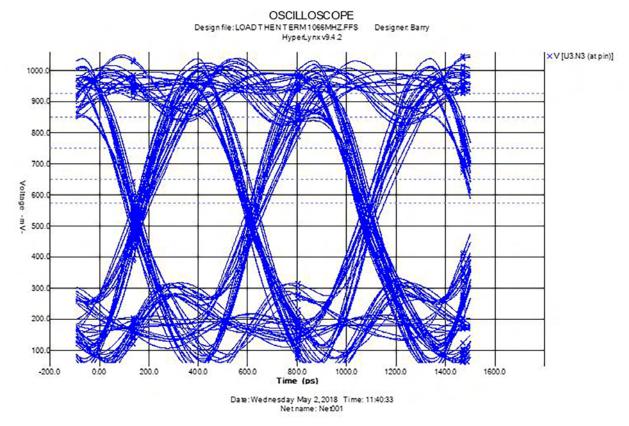

Figure 2: DDR3 address signal with termination before final load (all simulations performed in HyperLynx).

Figure 3: DDR3 fly-by topology with termination after final load.

small, all subsequent reflections will be negligible. However, in this case, the reflection causes a non-monotonic edge at the first receiver (orange waveform), which could lead to false triggering of the receiver. If for example, there are four memory chips on the address line, then this would occur on all receivers except the last to a similar extent.

Figure 3 illustrates a typical DDR3 fly-by topology with the termination at the very end of the final load. Also, the passing address signal trace goes directly to the receiver pins with no stub. This is the ideal scenario. In this case, there are no reflections, from the termination, which can be seen from the waveforms.

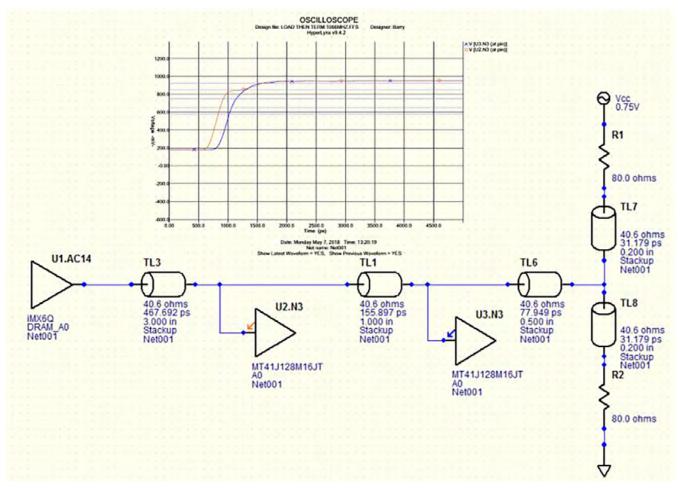

Now let's add a half inch stub from the passing address signal trace going to each receiver input pin, as I have seen many designers do. Figure 4 shows the schematic and the resultant waveforms. The reflections created by the additional capacitance, of the stubs, is not quite as bad as that of Figure 2, which had the termination before the final load. However, this demonstrates the impact of stubs on the ACC signals in the fly-by topology. Figure 5 shows the jitter and noise created by the half inch stubs on the signal.

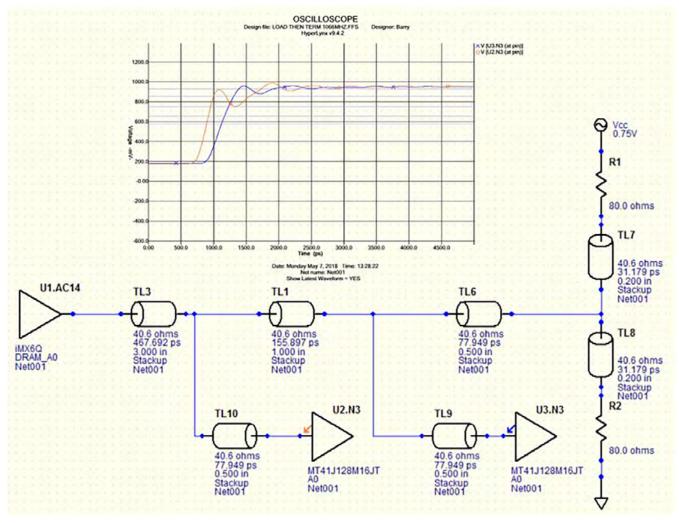

After running a few more, quick simulations in HyperLynx LineSim with varying stub lengths, I found that the stub length can be no more than 200 mil, to alleviate the impact of the reflections, in this (typical) case. This results in the reasonably clear eye diagram of Figure 6.

In conclusion, DDR3/4 fly-by parallel terminations should be placed after the last receiver at the end of the transmission line and routed directly to the last receiver. Since there is no reflection from this topology, this implies that the length, from last receiver to the termina-

Figure 4: DDR3 fly-by topology with end termination and 500 mil stub.

tions, does not need to be matched to the delay/length of the other signals in the ACC group. Also, further simulations confirmed that the length can be rather long (up to 3 inches) without any noticeable degradation of signal quality. Stubs to each receiver input, from the passing signal, should be kept below 200mil in length to maintain a clear eye.

#### **Key Points:**

- Fly-by topology supports higherfrequency operation and improves signal integrity and timing on heavily loaded signals.

- The sequencing of the stubs and the end termination and the associate load can make a measurable difference in signal quality.

- Reflections occur whenever the impedance of the transmission line changes along its length.

- If the propagation time and reflection from source to load are longer than the edge transition time, an electrically long trace will exist.

- If the trace is short, termination may still be required if the load is capacitive to prevent ringing.

- Series termination is an excellent strategy for point to point routes, one load per net.

- Parallel (end termination) is preferred for busses with a number of loads in a multi-drop topology.

- Address, control and command (ACC) signals, traces should be routed directly to

Figure 5: DDR3 fly-by topology with 500 mil stubs to receiver inputs.

Figure 6: DDR3 fly-by topology with 200 mil stubs to receiver inputs.

the memory device pins and the parallel termination placed at the end of the transmission line.

- Stub capacitance, along with the parasitic input capacitance of the receiver pin, creates an imperfection in the termination network.

- There are no reflections when the passing address signal trace goes directly to the receiver pins with no stub and the termination is at the very end of the line.

- Stubs create reflections and have a detrimental impact on the address signal in the fly-by topology.

- Simulations suggest that the stub must be a maximum of 200mil to alleviate the impact of the reflections.

#### **References:**