l'Connect007

# DESCRIPTION OF THE OPTIMIE

## Your how-to guide for making Rev 1 work.

In this book, readers will learn how to design complex boards correctly the first time, on time. A must-read for anyone designing high-speed, sophisticated printed circuit boards. THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

#### **Executing Complex PCBs**

Scott Miller Freedom CAD Services

1.007 Books

DOWNLOAD NOW

I-007ebooks.com/ecd

"A comprehensive tour through the world of thermal management. Required reading for designers and end users wishing to understand the science and practice of using insulated metal substrate materials."

Alun Morgan Chairman, EIPC

#### THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

Thermal Management with Insulated Metal Substrates

#### **Download Now**

Written by Didier Mauve and Ian Mayoh of Ventec International Group, this book highlights the need to dissipate heat from electronic devices.

> Didier Mauve and Ian Mayoh Ventec International Group

> > 007

I-007ebooks.com

#### MAY 2019 • FEATURED CONTENT

## DESIGNOOT MAGAZINE

## **Design Rules**

We've heard a lot about design rules lately, from designers and manufacturers alike. There just doesn't seem to be much agreement about design rules: how to set them, manage them, and validate them. We've seen how the IC segment has standardized its design rules process; is this sort of alignment possible in PCB design? For this issue, we spoke with a number of design and manufacturing experts about design rules and constraints.

10 Design Rules Recipe: Solvability, Manufacturability, and Performance Interview with Mike Creeden and Freedom CAD Services

18 Design Rules, Simulations, and Analyses An I-007eBook excerpt

- 30 Altium's Craig Arcuri on Design Rules: Past, Present, and Future Interview with Craig Arcuri

- 38 Mentor's EDA Perspective on Managing Design Rules Interview with Dave Wiens and Mike Santarini

#### FEATURE COLUMNS:

- 22 High-speed PCB Design Constraints by Barry Olney

- 46 Rules Keep You From Crossing the Line by Tim Haag

52 Board Negotiations: Design Rules and Tolerances by Mark Thompson

## Pcbcart

#### Get Your PCBs Assembled within Budget and Time Schedule

YOUR FIRST ORDER GET AN EXCLUSIVE

\$200

PCBCart's Consigned & Turnkey PCB Assembly services let you get fully assembled circuit boards at lightning speed and low cost without compromising quality.

We manage project from concept to delivery and make the entire assembly process as seamless and smooth as possible, saving you from dealing with multiple vendors and allowing you more time on project engineering & marketing issues.

#### **Our Advantages:**

DISCOUNT!

Flexible Volume: Prototypes, low volume, high volume

- Multiple Assembly Technologies: SMT, THT, Mixed Assembly

- Multiple Components Selection: Thru-hole, BGA, QFN, 01005, 0201...

- Multiple Value-added options: Free DFM Check, AOI, AXI...

WWW.PCBCART.COM SALES@PCBCART.COM

#### MAY 2019 • ADDITIONAL CONTENT

## DESIGNOOT MAGAZINE

#### SHORTS:

- 9 2D Materials May Enable Electric Vehicles to Get 500 Miles on a Single Charge

- 17 Wrap-around Sensors for the Grid

- 20 Words of Advice for New PCB Designers

- 28 The First Walking Robot that Moves Without GPS

- 55 Quantum Sensors Improve Sensitivity of Magnetic Resonance

- 69 KAIST Technology Controls Near-field Thermal Radiation

6

79 Viennese Scientists Develop Promising New Type of Polymers

#### **ARTICLE:**

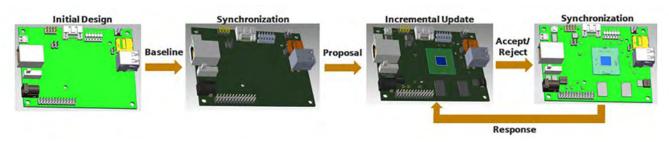

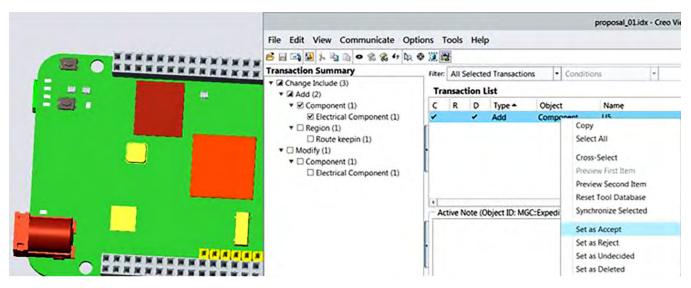

72 MCAD Is From Mars, ECAD Is From Venus by Linda Mazzitelli

#### **COLUMNS:**

- 8 Design Rules: For Your Own Good by Andy Shaughnessy

- 58 Spotlight on the Orange County Chapter by Stephen Chavez

- 62 Accurate Gerber Files Are Mission Critical for Smooth PCB Manufacturing by Bob Tise

66 Thermal Management: Why It Should Be High on Your Circuit Protection Agenda by Jade Bridges

#### HIGHLIGHTS:

- 56 PCB007

- 70 MilAero007

- 80 Top 10 PCBDesign007

#### **DEPARTMENTS:**

- 83 Career Opportunities

- 90 Events Calendar

- 91 Advertiser Index & Masthead

## **5G: Higher Frequencies!** Do you have the **right** circuit materials?

Frequencies at 28 GHz and higher will soon be used in Fifth Generation (5G) wireless communications networks. 5G infrastructure will depend on low-loss circuit materials engineered for high frequencies, materials such as RO4835T<sup>™</sup> laminates and RO4450T<sup>™</sup> bonding materials from Rogers Corporation!

Rogers RO4835T spread-glass-reinforced, ceramic-filled laminates are low-loss materials in 2.5, 3.0, and 4.0 mil thicknesses. They are well suited for millimeter-wave frequencies as part of the inner cores of 5G hybrid multilayer PCBs. They can work with other materials to provide the many functions needed by 5G wireless base stations, including power, signal control and signal transfers.

Н

Vehicle to

Rogers RO4450T bonding materials are available in 3, 4, and 5 mil thicknesses to help construct those 5G hybrid multilayer circuits. These spread-glass-reinforced, ceramic-filled bonding materials complement the different materials that will form these hybrid circuits, including RO4835T and RO4000° laminates. And for many 5G hybrid multilayer circuits, Rogers CU4000<sup>™</sup> and CU4000 LoPro° foils will provide a suitable finishing touch for many hybrid multilayer circuit foil lamination designs.

#### 5G is coming! Do you have the right circuit materials?

Learn more at www.rogerscorp.com/5G

Advanced Connectivity Solutions

\* IPC TM-650 2.5.5.5 Clamped Stripline at 10 GHz - 23°C

USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611 www.rogerscorp.com

| Product         | *Dk  | *Df    |

|-----------------|------|--------|

| RO4835T 2.5 Mil | 3.33 | 0.0030 |

| RO4835T 3.0 Mil | 3.33 | 0.0034 |

| RO4835T 4.0 Mil | 3.32 | 0.0036 |

| RO4450T 3.0 Mil | 3.23 | 0.0039 |

| RO4450T 4.0 Mil | 3.35 | 0.0040 |

| RO4450T 5.0 Mil | 3.28 | 0.0038 |

|                 |      |        |

lehicle to

mart Gri

Vehicle to Pedestriar

## Design Rules: For Your Own Good

The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

Rules are a part of life, but most of us don't like following the rules; I certainly don't. But I think we can make an exception for design rules.

Many of you remember simpler times when you didn't need any stinkin' rules. Those were the good ol' days. Try to design even a simple board now without some constraints.

Like most rules, design rules came about for your own good. And no single designer could possibly remember all of the constraints re-

quired to design one of today's PCBs. But with a set of well-defined design rules, a designer can execute the most complex PCBs on the first try.

I have to admit that I had no idea that designers had to contend with so many design rules for each design. Designers tell me they routinely have to set hundreds of design rules for the more high-tech designs. How does a designI will follow the rules I will follow I will follow

er manage all of these design rules and avoid over-constraining the design, which adds unnecessary cost and complexity?

One thing that struck me while working on this issue was how little agreement exists about best practices for design rules. If you ask a half-dozen designers to explain their approach to design rules, you might get a half-dozen answers.

It reminds me of the Wild West. You may have design rules for schematic, layout, fabrication, signal and power integrity, thermal, and assembly. With high-speed boards, you may have to set up matched-length, differential pair, DDR, and spacing constraints. And that's just the tip of the iceberg.

I will follow the rules I will follow the rule I will Wow the rules ow the rules I will t ow the rules I will the rules the rules the rules

Today's more powerful PCB design software tools all feature constraint editors that make setting and managing design rules about as simple as it's going to get. But setting up design rules is still a time-consuming part of each design cycle.

Is there a model for us to follow? Our friends in the IC arena figured out design rules years ago. Of course, that's a whole

different ballgame with only a handful of manufacturers serving that market. But those manufacturers laid down the law. "If you want to work with us, here's what you're going to provide us, every time." That took care of that problem. But that may not work for our segment with thousands of PCB fabricators worldwide.

So, we asked our expert contributors to discuss possible paths forward regarding design rules. First, we have a wide-ranging interview with Mike Creeden of San Diego PCB and Freedom CAD's Scott McCurdy, Jay Carbone, and Rich Kluever who discuss design rules from the perspectives of designers and fabricators as well as the need for a universal design data input. Next, we have a short excerpt from the new I-007eBook written by Scott Miller from Freedom CAD titled The Printed Circuit Designer's Guide to... Executing Complex PCBs, which focuses on using design rules.

Then, columnist Barry Olney weighs in with a feature on high-speed design constraints, explaining how to set design rules based on prelayout simulation, and how IPC's guidelines can go a long way toward helping designers set constraints. In an interview, Altium's Craig Arcuri follows up with a look at design rules from his vantage point of running both design and manufacturing companies, and why this industry, especially design software, must evolve sooner rather than later. We also have an interview with Dave Wiens and Mike Santarini of Mentor, a Siemens Business, who explain how design rules are part of the "shift left" movement to enable more decision-making earlier in the design process, and why PCB designers of today must have crossdomain awareness to succeed. Columnist Tim Haag explores the need for design rules and knowing when it's okay to break them. Then, columnist and author Mark Thompson highlights some of the challenges related to setting design rules for tight tolerances, and why negotiation is sometimes needed.

We also have columns from our regular contributors, including Bob Tise of Sunstone Circuits, Jade Bridges of Electrolube, and Stephen Chavez representing the IPC Designers Council. Further, we have a great article by Linda Mazzitelli of PTC that investigates the ongoing convergence of ECAD and MCAD technology.

It's a great time to be in this industry. See you next month! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 19 years. He can be reached by clicking here.

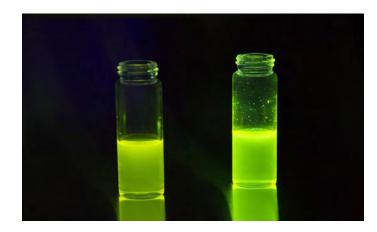

#### 2D Materials May Enable Electric Vehicles to Get 500 Miles on a Single Charge

Lithium-air batteries, which currently are still in the experimental stages of development, are poised to become the next revolutionary replacement for currently used lithium-ion batteries that power electric vehicles, cellphones, and computers.

Lithium-air batteries can store 10 times more energy than lithium-ion batteries and are much lighter. However, lithium-air batteries could be even more efficient and provide more charge with the incorporation of advanced catalysts made from two-dimensional materials. "We are going to need very high-energy density batteries to power new advanced technologies that are incorporated into phones, laptops, and especially electric vehicles," said Amin Salehi-Khojin, associate professor of mechanical and industrial engineering in the University of Illinois at Chicago's (UIC's) College of Engineering.

One of the reasons the 2D TDMCs performed so well is because they help speed both charging and discharging reactions occurring in lithium-air batteries. They also synergize with the electrolyte.

Poya Yasaei, Zahra Hemmat, Pedram Abbasi, Shadi Fuladi, Xuan Hu, Robert Klie, Fatemeh Khalili-Araghi, and Baharak Sayahpour of UIC and Robert Warburton and Jeffrey Greeley of Purdue University are co-authors on the paper.

(Source: UIC)

## Design Rules Recipe: Solvability, Manufacturability, and Performance

#### Feature Interview by The I-Connect007 Editorial Team

One thing that we've noticed lately: Each designer seems to have his or her own way of using PCB design rules. There doesn't seem to be much agreement about setting or using design rules.

So, in this true experts panel, Mike Creeden of San Diego PCB joined Freedom CAD's Scott McCurdy, Jay Carbone, and Rich Kluever to share their views on PCB design rules. This wide-ranging discussion with Andy Shaughnessy, Nolan Johnson, Barry Matties and Happy Holden covers everything from identifying the required constraints to setting electrical and manufacturing design rules and managing these often disparate requirements.

**Andy Shaughnessy:** Welcome, gentlemen. The topic of design rules keeps popping up, and there's not much agreement about best practices. Or is there? Mike, can you talk about how you go about setting up design rules?

**Mike Creeden:** Design rules help us utilize the strength of our CAD tool to make the circuit do

what we want it to do, and that occurs in three areas. I always talk about what I call the "designer's triangle," which are three perspectives when we look at the layout.

The first perspective would be the layout solvability. You have to solve the layout, and your design rules enable you to do that. I'm able to pin-escape from fine-pitch parts, and at the same time, I want to balance that with DFX or DFM. Second, physically speaking, I must address the concerns for the manufacturing process and capabilities of my supply chain. I want to optimize them because the more robust I can make it, the higher producibility and reliability I would have long term and in a production volume. Third, the other perspective is performance. Performance is many things, including signal integrity, power delivery, thermal, etc., and all those things have to be met.

We don't want to over-constrain anything. And you cannot do one or two of those perspectives I just mentioned and ignore the other one. When we apply our design rules, there might be an EE as well as a layout person sometimes, that is the same person—and then there's also design rules from the manufactur-

## THINK TWICE BEFORE PICKING YOUR PCB DESIGN FLOW.

#### PADS PROFESSIONAL IS SOFTWARE FOR THE MOST DEMANDING ENGINEERS

As PCB designs become more challenging, don't let your design flow become a career liability. PADS Professional is the high-grade software demanding engineers can count on to tackle the most complex projects.

AVAILABLE FOR A LIMITED-TIME PROMOTION STARTING AT \$8995\*

\*REGIONAL PRICING VARIATIONS MAY APPLY.

#### EVALUATE TODAY

ing supply chain. They may be different than the physical layout rules to pin escape. All design rules should be added as early on in the layout cycle as possible. Then, it's correct by construction.

**Shaughnessy:** Scott, can you take us through your process?

**Scott McCurdy:** I approach the design industry coming from my background of running a PCB fabrication company, where half the things that came to us had to be put on hold because something was wrong in the design. Sometimes, there was

Scott McCurdy

just no adult supervision at the other end. At Freedom CAD, we are a PCB design service bureau and create hundreds of designs each year, so I'm also including Jay Carbone, one of our top designers who lives for this stuff and is one of our better "interactors" with engineers, in this conversation. We deal with a lot of different personalities and skill levels. I also brought Rich Kluever, who was at Solectron for many years at the CM level running Valor, identifying design problems at the factory that was going to have to assemble this stuff. Rich has tried to bake into our process and people more of a manufacturing perspective because every one of our designs goes through Valor twice.

**Jay Carbone:** I can identify with the "designer's triangle" concept because that's a constant battle. A schematic is a perfect world; as soon as we put a piece of etch down on a board, we've compromised that perfect circuit. With RF circuitry, assembly rules go out the window. Sometimes, RF engineers want to pig-gyback caps or share component pads. Various technologies dictate different sets of rules; there's no one-size-fits-all solution.

We start with a kickoff meeting with the electrical engineer to go over the circuitry and

technology. From there we start putting in the rules. We like to identify potential signal integrity issues up front. As far as spacing and line widths, this might be a little bit further down the road as you handle the placement and become more familiar with the components, etc. For example, maybe they can get away with using five or four mil traces for ease of manufacturing, or maybe they're down to a 3.5 for impedance reasons.

Creeden: You can only put so many rules in today's modern CAD tools. The eyeball check that designers do so often is understated and undervalued. The other thing I wanted to address is an idea for a universal output. Scott and I had this discussion earlier. We have a universal output, such as ODB++ or IPC-2581, which are intelligent data formats for output. As an industry, we do not have a universal intelligent data input. I've talked to a couple of the CAD manufacturers, and they're all thinking about it, but they want to make it their own proprietary blend. Instead, I would encourage them to have a universal input that any fabricator could use; then, it could be used by whatever CAD tool the designer uses.

**Nolan Johnson:** Scott, I was wondering if you'd be willing to drill down on that for a little bit. A universal input is a great idea. What do you envision that looking like?

**McCurdy:** At some point, it needs to be a data file, and I envision it being the same thing as an ODB++ or IPC-2581 where it's universally portable into any CAD tool. It would show the manufacturer's process constraints and capabilities matrix as well as the stackup in the usage, material, and copper weights. All of these things exist in little islands of automation, but I would like to see a fabricator create this input where any CAD tool could read it.

**Johnson:** What do you see as a mechanism for bringing better control over design rules down to the designers who work toward the bottom half of the bell curve?

**McCurdy:** The manufacturer can output at the start of the job what their capabilities matrix are. When any designer approaches a part, they're going to look at the densest BGA on the board first, the highest pin-count device, and what the pitch and feature size is. That tells them what they need to use for minimum features to pin escape and sets up a whole chain reaction of design rules for the solvability.

**Carbone:** To your point of the designer's triangle, I would look at the technology and my highest speed first. Is back-drilling allowed? How many layers am I going to need to exit that BGA? In the end, my dielectric may be so thin that I have 3.25-mil lines because I have a 28-layer card and I can only have .102" to do it in. Now, I have to go back to the manufacturer and customer and say, "This is the box you put me in. Can this be fabricated? What are the yields on this, and what can we do to mitigate loss?"

**Barry Matties:** Do designers typically know who's going to be manufacturing the board when they set out to design the board, or does that happens post-design?

**Creeden:** That's a great question, and it gives as many answers as there are designers out there. But as someone who has done some public speaking on this subject, the designer should know to seek that information right upfront. And if you do not have it, you're just doing a small run or a debug board, for example. Or your procurement people don't want to tell you who they're building with, so you have to design for the solvability portion of the triangle, such as what do you need to pin escape.

**Matties:** We were talking to some suppliers yesterday about materials and how it affects the design of PCB boards and base material laminate, and they indicated that a designer will come to a fabricator, and the fabricator will say, "This is the material that we use." Then, the designer is pretty much locked into that.

**Creeden:** That's very true, and I work a lot with Insulectro who try to bring all of the materials to the fabricators out there. Material science is becoming much more integrated into highspeed design. It has to because the material is where the electromagnetic field exists. You must involve them at the beginning, and if the fabricator is making those decisions, you have to ask the electrical engineer or understand the performance requirements.

**Shaughnessy:** Rich, you come from a manufacturing background. What are some of the things when you are setting up design rules that you look for?

**Rich Kluever:** We're unique in the sense that we listen to questions about their supplier base and who their fabricator is going to be. We're in the middle where we take requirements from a lot of different customers and engineers and funnel

**Rich Kluever**

them through to various suppliers. We don't have a single path of where we always use the same suppliers or rules. I have my rules set to point me to things and let me make decisions. Again, we don't always know where everything's going, so we try to use the industry standard. We're constantly updating our knowledge base with the feedback we receive from some suppliers on things that are good and things that aren't.

**Matties:** What you're describing comes down to designer knowledge and expertise. What advice would you give to a new designer?

**Kluever:** Ask a lot of questions and work with us; a lot of our designers develop this experience. In the Valor group, we act as gatekeepers. We're not going to let you send something out that isn't manufacturable. It's a matter of building that knowledge base by receiving feedback and understanding where you may have misunderstood or made mistakes before. Understand what all of the terms are. It's tough to just say, "Here's everything you need to know," because all of us on this call probably have been doing this for 30 years, and we don't know everything we need to know.

**Matties:** Is there a design review process that a service bureau offers versus just doing the design?

**Creeden:** I deal with this a lot as a trainer, and I think your question is, "What about the EE who has now been conscripted to do PCB layout and has no design training in college?" We're looking hard at that subject. Surveys say

**Mike Creeden**

that 50–60% of designers will be gone in five years, so that knowledge base will be gone. But the industry thinks a MOOC (massive open online course) class can be a Band-Aid solution. It's an online course that you can take in two hours to learn how to be a designer. Anyone who has been in the business for a while laughs because it's so ineffective.

**Kluever:** And it's important to understand the "why" of the rules as much as the "what." You're going to have times that you will have to balance these things and make tradeoffs. You need to understand which one you can give more than another, and if there is a fail, is it a less serious fail than something else? For example, finding a failure in the fabrication process is better than finding one after you've soldered on a \$1,000 BGA.

**Matties:** It sounds like there's no piece of software or book that will guide you to that end.

**Happy Holden:** Yes, but that's the problem. Design rules can be determined mathematically,

but unfortunately, nobody is taking the time to put down rules or write the software that essentially creates a planning tool. I've looked at this for the last 40 years, so I have a planning tool, but I can't sell it because it has no documentation and if you look at it cross-eyed, it will go apart, but I call it a virtual prototype. Our industry keeps adding new sets of rules as we come up with other devices and constraints. For example, there are requests for designers to design for recycling and being environmentally friendly.

**Matties:** With the movement to the digital factory and smart manufacturing, what impact, if any, is that playing on the design community?

**Creeden:** I'm not seeing much at all, but I'm sure hoping that universal manufacturing rules are a byproduct of it. One of the most advanced, leading factories is GreenSource Fabrication is in New Hampshire, and at some point, the industry's goal is that the automation that they have would be transferable to the layout project.

**Matties:** A whole new level of data will have to be uniform and provided.

**Kluever:** I don't see how there could be one rule that fits all because all of these manufacturers have such a wide range of capabilities.

**Creeden:** Nobody's saying that there's one rule; we're saying that there's one format whereby each factory can plug in their capabilities matrix and process allowances.

**Holden:** Yes, that's what I call the virtual prototype or the design planner, which is badly needed software. One of the things I saw while working with Freedom CAD on their eBook is that the majority of their work is in the front-end planning of the design—not operating the EDA tool.

**Johnson:** Happy, I just want to tie the thought that you just made back to something that Rich said earlier, describing your Valor model as being a user and defining your rules in

## tec-speed 20.0 Dk 3.0-3.48

## No More Compromises Performance, Price & Availability

SUPERIOR loss characteristics

**GREATER** reliability **UNRIVALED** high frequency performance

Visit www.ventecsolutions.com/tec-speed-20

ventec-speed

such a way that it started to flag areas that you wanted to pay attention to. Rather than just straight-up manufacturing violations, which is how everybody seems to look at how they define the rules, you have a philosophically different approach, and Happy is touching on that too. When you change to that sort of a thinking model, how did that change using the tools and results?

**Kluever:** It requires you to be a lot more interactive with the tool in making decisions and not letting the tool make the decisions for you. I'll give you a good example with solder mask clearance. Some people want the solder mask to be designed exactly as they want the end product to be, whether it's two- or three- mil clearance and some mask defined pads. There are folks that roll up all of their solder mask at one-to-one and let the fabricator modify it accordingly.

In our world, how do I set a rule for that? I have multiple rules. I set a rule very high so that all of the solder mask fails. Then, I let the tool do the math for me and segregate the results. Now, I can look at it, and say, "All of the solder mask has two-mil clearance." If 90% of it is two-mil clearance, but six parts are one-to-one, I don't like that. So, I focus on those six parts and adjust them to be two-mil clearance so that everything is the same.

**Creeden:** I think what Happy was alluding to was intelligent input for rules. When do you use your rules? When do you apply them? When do you check them? If you're doing them at the end of the design, you're going to find errors, but those are very costly. When you appropriate correct-by-construction methodologies supported by your toolset, whatever that may be, you're correct by construction.

**Matties:** Are there any housekeeping rules that we should have for managing design rules? In other words, how do we keep them organized, and what should people think about?

**Creeden:** To me, they're relative to the circuit and fabricator or manufacturing supply chain

you're using. Essentially, rules don't stand alone by themselves because there are 1,000 rules out there. I want ones that apply specifically to the circuit I'm doing, and I'm going to implement it to achieve the performance of the circuit as well as how I'm going to build it with reliability and have the circuit perform the way I want it to.

**Matties:** Do you create a new set of rules for every design that you're starting?

**Creeden:** Absolutely. They're similar, but every circuit is its own entity for rules. I may use a rule set that I used someplace else, but rules have to be assigned to parts, nets, areas, features, layers etc. I never want to assume that if a rule worked on a previous circuit, it will also work here.

**Matties:** That's great advice because, for a manufacturer, you may fall into, "I've used these rules in the past with this manufacturing and it's going to apply here again." Does that happen?

**Creeden:** Yes, because factories do have a capability matrix, and they may be the same, but how they apply them on a four-layer board is different than how they would on a 12-layer board. You have to drill down, and ask, "How does this board work in this factory?"

**Carbone:** Multiple plating cycles or a different stack-up could change the line widths or impedance of a proven circuit. There are many different factors for changing stack-ups or moving a circuit to different layers of the card.

Jay Carbone

**Kluever:** You also have to consider the conditions of your design and what you're trying to do. I've had cases where people apply a rule, such as a solder mask oversize on a BGA, and say, "Yes, but we've always used this and it works," to which I respond, "But in the past, you didn't try to route a trace in between these paths." They've changed the condition of the design, so the rule doesn't apply anymore. You also have to understand where those rules truly apply.

**Holden:** Because semiconductors are constantly becoming more complicated, every time you start a new project, there's probably a new set of constraints that dictates that you have to come up with a new set of rules. The rules used last time, even for this company, now conflict because it doesn't meet signal integrity, cost, etc. It's something that everybody learns, which is unfortunately why we say we're concerned about experienced professionals retiring.

**Creeden:** Happy, you hit on something that I think is very important for us to touch on as a group. How do rules interact? For example, if I'm doing DDR, I'm going to match lengths on a bus. CAD tools are so powerful that I can match it to the micron and they can do it. It may not even need it, but we do it anyway because we like that power and want to match it. Often, we need to ask if there's a package delay coming off the chip and if that has been factored in. If I have two forward crosstalks and I'm external, that just made the problem worse. It's not as black and white as "I have some rules. Let's implement them." There's an environmental consideration that needs to be looked at.

**Shaughnessy:** Because it sounds like a lot of hours are being spent on setting up these design rules.

**Creeden:** Well, correct by construction—you either want it right, or you don't, so pick one.

**Matties:** There's no time to do it right but plenty of time to do it over.

**Shaughnessy:** I just want to acknowledge the wisdom and expertise that is being shared on this call. Do you have any final thoughts?

**Creeden:** My closing thought would be that a design will only be as accurate as the rules that constrain it. Those rules need to look at it from the three perspectives I mentioned: solvability, manufacturability, and performance.

**Matties:** Thanks for all of your input today. It's greatly appreciated.

**Creeden:** My pleasure.

#### **McCurdy:** Thank you.

Visit I-007eBooks.com to download *The Printed Circuit Designer's Guide to... Executing Complex PCBs* written by Scott Miller from Freedom CAD Services Inc. as well as other free, educational titles. **DESIGN007**

#### Wrap-around Sensors for the Grid

Scientists at Oak Ridge National Laboratory have developed a low-cost, printed, flexible sensor that can wrap around power cables to precisely monitor electrical loads from household appliances to support grid operations.

Using an inkjet printer, researchers deposited wires on a flexible plastic substrate, then wove in a magnetic strip to channel the flux produced by an electric current, making the sensor suitable to install in tight spaces. When tested on conductors in the lab and on a building HVAC unit, the sensor measured responses of up to 90A of electrical current and is expected to exceed 500A in larger applications.

"These inexpensive sensors provide crucial, real-time usage data needed to monitor and control devices, such as smart HVAC and water heaters for better power grid efficiency and resilience," said Pooran Joshi, a senior scientist in the Materials Science and Technology Division at ORNL.

The team is currently testing new materials, electronics, and packaging to increase the sensor's range and applications while keeping costs low.

(Source: Oak Ridge National Laboratory)

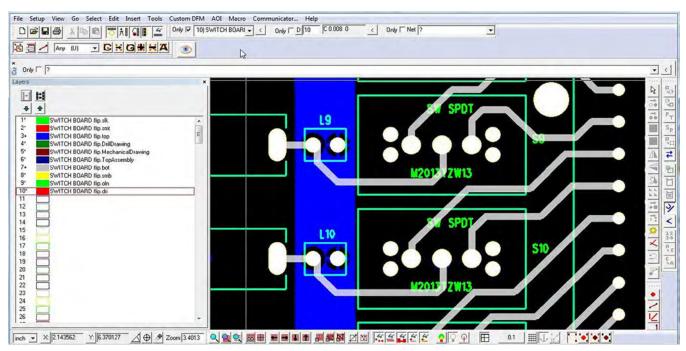

## Design Rules, Simulations, and Analyses

Timing is everything in life and complex PCBs. —Anonymous

## The following is an excerpt from Chapter 5 of *The Print-ed Circuit Designer's Guide to... Executing Complex PCBs* written by Scott Miller of Freedom CAD Services.

It is a fact that complex electronic components will not function properly unless a specific set of physical conditions is met. Active components and chipset performance requirements are presently being pushed to the edge. Their capabilities are only limited by the physical geometry and electromechanical properties of the materials that interface with them. We have come to the point where component chip makers are supplying 100-page user manuals describing not only what a chip can do, but also the layout, assembly manufacturing, and environmental operating criteria required for it to perform. Careful attention to these rules must be considered for the successful operation of the individual component within a circuit and the performance of the circuit in relation to all circuits on the PCB.

#### One designer said:

"Signal and power integrity analysis is a key way to ensure that the board design will meet the performance requirements on the first pass. By using software to simulate the effects on signal and power integrity, our customers spend less time in the lab trying to find out why their design isn't performing as expected. Performing in-process simulations enables problems to be identified and corrections to be made earlier in the design process, thus minimizing the collateral damage. The more items you have to move to address a problem, the more time this takes."

#### **Starting the Physical Design Process**

The next step is entering the execution phase of the board design process, which involves implementing all of the elaborate pre-planning that has already taken place.

#### **Layout Processes**

Many companies employ a number of specialized layout processes. One senior project engineer explained his process for very complex boards that he has refined over many years:

"I work with larger OEMs, and this is what I tell them. I go through their design and create libraries of templates to give us predictabil-

## When others say NO to your toughest designs, we have the tools to say YES.

With the right tools, you can build anything. ASC has the experts, technology and experience necessary to build anything you might need, all under one roof.

More about our advanced solutions

American Standard Circuits

Creative Innovations In Flex, Digital & Microwave Circuits

www.asc-i.com | (630) 639-5444

ity and efficiency. What I do is predictive engineering, which is to reuse circuits that they've already used. If they are a repeat customer, they already know it works, and now suddenly it saves them in fabrication, assembly, tests, and debug. They save a boatload of money and end up with fewer spins.

Our process is to create reusable modules. This allows us to use parts that you've already used, and if it's a new part, we go ahead and do a module for it; just substitute the old one for the new one after we've modified it. So, from that point on, after it has been proved to work, it works for us.

First, we have them define stackups ahead of time. We sit down with the customer and their fabrication shop and determine whatever layer count they feel with this particular company works best. We build in all of the fabrication capabilities that their fabrication house has because they usually have more than one fabrication house. We're just trying to define everything ahead of time so that it now becomes predictable.

Then, you place and replicate as much as you can. That's really what it comes down to. When the placement is done, you do placement verification. Then, once that's all done, approved, and cleaned up, you route all of the differential pairs and high-speed clocks. Next, you send that to engineering for them to review and route the remaining signals, which are pretty much single-ended nets, matched groups, etc. That last step is final verification. When we get to that, we send them a final board to review. We can do it in two weeks when we have all these pieces in place because it's already designed.

"At least I know that the replication process or reuse process is very good. It works, and people that have experienced it like it. And now the tools are better."

The process is as follows, using clusters, templates, and bundles:

- Auto-cluster from schematics

- Auto-place for complex parts

- Place

- Replicate and/or reuse templates

- Placement verify (refine)

- Fabrication and assembly review

- Cluster nets into bundles and route

- Complete routing with constraints

- Engineering review for SI, PI, and power distribution network (PDN)

- Rest of routing

- Validation (DFM and DFT)

- Create a template for future use

- Customer review

- Deliverables

Visit I-007eBooks.com to download *The Printed Circuit Designer's Guide to... Executing Complex PCBs* as well as other free, educational titles. **DESIGN007**

#### **Words of Advice for New PCB Designers**

In a recent survey, we asked the following question: What do you think is the most important thing a designer should remember when planning a new PCB design? Here are a few answers, edited slightly for clarity.

- 1. Have a good music selection.

- 2. Don't panic. It's almost always

- possible to complete a complicated design if you go step by step.

- 3. How will the board be fabricated and how will it be assembled? Both of these will affect cost and reliability.

- 4. Place with flow planning for routing in mind.

- 5. Each design has its own restriction and requirements. And each design is a new challenge. Communicate with the team and gather all information (mechanical, environmental, SI, PI).

#### ITI & IPC Conference on Emerging & Critical Environmental Product Requirements

June 3 • BOSTON, Massachusetts June 5 • CHICAGO AREA, Illinois June 7 • SAN JOSE, California

It is a continuing challenge to stay current on global environmental regulations and issues such as:

- EU Circular Economy Strategy

- EU RoHS

- REACH Directive

- EU Plastics initiatives

- Asia environmental restrictions

- California Proposition 65

That is why IPC and ITI are again joining forces to help keep you ahead of the curve and connect you with leading industry speakers, update you on the latest trends and offer networking opportunities at the <u>2019 Emerging & Critical Environmental</u> <u>Product Requirements Conference</u>.

This conference will provide anyone who is responsible for keeping their organization in compliance with environmental regulations the tools they need to comply with legal, regulatory, and customer requirements.

**<u>Register today</u>** and stay ahead of the curve on the changing state of global environmental regulations!

For more information, contact **Ken Schramko**, IPC senior director of North American government relations, at <u>KenSchramko@ipc.org</u>.

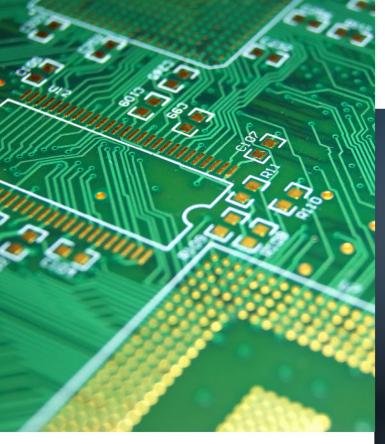

## High-speed PCB Design Constraints

#### **Beyond Design** Feature Column by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

Digital design has entered a new realm. Modern high-speed design (HSD) not only requires the designer to continuously break new ground on a technical level but also requires the designer to account for significantly more variables associated with higher frequencies, faster transition times, and higher bandwidths. Ignoring signal and power integrity and electromagnetic compatibility invites schedule delays and increases development costs and the possibility of never succeeding to build a functional product, which is a career-limiting strategy.

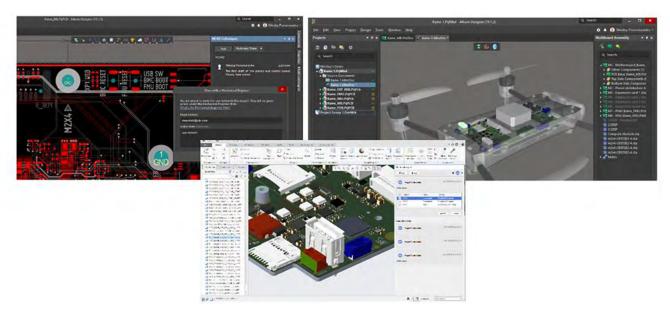

The key methodology is to understand the underlying high-speed design issues and then translate these into corresponding design constraints that will be adhered to during the entire design process. It is best to develop these high-speed design constraints based on prelayout simulation (Figure 1).

We had a few critical nets to manage in the past, but now, it seems that a significant number of interconnects are critical. Also, each design requires a specific set of constraints based on the technologies used. Sure, we can port basic design rules for trace width, clearance, etc., from a previous design to the next, but individual constraints still need to be established. Constraint reuse is also limited by net and group naming conventions. If you are consistent, then porting is much easier.

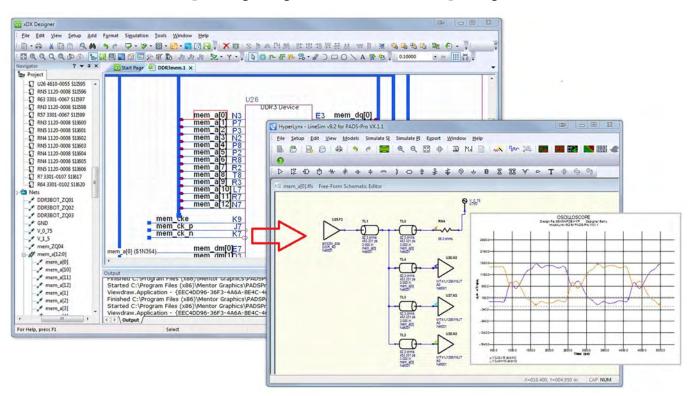

Figure 1: Develop high-speed design constraints based on pre-layout simulation (xDX Designer to HyperLynx).

#### 22 DESIGNO07 MAGAZINE I MAY 2019

## Candor Circuit Boards

## Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

#### www.candorind.com | (416) 736-6306

To begin with, every designer needs a set of well-established design rules to base the constraints on. IPC has provided the electronics industry with guidelines for designing and manufacturing PCBs compiled over the years with the support of both committee and industry members.

The IPC-2220-FAM: Design Standard for Printed Boards series is the bible for PCB designers. The series is built around IPC-2221B the base document that covers all generic requirements for PCB regardless of materials. From here, the designer chooses the appropriate sectional standard for a specific technology.

The IPC-2220-FAM series includes:

- IPC-2221B: Generic Standard on Printed Board Design

- IPC-2222A: Sectional Design Standard for Rigid Organic Printed Boards

- IPC-2223C: Sectional Design Standard for Flexible Printed Boards

- IPC-2224: Sectional Standard for Design of PWBs for PC Cards

- IPC-2225: Sectional Design Standard for Organic Multichip Modules (MCM-L) and MCM-L Assemblies

- IPC-2226A: Sectional Design Standard for High-density Interconnect (HDI) Printed Boards

This series provides coverage on material and final finish selection, current-carrying capacity and minimum electrical clearances, testspecimen design, guidelines for V-groove scoring, dimensioning requirements, and conductor thickness requirements.

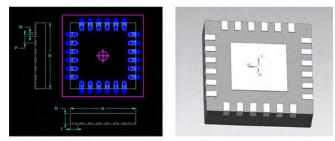

Also, several documents apply to HSD and land-pattern design:

- IPC-2141A: Design Guide for High-speed Controlled Impedance Circuit Boards

- IPC-2251: Design Guide for Electronic Packaging Utilizing High Speed Techniques

- IPC-7351B: Generic Requirements for Surface Mount Design and Land Pattern Standard

These standards (and their predecessors)

have been part of a well-used section of my technical library since 1987. They provide excellent reading and reference material for all PCB designers. These documents are available for purchase from www.ipc.org.

Design rules must keep up with the latest devices and fabrication processes without losing sight of design for manufacturability (DFM). DFM is the practice of designing board products that can be produced in a cost-effective manner using existing manufacturing processes and equipment. If you follow the above IPC guidelines, you will be designing for both manufacturability and mass production. However, at times, one must stretch the rules a little to meet the specific requirements of a design. This is fine, providing you can justify the reasons and tolerate the consequence of your decision.

Entry-level EDA tools tend to rely on the skills of the PCB designer to detect possible issues as they arise during the design process. However, these days, a more constraint-driven, correctby-construction approach is required for complex designs. Once the rules are established, they will be followed by downstream tools and validated to conform by the various design rule checkers (DRCs). A spreadsheet format is more efficient if you are dealing with a high volume of constraints, sorting, filtering, and duplicating constraints.

Constraint management:

- Enables better synchronization between schematic and layout

- Streamlines access to relevant PCB data

- Eliminates errors due to data integrity issues

- Promotes greater reuse of PCB data

Figure 2 illustrates typical constraints planning and definition for a high-speed DDR2 and DDR3 design. Constraints should be defined at the schematic level and flow through to the layout process. The advantage of this approach is that the engineer can convey their intent to the PCB designer without misinterpretation. Alternatively, the independent engineer (who does everything) can manage the constraints

| <b>▼</b> ‡ ×                                    | / Constraint Class/Net | # Pins | Net Class          | Topology |         |

|-------------------------------------------------|------------------------|--------|--------------------|----------|---------|

| Schemes<br>Net Classes                          |                        |        |                    | Туре     | Ordered |

| Default)                                        | 田 跡 (All)              |        | (Default)          | MST      | 1       |

| DR2_Addr_Cntrl                                  | 🕀 汭 DDR2               |        | (Default)          | MST      | 1       |

| DR2_Clocks                                      | 🗄 🦮 DDR2_Unused        |        | (Default)          | MST      |         |

| DR2_Data<br>DR2_Strobes                         | 🖻 🦄 DDR3               |        | (Default)          | MST      |         |

| dr3_address                                     | 🕀 🦮 Address            |        | ddr3_address       | MST      |         |

| dr3_clocks                                      | 🕀 🦮 clocks             |        | ddr3_clocks        | Chained  | . L.    |

| dr3_control                                     | 🗄 🦮 control            |        | ddr3_control       | MST      |         |

| dr3_extra                                       | 🗆 🦮 Data               |        | (Default)          | MST      |         |

| dr3_group0<br>dr3_group1                        | 🕀 🦮 Group0_1           |        | (Default)          | MST      |         |

| dr3_group2                                      | 🕀 🦮 Group2_3           |        | (Default)          | MST      |         |

| dr3_group3                                      | ExpoDemoAnalog3v_(All) |        | ExpoDemoAnalog3v_( | MST      |         |

| lff                                             | ExpoDemoPower0_9_(All) |        | ExpoDemoPower0_9_( | MST      |         |

| xpoDemoAnalog3v_(Defa.                          | ExpoDemoPower_(All)    |        | ExpoDemoPower_(Def | MST      |         |

| xpoDemoPower0_9_(Defa<br>xpoDemoPower_(Default) | 🕀 🦮 fs_addr            |        | (Default)          | MST      |         |

| ind                                             | 🕀 🦮 fs_data            |        | (Default)          | MST      |         |

| CI_Diffpairs                                    | 🕀 🦮 mictors            |        | (Default)          | MST      |         |

| CI_RX_Diffpairs                                 | PCI_Express            |        | PCI_Diffpairs      | MST      |         |

| CI_TX_Diffpairs                                 | Power_0_9_(All)        |        | (Default)          | MST      |         |

| ower<br>pecial                                  | Power_1_5_(All)        |        | ExpoDemoPower_(Def | MST      | 1       |

| rances                                          | Power_1_x_(All)        |        | (Default)          | MST      |         |

| traint Classes                                  | Power_3_0_(All)        |        | ExpoDemoAnalog3v_( | MST      |         |

|                                                 | E >>> Power_3_x_(All)  |        | (Default)          | MST      |         |

Figure 2: Constraints planning at the schematic level (PADS Professional).

throughout the design process using the same consistent management tool. Also, the reuse of constraints from a previous proven design not only ensures consistent rules but also minimizes the possibility of errors.

Net classes are used to organize and speed up the definition of routing constraints for nets with similar properties. For each net class, the layers allowed for routing, the corresponding trace width range for these layers, and the via types allowed can be defined. For differential pairs, a layer-dependent differential pair gap can be defined based on the calculated impedance to ensure uniform impedance across all layers.

The proper grouping and definition of net classes and constraint classes in the early stages of the design process simplifies constraint definition and management significantly. Grouped constraints can increase layout efficiency, reducing design time, and, ultimately, lower PCB design costs.

With DDRx design, it is also a requirement to assign layer sets to data lanes/strobes and ad-

dress, command, and control (ACC) and their associated clocks to ensure matched propagation delay. Signals within a group should be routed on the same layer with each path having the same via count. Even if the trace widths are adjusted on each layer, so as the impedance is identical, the propagation speed of microstrip (outer layer) is always faster than stripline (inner layer), typically by 13–17% (Figure 3). The speed of propagation of digital signals is independent of trace geometry and impedance and is solely determined by the dielectric constant of the material the electromagnetic energy propagates in.

The higher the signal frequency with which the designer must contend, the more complicated will be the PCB design. Complex PCB designs require deep knowledge and experience and simulation tools. However, it is not always necessary to route traces as short as possible, differential signals as close as possible, or to avoid crosstalk as much as possible. Rather, it depends on the signal's significance. Basically, the designer must know which are the sensi-

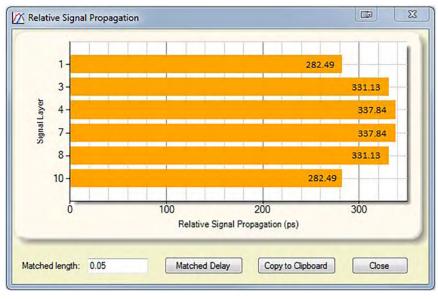

Figure 3: Relative signal propagation of microstrip and stripline (iCD Design Integrity).

tive parts in the circuit or where problems due to reflections and crosstalk can occur. With this knowledge, good placement of the devices can be made. Because placement is such an important step in high-speed design, the designer will do well always to keep it and the return current in mind.

With higher frequencies and faster transition times, the digital system timing budget is also of the utmost importance. The timing budget is the account of timing requirements necessary for a system to function properly. For synchronous systems to work, timing requirements must fit within one clock cycle. A timing budget calculation involves many factors, including setup and hold time and maximum operating frequency requirements. By calculating a timing budget, the limitations of conventional clocking methods can be seen. This data can then be translated into routing design constraints.

The first step in establishing the timing budget is to define the initial system timings. To do this, one must obtain estimates of the minimum and maximum output skew from the silicon vendors. This information is generally available in the IC datasheets. Then, define the setup and hold times for the read and write cycles. The timing budget for each component is then calculated given a certain margin. Whatever is left over (if anything) can then be allocated to the boardlevel interconnect design. This is the only factor that PCB designers can influence. If there is no margin left for the interconnect, then the silicon numbers need to be retargeted, or an easier solution might be to decrease the clock speed. This is why a shoddy design may work at a low frequency but not at full speed. Timing is everything in high-speed design.

In conclusion, PCB designers need to understand the underlying high-speed design issues of the design based on simulation and then translate these

into corresponding design constraints. Constraints can always be altered on the fly if a particular constraint is too tight, providing the designer can justify the easing of the specification and that the product is still manufacturable.

#### **Key Points:**

- The key methodology is to understand the underlying high-speed design issues and then translate these into corresponding design constraints

- High-speed design constraints are based on pre-layout simulation

- Constraint reuse is limited by net and group naming conventions; if you are consistent, then porting is much easier

- IPC has provided the electronics industry with guidelines for designing and manufacturing PCBs

- Entry-level EDA tools tend to rely on the skills of the PCB designer to detect possible issues as they arise during the design process

- A constraint-driven, correct-by-construction approach is required for complex designs

- Constraints should be defined at the schematic level and flow through to the layout process

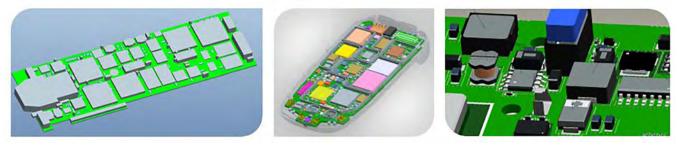

### Integrated Tools to Process PCB Designs into Physical PCBs

Minimize costs in both PCB fabrication and assembly through maxiumum panel usage.

Quickly and easily specify the PCBs form, fit and function.

Use manufacturing data to generate a 3D facsimile of the finished product.

Ensure that manufacturing data is accurate for PCB construciton.

Verify

Verify and Optimize PCB Designs for Successful Manufacturing

Create Comprehensive Documentation to Drive Fabrication, Assembly & Inspection

800-535-3226 | downstreamtech.com ©2019 DownStream Technologies, Inc. All rights reserved.

- The proper grouping and definition of net classes and constraint classes in the early stages of the design process simplifies constraint definition and management significantly

- The propagation speed of microstrip (outer layer) is always faster than stripline (inner layer), typically by 13–17%

- The speed of propagation of digital signals is independent of trace geometry and impedance and is solely determined by the dielectric constant of the material

- The designer must know which are the sensitive parts in the circuit or where problems due to reflections and crosstalk can occur

- The timing budget is the account of timing requirements necessary for a system to function properly

- The timing budget shows the limitations of conventional clocking methods and can then be translated into routing design constraints **DESIGN007**

#### **Further Reading**

• Olney, B. "Beyond Design: The Need for Speed–Strategies for Design Efficiency," *The PCB Design Magazine*, March 2016. • Olney, B. "Beyond Design: Design Rules and DFM for High-speed Design," *The PCB Magazine*, June 2012.

• Olney, B. "Beyond Design: Signal Flight Time Variance in Multilayer PCBs," *The PCB Design Magazine*, December 2017.

• The IPC-2220-FAM: Design Standard for Printed Boards series, www.ipc.org.

• Hughes, S. "Why Impose Design Constraints?" Mentor, a Siemens Business.

• Martens, J. "How to Handle PCB Design Constraints Without Losing Your Mind," Mentor, a Siemens Business.

• Hall, S. W., Hall, G. W., & McCall, J. A. High-speed Digital System Design: A Handbook of Interconnect Theory and Design Practices, Wiley, 2000.

• Johnson, H., & Graham, M. *High-speed Signal Propa*gation: Advanced Black Magic, Prentice Hall, 2003.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in boardlevel simulation. The company developed the iCD Design Integrity software incorporating the

iCD Stackup, PDN, and CPW Planner. The software can be downloaded from www.icd.com.au. To read past columns or contact Olney, click here.

#### **The First Walking Robot that Moves Without GPS**

Researchers at CNRS and Aix-Marseille University (AMU), in the Institut des Sciences du Mouvement—Étienne Jules Marey (ISM), have designed the first walking robot that can move without GPS: AntBot.

Inspired by desert ants—which are considered extraordinary solitary navigators—AntBot can explore its envi-

ronment randomly and go home automatically without GPS or mapping.

Ants use polarized light and ultraviolet radiation to locate themselves in space. Cataglyphis desert ants, in particular, can cover several hundreds of meters in direct sunlight in the desert to find food, then return in

a straight line to the nest without getting lost. Distance and heading are the two fundamental pieces of information that, once combined, allow them to return smoothly to the nest.

AntBot is equipped with an optical compass used to determine its heading by means of polarized light, and an optical

> movement sensor directed to the sun to measure the distance covered. Armed with this information, AntBot has been shown to be able to explore its environment and to return on its own to its base with a precision of up to one cm after having covered a total distance of 14 m.

(Source: French National Centre for Scientific Research)

## WHAT DO ALL OF THESE LEADING COMPANIES HAVE IN COMMON?

#### They all benefit by advertising with us-PCB007 China Magazine. Should your name be on the leaders' list?

pcb007china.com

Altium's Craig Arcuri on Design Rules: Past, Present, and Future

#### Feature Interview by the I-Connect007 Editorial Team

We recently spoke with Altium's Craig Arcuri about his views on design and manufacturing rules. Craig has experience running both design and manufacturing companies, so he has a fairly circumspect view of constraints from both sides of the product realization\_process. In this interview, Craig details some of the challenges with setting and managing hundreds of often divergent design and manufacturing rules, and how both design and manufacturing constraints need to evolve to better serve all of the stakeholders in PCB design.

**Andy Shaughnessy:** Craig, there seems to be a lot of disagreement about design and manufacturing rules, and it seems that there's not much agreement on best practices. It's very fragmented, and everyone does design rules their own way. As an EDA tool company guy, what are users asking you all for regarding design rules?

**Craig Arcuri:** Let me give you a different perspective. Of the last three companies I ran, one was a design company that did engineering design

and used CAD tools to create data that was then passed on to manufacturing. Although we tried to care, and said we cared, we really didn't worry about what happened after we sent the data out because that was somebody else's problem. Then it was poetic justice that my last two companies were manufacturing companies that had to deal with those folks who didn't really worry about what happened after the handoff to manufacturing!

You know the phrase "poop rolls downhill." Well, the manufacturing folks are pretty close to the bottom. At the end of the day, the engineer and layout person have done their job, and a big pile of data comes down and lands on manufacturing. My job is to make a physical thing in less time with less money at a higher quality than is probably reasonably possible given the pile of poop that I was given. Over the course of the last 10 years, I've seen 200–300 unique customers per quarter send the data to the manufacturing people, from the perspective of being close to the bottom.

Some of the data comes from companies like Google, Tesla, Intel, and Microsoft. You might think that those companies would provide pristine data and that the design rules would be absolutely well-defined, followed, and imple-

#### Your signal needs to get around the world fast... Why go halfway around the world to get your high-speed PCBs?

## ACE: your high-speed experts right here at home, specializing in microwave and hybrid PCBs.

Accurate Circuit Engineering 3019 Kilson Dr Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: James Hofer (714) 227-9540

www.ace-pcb.com

RoHS & WEEE compliant • Certified AS9100, ISO, ITAR, MIL-PRF-31032 & 55110

Craig Arcuri

mented in the design EDA tool, and translated through the software into a package where I would think, "This is going to be a piece of cake. What am I going to do with all the money I'm going to make?"

You might also assume that the little guys come across with data out of CAD tools like Eagle and KiCad where a consistent database is a thing of dreams, and it's a bunch of disconnected data that may or may not have any sanity to it. But you would be sadly mistaken. Across the board, manufacturers rarely receive a data package where manufacturing rules have been considered, adhered to, or worked around, and where the data has been presented in a way that shows that. The instructions are almost never clear and the board can't always be built.

Now, I won't put all of the blame on the designer or engineer. If you look at companies like Apple or Samsung, they expect most of the products they design to go into volume production very quickly. Regardless of their size, companies that expect a product to go in volume production clearly consider design rules and manufacturing issues during the design process. They "design for manufacturing," as opposed to "design with manufacturing."

But everybody else typically has a designer or an engineer in front of a computer screen. And it's not that they don't want to know more about manufacturing. It's not that they want to choose components that are hard or impossible to get or will be impossible to reflow because of their mass. They're not doing that on purpose, but part of it is that they're busy. They have a job to do, and that job is to create the electronic design and capture it in a CAD tool as quickly as possible and get that prototype to a manufacturer to build so that it can be validated back in the labs.

The engineers are never going to have time to understand the nuances of why a tall electrolytic capacitor next to an 0603 is going to have a shadow effect when it gets reflowed. For decades, manufacturers have beat on customers, I've been one of them, saying, "Please involve me earlier. I can consult with you, explain what things are important, and look at the designs as you do them."

Then, commercial reality comes in. At some point, a quote is given, and generally, customers don't want to involve a manufacturer early for commercial reasons because that would mean they'd be locked in. The only way we're going to have to solve that is with smart software that aims more at designing with manufacturing in mind so that the tools evolve in a way that is far beyond where they are today.

**Shaughnessy:** We've heard that before about how software needs to evolve, and some people see a role for AI. Do you think AI will be a part of this evolution?

**Arcuri:** Absolutely. And I'll say one more thing while I'm standing on my soapbox. I think DFM is the stupidest thing ever. I know, I've just said heresy (laughs). The layout is completed by a designer and the CAD tools. Then, the data is sent to a fabricator, and while the design is being cast in concrete, fiberglass, or resin, the data is sent to an assembly shop so that they can do DFM.

Well, what good is that? All I'm going to do with the DFM is learn what problems I'm going to have to solve on the manufacturing floor because it's already baked in concrete. I can't go back and say, "Stop the fabrication and start over again. Move that BGA 300 mils to the left so that it's not right on the edge of the board and won't need fixtures to run it down the line." I don't have that option. DFM is really just a preemptive alert for the manufacturing engineers to say, "This is the pile of crap that's heading in your direction, so figure out how to build it, and you can't change anything. Too bad." We have all of these rich CAD tools with lots of information about constraints, land sizes, via holes, and annular rings, and then we reduce that rich data down to Gerber data, which is about as dumb as a post, or ODB++, which is more intelligent.

Then, we give it to a fabricator and an assembly shop. In that whole process, I don't believe the humans and business paradigms involved are going to evolve in such a way that this can be done collaboratively. Due to commercial and technical reasons and how busy everybody is, I can't make a designer understand everything a manufacturing engineer knows and vice versa. The only place left to go is the software. We can create a software paradigm where this stuff happens in parallel. We have to.

**Happy Holden:** We've had that for 20 years in integrated circuit design.

**Arcuri:** Exactly! The parallels to that are shockingly obvious. I'm in love with whoever said that (laughs).

**Nolan Johnson:** That's a good one, Craig. Happy and I have IC backgrounds too. The PCB design tool flow seems to be 10–20 years behind where IC was. IC has been driven by huge monetary constraints to getting to silicon, which then forced the discipline that isn't present in PCB right now. Instead of having three shops and a \$60,000 price tag for getting your first silicon, you're looking at a few hundred bucks at any one of 800 shops.

**Arcuri:** That's a very good point. The capital requirements for an IC factory are grossly large. There are 400–500 medium to small CMs in North America alone competing for all of this business. It's such a fragmented market, and it's not driven by the turn time. The cost of spinning an IC is astronomical compared to, "If we have to relay out the board and fabricate another board and simplify it more, that's not going to kill us." We're preaching to the choir.

**Johnson:** Let's take that complexity and add another layer because there are some trends going on here. We have that sort of complexity going on plus new design constraints that are coming all the time. There are so many specialized functions. You can't expect one designer to master them all, so how do the tools help them?

**Arcuri:** I've always wanted to know so much about something that I could call myself a thought leader in a subject area without laughing at myself, and I'm still looking for that thing. I am a pilot and am pretty good at flying, but to the extent that I am old now and have a lot of experience. Globally, we are embracing more and more collaboration across all walks. With the gig economy and services like Uber where software applications connect a

#### Globally, we are embracing more and more collaboration across all walks.

customer with a seller, there's a piece of technology in the middle that facilitates that. People use the Uber analogy a lot, but the idea is that the devices we have are much more powerful and portable. We are much more comfortable, although it might be scary to many of us, with our data being someplace in the Cloud. Because when it's in the Cloud, it's a lot easier to create collaborative experiences because everybody can access it.

| 💼 Design Rules                                 | Name                      | Priority | Enabled  | Туре                          | Category      | Scope              | Attributes                   |

|------------------------------------------------|---------------------------|----------|----------|-------------------------------|---------------|--------------------|------------------------------|

| Electrical                                     | AssemblyTestpoint         | 1        |          | Assembly Testpoint Style      | Testpoint     | All                | Under Comp - Allow Sides     |

| ✓ Tearance                                     | AssemblyTestPointUsage    | 1        | ~        | Assembly Testpoint Usage      | Testpoint     | All                | Testpoint - One Required     |

| Clearance                                      | Clearance                 |          | 9        | Clearance                     | Electrical    | All - All          | Generic clearance = 10mil, a |

| Short-Circuit                                  | ComponentClearance        |          | 8        | Component Clearance           | Placement     | All - All          | Horizontal Clearance = 10m   |

| Un-Routed Net                                  | DiffPairsRouting          |          | 9        | Differential Pairs Routing    | Routing       | All                | Pref Gap = 10mil Min Gap     |

| 0 Un-Connected Pin                             | FabricationTestpoint      |          |          | Fabrication Testpoint Style   | Testpoint     | All                | Under Comp - Allow Side      |

| Modified Polygon                               | FabricationTestPointUsage |          |          | Fabrication Testpoint Usage   | Testpoint     | All                | Testpoint - One Required     |

| Routing     SWidth                             | Fanout_BGA                |          |          | Fanout Control                | Routing       | IsBGA              | Style - Auto Direction - A   |

| Width                                          | Fanout_Default            |          |          | Fanout Control                | Routing       | All                | Style - Auto Direction - A   |

| A SRouting Topology                            | Fanout LCC                | 2        |          | Fanout Control                | Routing       | ISLCC              | Style - Auto Direction - A   |

| RoutingTopology                                | Fanout Small              | 4        |          | Fanout Control                | Routing       | (CompPinCount < 5) | Style - Auto Direction - O   |

| Routing Priority                               | Fanout SOIC               | 3        | ×.       | Fanout Control                | Routing       | ISSOIC             | Style - Auto Direction - A   |

| Routing Layers                                 | Height                    | 1        |          | Height                        | Placement     | All                | Pref Height = 500mil Min     |

| Routing Corners                                | HoleSize                  |          | 2        | Hole Size                     | Manufacturing | All                | Min = 1mil Max = 100mil      |

| A == Routing Via Style                         | HoleToHoleClearance       |          | ¥.       | Hole To Hole Clearance        | Manufacturing | All - All          | Hole To Hole Clearance =     |

| RoutingVias                                    | LaverPairs                |          |          | Laver Pairs                   | Manufacturing | All                | Laver Pairs - Enforce        |

| Fanout Control                                 | MinimumSolderMaskSliver   | 1        | ×.       | Minimum Solder Mask Sliver    | Manufacturing | All - All          | Minimum Solder Mask Sliv     |

| <ul> <li>Differential Pairs Routing</li> </ul> | 7 NetAntennae             |          | 26       | Net Antennae                  | Manufacturing | All                | Net Antennae Tolerance =     |

| DiffPairsRouting                               | PasteMaskExpansion        |          | 1        | Paste Mask Expansion          | Mask          | All                | Expansion = Omil             |

| SMT                                            | PlaneClearance            |          | ×.       | Power Plane Clearance         | Plane         | All                | Clearance = 20mil            |

| Mask                                           | PlaneConnect              |          | 2        | Power Plane Connect Style     | Plane         | All                | Style - Relief Connect Exp   |

| Plane                                          | PolygonConnect            |          | 2        | Polygon Connect Style         | Plane         | All - All          | Style - Relief Connect Wi    |

| Testpoint                                      | RoutingCorners            |          | 10       | Routing Corners               | Routing       | All                | Style - 45 Degree Min Set    |

| Manufacturing                                  | RoutingLayers             |          | ž.       | Routing Layers                | Routing       | All                | TopLayer - Enabled Bottom    |

| High Speed                                     | RoutingPriority           | 4        |          | Routing Priority              | Routing       | All                | Priority = 0                 |

| Parallel Segment                               | RoutingTopology           |          | -        | Routing Topology              | Routing       | All                | Topology - Shortest          |

| Length                                         | RoutingVias               |          |          | Routing Via Style             | Routing       | All                | Pref Size = 50mil Pref Hol   |

| Matched Lengths<br>Daisy Chain Stub Length     | ShortCircuit              |          |          | Short-Circuit                 | Electrical    | All - All          | Short Circuit - Not Allowed  |

| Vias Under SMD                                 | SilkToSilkClearance       | 1        |          | Silk To Silk Clearance        | Manufacturing | All - All          | Silk to Silk Clearance = 10r |

| Maximum Via Count                              | SilkToSolderMaskClearance |          |          | Silk To Solder Mask Clearance |               | IsPad - All        | Silk To Solder Mask Cleara   |

| Max Via Stub Length (Back Drilling)            | SolderMaskExpansion       |          |          | Solder Mask Expansion         | Mask          | All                | Expansion = 4mil             |

| Placement                                      | UnpouredPolygon           | -        | ×.       | Modified Polygon              | Electrical    | All                | Allow modified - No Allow    |

| Signal Integrity                               | UnRoutedNet               |          | R        | Un-Routed Net                 | Electrical    | All                | (No Attributes)              |

|                                                | Width                     |          | 8        | Width                         | Routing       | All                | Pref Width = 10mil Min V     |

|                                                | New Rule Delete R         | ule(s)   | Duplicat | e Rule Report                 |               |                    |                              |

| le Wizard Priorities Create De                 |                           |          |          |                               |               |                    |                              |

The Altium design rules editor.

It's not a case of FTPing or emailing files. We're all looking at the same thing, so that evolution is an enabler for companies like Altium to look at this very fragmented process and say, "We can't solve it all at once, but how can we start bringing pieces together?" I'm sure we're not the only ones, but we're feverishly working on things in our R&D area to create platforms that allow different functions and software tools to interact in a very agnostic way, meaning it wouldn't matter what company you chose.

**Johnson:** Where do you see Altium's vision going for how to retool all of this? Were you alluding to Altium 365 as a starting point?

**Arcuri:** I was trying not to say that, so thank you for prying that out of me. Again, being a guy who was in the trenches at the last two companies I worked at, it didn't matter what went wrong; I was blamed because I was at the bottom of the hill—the manufacturers. I'm a big believer in not letting the marketing get too far ahead of the reality. You could look at some things that Altium has today that are public information and guess what we might do with that if we thought this problem we've been talking about was a big problem. We thought that there was a great business opportunity in helping to solve it, and we are.

For example, Octopart has a huge user following, and it's absolutely not centric to Altium. Components are one of the major irritants in our life because, from a manufacturing perspective, if I don't have them, I can't put them on the board. From a customer perspective, if I go to order them and can't get them because Cisco just designed that tantalum capacitor into a product, the worldwide supply just went down to zero. Everything to do with components—physically, electrically, and related to the supply chain—causes us lots of excitement in this industry.

We have a thing called Ciiva, which is interesting and CAD-nostic. I would like to be cred-

#### EIPC SUMMER CONFERENCE • LEOBEN, AUSTRIA Falkensteiner Hotel & Asia Spa Leoben

Alun Morgan, EIPC President