OCTOBER 2018

# Connect007

# DES GAZINE

# BREAKthe Design Data Bottleneck!

# Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

### View our eBook library

"Mark does an outstanding job detailing what needs to be included in the handoff from designer to fabricator. This book should be required reading for every designer."

Producing the Perfect Data Package

**Mark Thompson Prototron Circuits**

Douglas Brooks, Ph.D. THE PRINTED CIRCUIT DESIGNER'S GUIDE TO... **BS/MS EE**

Most of the design data packages that a fabricator receives contain inaccurate or incomplete data.

Don't be a data violator!

I-007eBooks.com/data

#### **OCTOBER 2018 • FEATURED CONTENT**

# DESIGNOOT MAGAZINE

### **Design Data Packages**

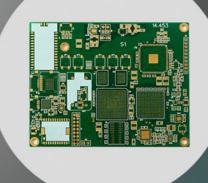

You've heard the stories. Most CAM departments say that anywhere from 80–100% of designs from new customers are inaccurate or incomplete, often necessitating a Friday afternoon call to the designer, or the job being put on hold. So, what can we do to optimize the design data package and make the handoff to the fabricator as smooth as possible? We asked a variety of industry experts to weigh in on this topic.

- 10 Steph Chavez: Breaking the Design Data Bottleneck Interview by Andy Shaughnessy

- 24 At GreenSource, Lean and Green Starts on the Front End Interview with JanNell Taylor and Andy Schilloff

- **30 Design Data: File Naming Conventions** by Kelly Dack, CID+, CIT

#### **FEATURE COLUMNS:**

- 18 Getting on the Same Page: A Data Story by Mark Thompson

- 36 Digital Specs for Automated Manufacturing: Finding the Missing Link! by Jan Pedersen

### Candor Circuit Boards

# Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

### www.candorind.com | (416) 736-6306

#### **OCTOBER 2018** • ADDITIONAL CONTENT

# DESIGNOOT MAGAZINE

### **SHORTS**:

- 9 New Half-Light Half-Matter Particles May Hold the Key to a Computing Revolution

- 16 Medication You Can Wear

- 23 Superconducting at the Speed of Light

- 29 Novel Topological Insulator

- 51 New NIST Method Measures 3D Polymer Processing Precisely

#### HIGHLIGHTS: 40 PCB007

- 64 MilAero007

- 78 Top 10 PCBDesign007

#### **DEPARTMENTS**:

- 81 Career Opportunities

- 88 Events Calendar

- 89 Advertiser Index & Masthead

#### **ARTICLES:**

- 66 New Designers Council Column: The Digital Layout Interview with Mike Creeden and Steph Chavez

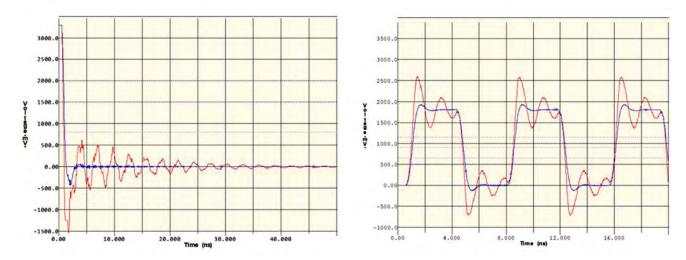

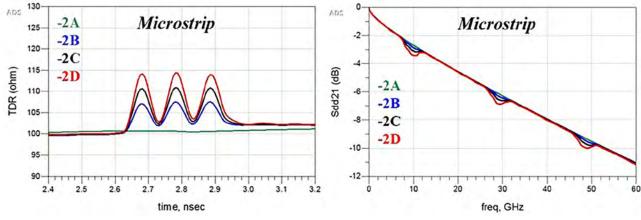

- 70 Impact of Serpentine Routing on Multi-gigabit Signal Transmission by Chang Fei Yee

#### **COLUMNS:**

- 8 Despite Progress, Design Data Issues Continue by Andy Shaughnessy

- 42 New Landing Design to Reduce Thermal Pad Failures by Bob Tise and Dave Baker

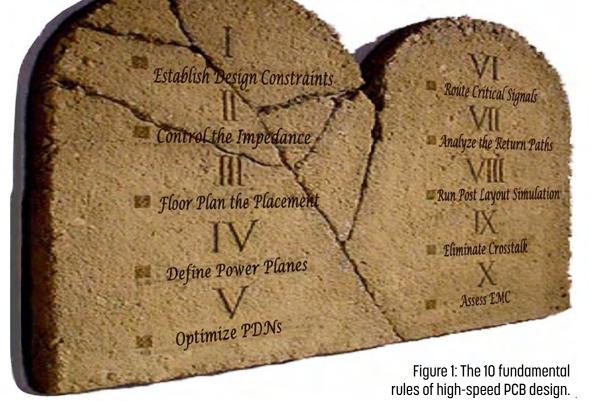

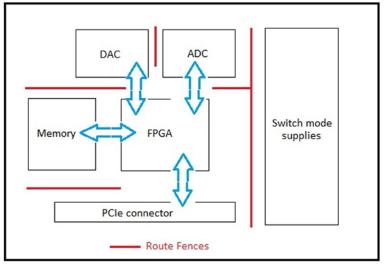

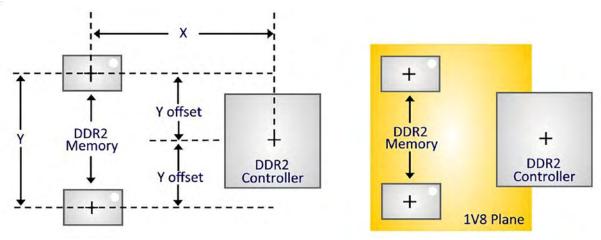

- 46 10 Fundamental Rules of High-Speed PCB Design, Part 2 by Barry Olney

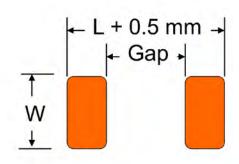

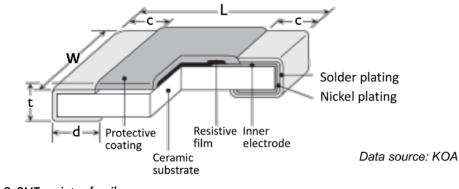

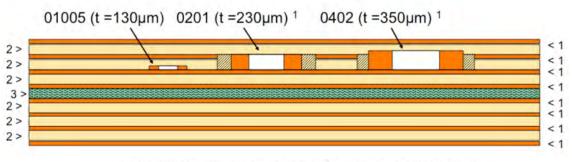

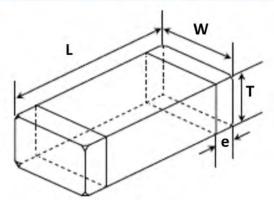

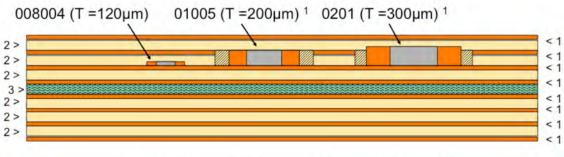

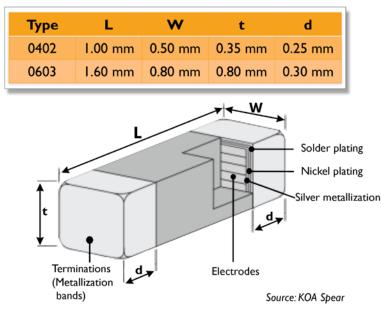

- 52 Embedding Components, Part 4: Passive Component Selection and Land Pattern Development by Vern Solberg

- 60 Different Aspects of Impedance for PCBs by John Coonrod

# A Siemens Business

### Speed up your PCB design verification by up to

### Get HyperLynx DRC for FREE for 12 months COMPATIBLE WITH ANY PCB LAYOUT TOOL!

www.mentor.com/get-drc

### Despite Progress, Design Data Issues Continue

#### The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

It seems so simple —you design a PCB, hand off the design to a fabricator, along with notes describing your design intent, and they manufacture the board. Everyone gets paid, and everyone's happy, right?

Wrong.

Much of the time, that's not how it works out—not even close.

You've heard the stories. Most CAM departments tell us (are they telling you?) that anywhere from 80–100% of designs from new customers are inaccurate or incomplete, often necessitating a Friday call to the designer, or the job will be put on hold.

This has been an ongoing problem for decades, and it doesn't seem to be getting any better—at least from the viewpoint of CAM personnel. The problem is so prevalent that columnist Mark Thompson has built quite an audience by writing about design data packages and sharing his treasure trove of horror stories about data gone wrong.

Most of you are not new to the industry, shall we say. Many of you have at least 30 years of experience designing PCBs. You've done this hundreds of times before. But why are we still seeing so many errors during the post-processing part of the design flow?

You might think that constant improvements to the Gerber, ODB++, and IPC-2581 data formats would make issues like this a thing of the past. However, much of the data package is still dependent upon the designer's ability to describe how they want the board built. It's the little things that trip up a design, such as failing to specify whether a quarter ounce of copper is the weight before or after processing.

Part of the problem is that CAM people often fix the error without telling the designer, so the designer never knows that there was a problem in the first place, which perpetuates the issue.

What can we do to optimize the design data package and make the handoff to the fabricator as smooth as possible? We asked a variety of industry experts to weigh in on this topic.

Steph Chavez, a CID instructor with EPTAC Corporation and IPC Designers Council Executive Board member, explains how designers can break the design data bottleneck, and why it's so critical that designers and fabricators stay in touch throughout the design cycle. Mark Thompson brings us a feature column that explains what fabricators would like to see in each design data package. (Shameless plug: This column details Mark's new I-Connect007 eBook, *The Printed Circuit Designer's Guide* to... Producing the Perfect Data Package.)

Next, CAM engineers JanNell Taylor and Andy Schilloff of GreenSource Fabrication discuss their preparation for the company's upcoming entry into the commercial market, and how they will be able to trigger jobs from their off-site location in a different state. Then, Kelly Dack, CID + , answers the old question, "What's in a name?" He discusses many of the ways that designers are inadvertently shooting themselves in the foot by assigning similar or confusing naming conventions to layers of artwork. We wrap things up with a feature by columnist Jan Pedersen of Elmatica who explains the need to move design data fully into the digital realm. As Jan says, "We're close, but we're still not quite there yet."

This month, we're introducing a brand-new column, "Connect the Dots," by Bob Tise and Dave Baker of Sunstone Circuits, as well as columns from our regular contributors Barry Olney, Vern Solberg, and John Coonrod. We also have an interview with Mike Creeden and Steph Chavez from the IPC Designers Council who discuss their upcoming column "The Digital Layout," which will launch next month.

If you don't already subscribe to *Design007 Magazine*, what are you waiting for? Click here to subscribe to our magazine and newsletters. See you next month! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 18 years. He can be reached by clicking here.

### New Half-Light Half-Matter Particles May Hold the Key to a Computing Revolution

Current computing technology is based on electronics, where electrons are used to encode and transport information.

Due to some fundamental limitations, such as energyloss through resistive heating, it is expected that electrons will eventually need to be replaced by photons, leading to futuristic light-based computers that are much faster and more efficient than current electronic ones.

Physicists at the University of Exeter have taken an important step towards this goal, as they have discov-

ered new half-light, half-matter particles that inherit some of the remarkable features of graphene, the so-called "wonder material."

This discovery opens the door for the development of photonic circuitry using

these alternative particles, known as massless Dirac polaritons, to transport information rather than electrons.

A unique feature of Dirac particles is that they mimic relativistic particles with no mass, allowing them to travel very efficiently. However, it is very difficult to control them. This fundamental drawback—the lack of tunability—has been successfully overcome in a unique way by the physicists at the University of Exeter.

"Our work has crucial implications for the research fields of photonics and of Dirac particles," adds Dr. Eros Mariani, principal investigator on the study. "We have

> shown the ability to slow down or even stop the Dirac particles, and modify their internal structure, their 'chirality' in technical terms, which is impossible to do in graphene itself."

(Source: University of Exeter)

### Steph Chavez: Breaking the Design Data Bottleneck

#### Feature interview by Andy Shaughnessy I-CONNECTO07

When we started planning this issue on design data, I knew we'd have to speak with Steph Chavez.

**Andy Shaughnessy:** Steph, can you tell us about your background? Then, we'll talk about what you are seeing and hearing regarding PCB design as a design instructor for EPTAC Corporation.

**Steph Chavez:** Sure. I hold a seat on the global IPC Designers Council (DC) Executive Board. I am my local area's IPC DC chapter president in Phoenix. I have about 28 years of experience in the industry. I've spent the last 15 years of my career as a lead designer successfully designing a wide spectrum of PCB designs—both simple and complex—including HDI, flex, and rigid-flex. I've also led global PCB design teams, which include managing diverse, multicultural teams in multiple time zones. The foundation of my education and leadership stems from my

time in service in the U.S. Marine Corps as an avionics technician. Whenever I'm speaking, I always stress that you should have plenty of knowledge resources in your "bag of magic," so to speak, This includes establishing your professional network, which I believe this is key for your overall success. I-Connect007 is a great resource of knowledge sharing and upto-date industry content.

**Shaughnessy:** We appreciate that. We like to publish information that designers can use right away. Speaking of which, one thing everybody was talking about at IPC APEX EXPO 2018 was data. The Design Forum hardly covered anything about how to design a board; it was all about data. You hear from fabricators that 90% of new customers submit design data packages that are incomplete or inaccurate. They don't provide an updated netlist, etc. You said that you've been dealing with a lot of data issues lately. Can you tell us about that?

**Chavez:** As a designer, when you think about the data you're presenting or handing off to

### Offshore pricing. Exceptional quality. Local service.

We strive for excellence in everything we say and do.

Our finger is on the pulse of the latest technologies, systems and solutions in an effort to be a total PCB solution provider for our customers.

#### Why choose Eagle as your total PCB provider:

- . Dedicated offshore team with local quality and engineering support

- Seamless transition from prototype to production

- . The same exceptional service and support that you've come to expect from Eagle

Click here to learn more about our offshore option

Steph Chavez

your suppliers, you should have a basic understanding of IPC standards because that is how you're going to communicate your intent to your fabricator and assembler. At the same time, you need to fully comprehend what you are giving to your suppliers and what you are stating in your fabrication and assembly drawings. Are you correctly stating vour fabrication or assembly notes? Do they make

sense? Do you have all the required information listed to fabricate your PWB or assemble your PWA successfully? Do you have statements in your drawings that conflict with one another and could cause confusion? Worse yet—and I feel this is the root of the problem—do you understand your company's documentation details, or are you just "rubber stamping" your documentation because "that's how it's always been done?"

These are some of the questions that come to mind when I think about bad data being handed off. Board design construction is key for success and getting the details correct is paramount. Many times, bad data is given because people are not paying attention to the details. Some designers simply don't know what they don't know and pass on bad data.

In my experience, when you get into production runs with a top-tier supplier, they will not change or modify your data without permission. If you send a job over to them with issues, concerns, or missing data, chances are it's going to be put on hold. By the time you receive any feedback that your job has been put on hold, it could be five or more days lost in a schedule before you can address these issues flagged by the supplier. For many companies, that's a huge negative hit. The sad thing is that this usually stems from something that could have been easily mitigated up front in the beginning stages of your design with the supplier. **Shaughnessy:** Communication is the key, as we keep hearing.

**Chavez:** Exactly. Let's discuss PWB classes, for example. If you don't have the requirements for Class III implemented in your design, but you ask the supplier to build to Class III, the supplier will kick your data back and say it's physically impossible and your board isn't designed correctly for it. Then what do you do? Find a board shop somewhere that can build it once if you're lucky, or do you go back and redesign your board appropriately for a Class II design? That's why it's paramount that you understand IPC specifications and bring in your fabricator at the beginning stages of the design process. You should discuss stackups and all the details that make up your board depending on if it's a Class II or III design. This is one piece of information you need to know before starting-not something you find out afterward when your design is finished.

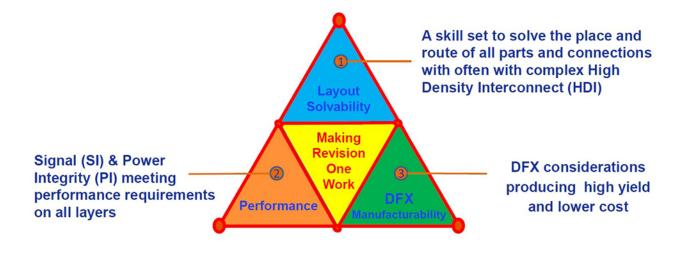

By engaging your suppliers early in the design stage, you'll ensure that everything aligns, is cohesive, and meets the basic industry IPC standards to make the smoothest transition from design to fabrication, assembly, and test. The transitions could be from you as a designer to the manufacturer, or from the fabricator to the assembler, with the least amount of resistance. Then everything is optimized. This is why three perspectives have been identified for a successful design that must be met: layout solvability, performance (routing solvability that includes signal and power integrity), and DFX (manufacturability). I refer to this as the "Designer's Triangle." The end result is making the first revision work!

**Shaughnessy:** We keep hearing CAM departments complain about receiving bad data—even from senior designers who know how to design a complex board.

**Chavez:** Just because someone has a senior designer title doesn't mean they truly comprehend what they are doing or are paying attention to all the details. I've come across design-

#### Today's Designer must meet 3 Perspectives for Success

THE RESULT

Maximum placement and routing density, optimum electrical performance and efficient, defect-free manufacturing

Figure 1: The "Designers Triangle."

ers with many years of experience in my career that have bad habits. Bad habits are major contributors to bad data being supplied to the fabricator. I know from experience and from discussions with my fellow IPC CIT instructors that there are seasoned veterans with many years of experience and complex designs under their belt who fail the IPC CID or CID + certification courses. These senior designers tend to get caught up in their own world, or worse, become legends in their own mind. They think they know everything and don't continue their professional development. Over time, the fabricator bails them out by catching their mistakes from the feedback of the CAM engineers, as you mentioned.

**Shaughnessy:** I'll often ask designers if they regularly speak with their fabricators, and a lot of them say they never do because they don't know who's going to build it. They don't know who will do the prototypes or build production volumes overseas. Instead, they output in Gerber and Valor—so they're fairly safe—and then they wait for the call about what's wrong.

**Chavez:** You're absolutely right, when it comes to many companies and how they procure boards. Sometimes you don't know who is building your board. Generally, if you follow IPC standards, you'll minimize your overall risk. You should design your PWBs per IPC standards at a minimum, then no matter where it's fabricated or who is fabricating it, you will have success. When you start deviating from IPC standards, negative issues begin to present themselves. This is why communication is key. To achieve overall success and make revision one work, you should design your board per IPC standards at a minimum. If you do this, your designs will have a much lower risk going into fabrication, and you'll end up with a positive result.

I'm flabbergasted as to why many designers don't pick up the phone and call their supplier. You and your supplier should be on a first-name basis. You don't want to guess in this game.

Recently, I've done some research on outputs regarding data formats. Which output should be the primary output for suppliers— Gerber along with IPC-D-356 netlist, ODB++, or IPC-2581 data? Which is the preferred format? I gathered information from many suppliers throughout the U.S. as well as globally.

**Shaughnessy:** What did you find during your research?

**Chavez:** It was amazing to find out that it was not consistent from one supplier to another, or even consistent within a global supplier that has many divisions throughout the world. One division of a large top-tier company preferred Gerber data along with an IPC-D-356 netlist, while another division of the same company on the other side of the world preferred ODB++ data. That particular division even provided discounts for sending ODB++ data over any other format. When I received the feedback, I thought, "You're all the same company, so why aren't you on the same page and preferring the same data throughout all your divisions?"

From my initial research, it appears that there more people accept ODB++ data over IPC-2581 at this time. However, my research also pointed out that Gerber data along with an IPC-D-356 netlist was still the leading data format that most suppliers prefer. Yes, both ODB++ and IPC-2581 data formats provide more intelligent content that you'd prefer to

### That is what makes those formats better and more powerful to use, but not everybody is accepting these formats.

share instead of Gerber data. Those intelligent formats have everything you need for both fabrication and assembly all in one dataset package. That is what makes those formats better and more powerful to use, but not everybody is accepting these formats.

Let's say you go digital with one of these intelligent data formats and send it out to your

long-term supplier. What do you do when your supplier says, "I'm sorry, I can't use this data format. I don't have that capability. I'd prefer to have that Gerber data along with an IPC-D-356 netlist you've been supplying me all these past years." Do you stop using that supplier and toss aside all the years of establishing relationships and successfully working with them to find a new one? If you work for a large corporation-and believe me, I have experience at several of them-it's not that easy to jump from one supplier to another, especially if getting on a company's approved vendor's list (AVL) is already tough due to required restrictions and certifications that those suppliers need to have in place. Thus, you end up going back to Gerber data along with an IPC-D-356 netlist until your suppliers update their capabilities as well.

As I said, I was amazed at the feedback I received. Gerber data along with an IPC-D-356 netlist was still the leading data format preferred in the industry when it comes to PWB fabrication.

**Shaughnessy:** Right. You've probably seen the surveys showing that 95% of designs are still generated in Gerber.

**Chavez:** Yes, I have. I was stunned at the response I received when I was onsite at one top-tier supplier and asked about what data format they prefer. They preferred Gerber data and an IPC-D-356 netlist because they take the supplied Gerber data and an IPC-D-356 netlist and generate an internal ODB++ file. I asked, "What if I eliminate that extra step in the process and provide you the ODB++ file directly from my Mentor software?" They responded, "No, we prefer to receive Gerber data and an IPC-D-356 netlist because we have a solid process in place that is effective and optimized to our internal processes." We still supply them with Gerber data along with an IPC-D-356 netlist.

**Shaughnessy:** Even though it would be messy to change over, I'm surprised that the industry hasn't locked into one data format.

# VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

### **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

©2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

### Visit downstreamtech.com or call 800-535-3226

**Chavez:** What it comes down to is that companies want to be successful. It's not easy to change internal processes quickly, especially when you think of a large corporation as a big machine. It takes time and a willingness to be open to change. It will happen eventually. The industry's evolving, and we'll eventually evolve too like everyone else in the industry. It's not an overnight thing. If it were, we would have evolved to a digital flow a long time ago, and we wouldn't even be having this discussion.

**Shaughnessy:** What advice would you give to a designer regarding design output data formats?

**Chavez:** Similar to my teaching in CID and CID + courses, my advice to my students and fellow designers is that you have to communicate with your suppliers constantly. Establishing a long-term relationship with them is a must and communication is key for overall success! You have to stay on top of what's going on in the industry. Continuous professional development and professional networking are extremely important. You should design your PWBs at a minimum of IPC standards. When you communicate with your suppliers and hand over your data to fabricate or assemble, you should speak the same IPC language and be on the same page to set yourself up for success. Regarding IPC, get involved, especially your local IPC Designers Counsel chapter. If you don't have a local chapter, why not start one yourself?

Regarding data formats, if your supplier prefers or can only handle Gerber data, then you must provide that. If it's ODB++ or IPC-2581, then you will have to evolve too, provided your CAD tool can generate those formats. These two formats are very intelligent, and in the long run, are much better formats to use. We can do so much with them, so start embracing intelligent formats and see if you can start migrating to them within your company and with your suppliers sooner rather than later. We'll get there eventually.

Concerning providing bad data to the suppliers, you have to check your data before you send it out. You'd be surprised how many people blindly toss their data over the wall. Many don't even involve their suppliers until after the fact. By then, it's too late, and you're in a world of hurt. Some designers may not even produce a fabrication document; they just send Gerber data over and say, "Build this," without any specifications or instructions. This is why you have CAM engineers pulling their hair out due to bad data being pushed on to them.

**Shaughnessy:** I appreciate it, Steph. Thanks for your time.

Chavez: My pleasure, Andy. DESIGN007

### **Medication You Can Wear**

Drug-releasing textiles could, for instance, be used to treat skin wounds. EMPA researchers are currently developing polymer fibers that can be equipped with drugs.

For the "Self Care Materials" project, fibers are produced from biodegradable polymers using various processes. "The targeted use of the fiber determines which manufacturing process is best," explains EMPA researcher and project coordinator René Rossi.

Delicate, light membranes with a large surface are formed during so-called electrospinning. If robust fibers are required, it is better to draw the melted ingredients. In the end, all processes produce novel fibers, the nano-architecture of which is made up of several layers and components. "The use of self-care fibers is conceivable for an enormous number of applications," says Rossi. In addition to chemical signals from the body, however, stimuli can also be used that are deliberately set from the outside to control the release of medication by the fibers. Textiles or dressings that release a remedy under slight pressure or a stimulus of light can contribute to the quality of life of patients and at the same time relieve the burden on health care staff.

The system can also be used for preventive measures. The idea behind it: Where active substances can be released, substances are also able to penetrate the fiber in the opposite direction.

(Source: EMPA)

## Heroically On Time

Saving Our Customers Time & Money With Amazingly Fast Lead Times

### Printed Circuit Board Solutions

Is bigger always better? Maybe if you have all the time in the world? APCT may not have a fortress or a thousand rows of equipment, It just has the heroes in place to execute your lead times.

### APCT, Delivers World Class Lead Times!

| CYCLE TIMES                        | APCT Santa Clara | APCT Wallingford | APCT Orange County | APCT Cirtech |

|------------------------------------|------------------|------------------|--------------------|--------------|

| Through-Hole Technology            |                  |                  |                    |              |

| Standard Lead Time                 | 15 Days          | 15 Days          | 15 Days            | 4 - 6 Weeks  |

| 2 - 10 Layers Expedited Lead Time  | 24 Hours         | 48 Hours         | 24 Hours           | -            |

| 12 - 24 Layers Expedited Lead Time | 48 Hours         | 72 Hours         | 48 Hours           | -            |

| Filled Via in Pad Technology       |                  |                  |                    |              |

| Standard Lead Time                 | 15 Days          | 15 Days          | 15 Days            | 20 Days      |

| Expedited Lead Time                | 2 - 3 Days       | 4 - 5 Days       | 2 - 3 Days         | 5 - 7 Days   |

| HDI Technology                     |                  |                  |                    |              |

| 2x Lam Cycles Standard Lead Time   | 15 Days          | 20 Days          | 20 Days            | 20 Days      |

| 2x Lam Cycles Expedited Lead Time  | 3 - 5 Days       | 5 Days           | 3 - 5 Days         | 10 Days      |

| 3x Lam Cycles Standard Lead Time   | 20 Days          | 20 Days          | 20 Days            | -            |

| 3x Lam Cycles Expedited Lead Time  | 7 Days           | 10 Days          | 7 Days             | -            |

| 4x Lam Cycles Standard Lead Time   | 25 Days          | -                | 25 Days            | -            |

| 4x Lam Cycles Expedited Lead Time  | 10 Days          | -                | 10 Days            | -            |

| APCT.com | APCT Santa Clara<br>Corporate HQ | <b>Cirtech</b><br>A Division of APCT | APCT Orange County | APCT Wallingford | APCT Global  |

|----------|----------------------------------|--------------------------------------|--------------------|------------------|--------------|

|          | 408.727.6442                     | 714.921.0860                         | 714.993.0270       | 203.269.3311     | 203.284.1215 |

### Getting on the Same Page: A Data Story

### The Bare (Board) Truth

Feature Column by Mark Thompson, CID+, PROTOTRON CIRCUITS

In this month's column, I will write about what makes a great incoming dataset for PCB fabrication.

#### **Drawings and README Files**

The overall part thickness should be expressed as the desired thickness measured between two points, including tolerances. For example:

• 0.062" ± 10% metal-to-metal including surface finish

This description tells us the part will be 0.062" nominal with an allowed variance of  $\pm 10\%$  measured over the finished plated metal and surface finish. If the drawing or README file merely states 0.062", the fabricator must establish whether or not this is a maxthickness imum or if a tolerance is associated with it. The note also says nothing about what distance 0.062" refers to. Is it 0.062" glass-to-glass over the material, or is it metal-to-metal? Does this include plate-up and surface finish, or is it an overall dielectric with a tolerance, such as  $\pm 10\%$ ?

Thickness callouts for single-sided or double-sided orders are even more critical. As a fabricator, we can control the thickness of the multilayer by using different combinations of prepregs/cores. If a customer calls out a single-sided or double-sided job as 0.008", is this the core dielectric or an overall dielectric? If 0.008" represents the core dielectric callout on a 2-ounce finished part, the final thickness would be closer to 0.013". If the callout for 0.008" pertains to the overall fin-

ished thickness, we would need to start at a 0.004" core to finish at approximately 0.009" after plate, surface finish, and mask. Again, notes about thickness should idedescribe allv what the overall thickness is to be and the points from which they should be measured.

Another example of drawing callouts that can require clarification is copper callouts. If the drawing or README file expresses the copper merely as 2-ounce copper, this leaves the fabricator with more quesFlexible, reliable Supply<br/>Chain Solutionshigh quality copper clad<br/>laminates & prepreg<br/>bonding materials

Ventec International Group is a world leader in the production of high quality and high performance copper clad laminates and prepregs, with full R&D and product development capabilities. Our global distribution means we can readily supply our products to all markets in all geographic areas.

Get your free copy of The Printed Circuit Designer's Guide to...Thermal Management with Insulated Metal Substrates.

DOWNLOAD NOW

### Ventec - wherever technology takes you, we deliver

#### Ventec International Group

ventec

INTERNATIONAL GROUP

**螣**輝雷子

179 Ward Hill Ave, Ward Hill, MA 01835, United States T: 978-521-9700 E: ordersCA@ventec-usa.com Y Follow @VentecLaminates

www.venteclaminates.com

tions. Is it a starting or finished copper callout? If the part is a multilayer board, is it 2-ounce inners and 2-ounce finished outers? If that's the case, a fabricator will start on 1-ounce copper clad outers and plate to a 1-ounce finish. IPC dictates that there be a minimum of 0.0008" copper in the barrels of the holes for conductivity concerns. Fabricators typically plate up in whole ounce increments to ensure this minimum requirement is met, so a part that started on half-ounce copper foil would finish at 1.5 ounces after plate.

If a note merely reads 1-ounce finish, the fabricator must call the customer to clarify their intentions because starting on 0.05-ounce foil and plating to 1 ounce does not meet IPC minimum requirements for hole wall thickness. A good copper callout note on a drawing or README file should indicate finished copper for both inner and outer layers as well as a reference to minimum copper in holes, such as:

- Copper clad cores and prepregs per IPC-4101/26, 83, 98

- 1-ounce copper weight on internal layers and 0.5-ounce copper plated to 1.5-ounce finish on external layers, unless otherwise specified on stackup

This description tells the fabricator a few things at once:

- Which materials they are allowed to use (4101/26, 83, 98)

- What the inner layer and outer layer starting copper will be, including finished copper

For the holes, a good note could read:

- All holes to meet IPC-6012B Class 2 annular ring

- Plated hole wall thickness to be 0.001" with 0.0008" absolute minimum

This callout gives us criteria for acceptability and a tolerance for hole wall plating. Additional notes about holes could address other items, such as allowed tolerance for true drill position. For example:

• All holes shall be located within 0.0008" diameter of the true position

Another example might describe whether or not certain hole sizes, such as vias, require conductive or non-conductive filling:

• All 0.008" vias to be filled with conductive material and the final surface shall be flat with no dimples or protrusions

This is a typical note for via-in-pad applications where the vias are drilled, filled with the conductive material, and planarized (made flat, so that no dimples or protrusions exist on the surface mount). If done right, there will be no evidence that a via even exists in the surface mount. If any holes require solder mask plugging or tenting, one might say:

• All vias to be filled and covered with solder mask

It is important to remember that the absence of such notes on a fairly complicated board can result in a clarification call or email from the fabricator that can delay the fabrication of the parts.

#### Too Much is Just as Bad as Not Enough

Is there such a thing as too many notes or details? Yes, an effort to give as much detail as possible can sometimes result in conflicting notes, which will also result in a call or email from your fabricator. For example, one that we frequently need to clarify is where specific dielectrics are shown on a stackup detail on a drawing. In conjunction with this, the notes on the drawing refer to the acceptable types of materials that can be used. The customer will often show a dielectric constant (Dk) value that all impedances are based upon. Many times, the Dk number does not match what the fabricator knows to be the real effective Dk of that particular subsection based on the allowed materials and customer-specified dielectric.

Powerful Schematic Capture and PCB Design Software

# Are you looking for cost effective **PCB Design Software?**

### Look no further, **Pulsonix** is the answer

- Very easy to learn and use

- Co-design in integrated PCB/3D design environment

- Import design data from your existing CAD tool

- High Speed design with Constraint Manager

- Free access to over 13 million library parts

- STEP integration with Mechanical CAD

- Reverse Engineer feature to PCB from Gerber files

### Download a FREE trial from **pulsonix.com**

Contact us today and see how Pulsonix can work for you:

Email sales@pulsonix.com

### www.pulsonix.com

As you know from previous columns, a general rule of thumb is that the thinner the dielectric of prepreg, the higher the resin content, and the higher the resin content, the lower the Dk. If a Dk is listed for a 0.004" dielectric subsection as 4.5, we must use thin pregs as low as 3.3 for FR-4/406 derivatives and 3.87 for the thinnest pregs on Nelco N4000-29 (a commonly allowed material for RoHS compliance and the elevated temperatures at assembly due to alternative surface finishes) to achieve this dielectric. Ultimately, this can result in the need for either altering the specified dielectrics or resizing impedance lines, which is less desirable.

The bottom line is this—avoid specific Dk or material information unless it is critical to the design. It is better to call out the material type via IPC-4101 or the number used on the material specification. Specifying Dk or dielectric numbers in your stackup may precipitate a call or email from your manufacturer and require a negotiation, which takes valuable time.

### The bottom line is this avoid specific Dk or material information unless it is critical to the design.

#### Pre-Quote Software

Another example is IPC-2581, which is an allinclusive consortium package that includes the bill of materials (BOM) and assembly information as well as design and image output data in three formats. As long as there is no conflicting information between the image data—and sometimes there is—this dataset can be used. I am writing this from the standpoint of quick but accurate PCB quotes, not the validity of a given dataset, which means I don't have any issues with an IPC-2581 output for manufacturing.

However, for fast and accurate pre-quote analyses, the additional files in datasets, such

as IPC-2581 and others that include multiple image outputs, can slow down the quote process. We have seen as many as six separate ODB++ outputs—some as an ODB folder, some as TGZ files, and some as ODB inside a ZIP file—all in the same dataset. Many fabricators use pre-quote software packages, such as INSIGHT or Integr8tor. Both are outstanding for what they are intended. A prequote design check to ensure obvious things like trace and space meet the defined copper weight and that a Drill file exists and matches the drawing.

Even though the datasets should all be the same in theory, input pre-quote packages must be edited so that only one dataset is checked. Multiple sets will stop the operation and ask for more user information, which again, takes time out of the quote process.

Additionally, file naming conventions are another way to streamline the quote process. Many design systems have a default for file names as do drawing stackup templates. Most do not match exactly, and if there are no Z-axes layer designators on the file itself, sometimes it is difficult to tell what each layer should be. For example, the image data file template may call inner plane layers "GP1" for Gerber plane 1, but your stackup may show the real names of the layer functions. Thus, GP1 of your image data may be called "GND" or "PWR" on the stackup describing the layer function more than the layer name.

This is not an issue most of the time if you provide an EXTREP file or extension representation file that describes the layer versus stackup layer names. Much like with multiple image datasets, incoming pre-quote software packages will have trouble with identifying each layer and will pause for the operator to give the system more information to continue with an analysis. As far as the pre-quote analysis is concerned, if the layer names and stackup layers can match and multiple datasets do not need to be culled before running the pre-quote software, the faster the pre-quote software works, the quicker you get your quote. Again, the purpose of this column is not to suggest you do not use IPC-2581, but to suggest you eliminate duplicate sets of data that slow down the quote process for faster quotes. Neither of the previous examples is showstoppers that do not allow us to build the part, but they do take additional edit time, and if discrepancies exist, address them before fabrication.

### **Quick Tips**

Lastly, here are a few items you should know about that can increase manufacturing costs:

- Minimize blind vias when they are not needed based on part real estate/ interconnects, because they add approximately eight hours to manufacture time

- 2. Minimize the number of drill sizes you use and combine those within 1 or 2 mils of one another to save costs

- 3. If a part is conducive to score, set it up as a score instead of a tab rout because tab routs add additional time and drills for the perforation holes

- 4. Avoid the use of minimum radius areas where two different rout sizes are needed because it increases the cost

- 5. Avoid using multiple 0.001" draws on silkscreens because this exponentially increases the data size and takes longer through computer-aided manufacturing (CAM)

### Conclusion

It is important to make sure any drawing notes address customers' reliability concerns in a manner that is clear to the fabricator and minimizes any time lost due to note clarifications or the absence of notes. **DESIGN007**

Mark Thompson is in engineering support at Prototron Circuits. To read past columns or contact Thompson, click here. To download your copy of Thompson's eBook, The Printed Circuit Designer's Guide to...

Producing the Perfect Data Package, click here.

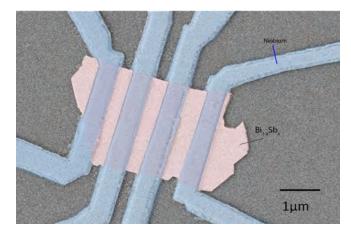

### Superconducting at the Speed of Light

Sightings of Majorana modes are rare and have up to now always involved states at the edge of special, topological materials. As reported in the October issue of "Nature Materials," a new discovery shows that the bulk electronic states of a three-dimensional Dirac semimetal can also play host to topological superconductivity and the related Majorana zero-modes. As these states are protected by fundamental symmetries, their discovery on the

inside of a crystal, hidden from the disturbing influences of the environment, is a valuable next step towards their application in topological quantum computation.

Spotting Topological Superconductivity

In a new development, researchers from the universities of Twente and Amsterdam, as part of a Dutch national research programme into so-called topological insulators, have combined forces to show that inside a tuned crystal of bismuth hide the Majorana modes signaling topological superconductivity.

While it may not be found in your kitchen cupboard at home, the heavy atoms of bismuth-in the form of pure crystals-have served as a test set-up for research into the behavior of electrons in a solid for almost a hundred years. For example, it was in bismuth that it was discovered that the electrical resistance of a material can change or even oscillate by applying or changing a magnetic field, a phenomenon which has grown into an indispensable tool in modern materials research.

(Source: University of Amsterdam)

### At GreenSource, Lean and Green Starts on the Front End

#### Feature interview by Andy Shaughnessy I-CONNECTO07

Whelen Engineering's board shop, Green-Source Fabrication, is set to go commercial at the end of the year. But GreenSource Vice President Alex Stepinski has set his sights high from the start.

The Charlestown, New Hampshire, facility may be the board shop of the future. Green-Source is the first new captive shop in America in decades and one of the first waste-free board shops as well. It's almost a "no-touch" operation. The CAM engineers all work remotely, and they can launch a job without ever entering the facility.

I spoke with JanNell Taylor and Andy Schilloff, who work at the CAM office in New York. We discussed what it's like working for a company that plays by its own rules, and what the front-end engineers are doing to get ready for the day that GreenSource officially goes commercial. **Andy Shaughnessy:** JanNell, can you and Andy give us a little background about yourselves?

**JanNell Taylor:** Sure. I am currently the global product engineering manager for GreenSource Fabrication. I've been in the PCB industry since 1972. My last employer was Sanmina, and I was there for almost 20 years. I was the front-end engineering manager for the past seven years I spent there.

**Shaughnessy:** Did you knew Alex Stepinski when you were with Sanmina?

**Taylor:** I actually worked for Alex. That's how I was brought into this project when he first opened Whelen.

**Andy Schilloff:** I also have prior experience working with Alex at the new product introduction (NPI) group at Sanmina a little over 10 years ago.

### Superior electro-chemicals across the board

8 8 8 8 8 8 8

When every connection counts, you can count on Electrolube's electro-chemical expertise.

With a 77-year pedigree, a growing presence in 55 countries and production in 3 global locations, we have the products, research facilities, resources and personal expertise to engineer solutions to your manufacturing challenges.

Make contact and discover what makes Electrolube the solutions people for leading manufacturers worldwide.

#### Tel: 888-501-9203 www.electrolube.com

Electronic & General Purpose Cleaning Conformal Coatings Encapsulation Resins Thermal Management Solutions Contact Lubricants Maintenance & Service Aids

ELECTROLUBE THE SOLUTIONS PEOPLE **Taylor:** Andy and I met while we were working at Sanmina. Andy worked in the NPI group, and I was in front-end engineering. Andy also worked at Sanmina in other positions, including in the front-end for a while.

**Schilloff:** I have experienced both process and product engineering over a long period of time, which helped me be effective in the NPI group. I've also had experience working for i3 Electronics most recently for a little over two and a half years, and Alex has been build-

ing up the crew here to move forward with everything that's happening at GreenSource, and he asked me to come on board. It was definitely the thing to do.

**Taylor:** In this office, we have eight CAM and product engineering personnel. There is also a customer service rep and sales manager located here. We have three people in Phoenix, and we're currently adding three

more. We're also going to be adding another person to the New York office. We'll have 15 total CAM product engineer personnel working remotely.

#### Shaughnessy: Andy, what's your title?

**Schilloff:** I'm the lead product engineer, so I deal more with the customer stuff and NPI— things that we haven't come across yet until our capabilities are well established. I'm also a principal engineer. Capability-wise, I'm a good interface between process engineering and the plant by enabling people who work remotely to get the data to where it needs to be. Alex has talked about turn times being much less than what's standard at i3 Electronics, for example, where it might take 10 weeks to build a part. We're going to do it in three weeks, so a part of that has to be an efficient front end, which will be a challenge.

**Shaughnessy:** Where are you located now?

Taylor: Owego, New York.

**Shaughnessy:** Sure, near Sanmina. So right now, you all haven't gone commercial yet officially, so primarily what you're doing is inhouse captive work, the Whelen work.

**Taylor:** Correct. We're setting up for the commercial work.

**Shaughnessy:** What are you doing to get ready for this?

**Taylor:** We purchased all new software, so we've been busy for the last year configuring our CAM and engineering software. We went to Ucamco for CAM software, and we've spent this year configuring that. We use a system called Bacon from Bacon Software, which is going to be our enterprise resource planning (ERP) system. It is also our engineering system for travelers, process loads, etc. We will not

have any paper travelers. It will all be built on barcode readers, and I believe there are 82 different barcode readers. Every barcode reader will equate to an operation on the traveler.

**Shaughnessy:** We took the tour with Alex, he pointed out all these barcode readers. You'll all be able to trigger a job from off-site without touching the board, right?

**Taylor:** Yes, it's all remote. All the data is stored at the plant, not off-site. We physically log in to the plant to work.

**Shaughnessy:** Wow. Are any other companies following this model with CAM people working off-site?

**Taylor:** When we all worked at Sanmina, we did have remote tooling. We had 11 people in Phoenix at that time who worked remotely for four or five years until they closed it down. We spent a lot of effort making that work, and

JanNell Taylor

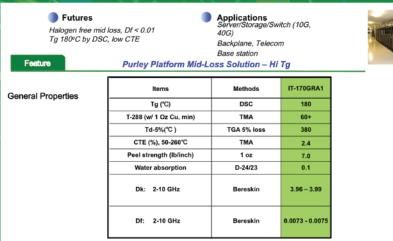

# IT-170GRA1

### IT-170GRA1 Value Proposition

- Halogen Free

- Best in class performance in its space

- •Best in class CAF performance

- Very attractive price to performance ratio

- Pass MRT-6 requirements

- -CAF > 1000 hours

- -0.65mm pitch equivalent, no thermal issue

- •Available with RTF and 2µ copper which provides additional

- performance on a very solid platform

- •Df = 0.0075 @10GHz

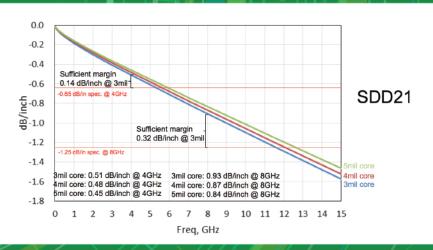

### Intel Purley Mid-Loss Solution – IT-170GRA1

IT-170GRA1 Insertion Loss

ITE

we were able to bring those lessons with us to start this group.

When I first got here, I worked alone. We brought in one software engineer, and then another, so we did the tooling and scripted things to make operations more efficient. We were very remote. We have brought in experienced help to be a part of this project, so there are some very talented folks here; we know what to do to make it happen.

**Shaughnessy:** As far as the data goes, will you accept Gerber and ODB++?

Taylor: Yes, we're capable of both. My prefer-

ence would be Gerber. If we were using InCAM or Genesis, my preference would be ODB. Now that we've migrated to another CAM software, the preference is definitely Gerber, but we're able to accept either. The problem with taking ODB data from other customers is that it works very well if you have your set-up in-house between your designers and CAM. But when you're receiving ODB from the outside, the attributes are different. You don't re-

strip all the attributes from the incoming data, and then it collides with the scripting and automation that you have in yours. Typically, what I've seen is that we receive ODB data and have to strip it down because we didn't use any of the attributes that the design engineers did. It defeats the whole purpose of having the selfcontained job.

**Shaughnessy:** Have you had any new designs come in yet, non-Whelen stuff? I know you're not officially commercial yet.

**Taylor:** We do have data that we've been performing DFMs on. We're quoting a few test vehicles that we've been building.

**Schilloff:** We're preparing to release our first HDI films, and working out a lot of the kinks, so that's getting ready to happen shortly.

**Taylor:** Any time new equipment comes in, or there's something new going on at the plant, we make trips out there. We rotate, go as a group, or a few of us go to check out the equipment and try to find out what they will need from CAM and engineering.

**Shaughnessy:** I talked to a lot of CAM people, and they say that one of their biggest jobs is educating new customers on data packages.

**Taylor:** Yes, you must work with your customers to try to streamline your profits. It's always been that way working with customers, trying to get data packages so you can

drop them in and not have anything be held up. That will continue for sure.

**Shaughnessy:** And I heard you all are going to start doing RF?

**Taylor:** Yes, we are.

**Schilloff:** A military customer has approached us. Part of that deal is to see how well we do with their constraints, and also for them to get official data and

different materials sets, so we're looking at doing that soon.

**Shaughnessy:** During our tour, we noticed that you have a group of people under 30, and you also have 30-year veterans. It seems like you have a good mix of age groups working at GreenSource.

**Taylor:** That's the goal here with what we're doing off-site: to hire younger people to pass on knowledge. We started with two, and that's working great. They pick things up quickly and are doing a great job, and we will eventually add more.

**Shaughnessy:** I understand GreenSource is planning to cross-train the engineers. I know there's a father-son team and some couples are working there, and the cross-training means

Andy Schilloff

that they can take time off to go on vacations together.

**Taylor:** We're doing that here as well in the front end so that we have the flexibility to rotate based on the demands of our schedule. We don't want to be stuck where we only have two product engineers and four CAMmers, so there's cross-training going on, and everybody here will be capable of performing every task in tooling.

**Shaughnessy:** You're writing the textbook as you go.

**Taylor:** We'll see. I'd like to read that book another year.

**Shaughnessy:** It sounds like an exciting place to work. We were laughing about how usually when we visit a board shop, everybody has a hang-dog look. Everyone at GreenSource was happy to be there.

**Taylor:** I cannot say enough good things about Whelen and GreenSource. They're the best employer I've ever had. They treat us very well. It's challenging, and it can be frustrating, but finding solutions to the challenges is what keeps me motivated. If you came in every day and did the same thing, it would get very boring. We do not have boring days here.

**Shaughnessy:** I know you all will be busy when you open the doors in a few months, so it's an exciting time for you. Thanks for taking the time to talk with me.

Taylor: Thank you for sharing our story.

**Schilloff:** You are welcome at GreenSource any time. **DESIGN007**

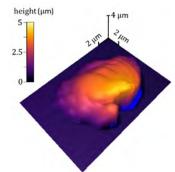

### **Novel Topological Insulator**

Topological insulators are materials with very special properties. They conduct electricity or light particles on their surface or edges only but not on the inside. This unusual behaviour could eventually lead to technical innovations, which is why topological insulators have been the subject of intense global research for several years.

Physicists of Julius-Maximilians-Universität Würzburg (JMU) in Bavaria, Germany now report their discovery in the journal "Nature." For the first time, the team has successfully built a topological insulator operating with both light and electronic excitations simultaneously, called an "exciton-polariton topological insulator."

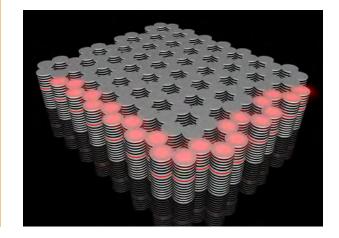

Dr. Sebastian Klembt, group leader at Höfling's chair, said that the topological insulator was built on a microchip and basically consists of the gallium arsenide semiconductor compound. It has a honeycomb structure and is made up of many small pillars, each two micrometres (two millionths of a metre) in diameter.

**Propagation Direction Can be Controlled**

When exciting this microstructure with laser light, light-matter particles form inside it, exclusively at the edges. The particles then travel along the edges and around the corners with relatively low loss.

It is a sophisticated systems which works in application-oriented dimensions, on a microchip, and in which light can be controlled. Usually, this is not so easy to accomplish: Pure light particles have no electric charge and therefore cannot be readily controlled with electric or magnetic fields. The new topological insulator, in contrast, is capable of doing this by "sending light around the corner," in a manner of speaking.

(Source: University of Wurzburg)

### Design Data: File Naming Conventions

CLEAR, CONCISE, COMPLETE

NFORMATIO

#### Feature by Kelly Dack, CID+, CIT EPTAC CORPORATION

Have you ever Googled your name? Using the internet, I found out there are not many folks named Kelly Dack in the world, though I was surprised to find out there are a few scattered here and there. Now, imagine my shock if I were to be denied a loan, referred to as "Ms. Dack," or passed up for a job opportunity because an auditor used the incorrect profile data from one of the other Kelly Dacks out there during my data verification process.

I have found that when searching for myself on the internet (come on, you do it too), I achieve better results by being more specific in my search criteria. For instance, simply adding "PCB" after my name helps to narrow the search criteria by being descriptive enough to show Kelly Dack the PCB designer and almost anything I am connected to within the PCB industry.

I recently read that up to 90% of the manufacturing data for the electronic design indus-

try's PCBs is still supplied in the non-intelligent Gerber data format. Regardless of the percentage, I know that the EMS provider I work for sees a lot of Gerber data from our customers. And we procure a lot of quality PCBs from our suppliers using Gerber data (unless we can't). Sometimes information on an entire layer or other manufacturing files are missing. Again, Gerber data is not intelligent. It is graphic information only, and if measures aren't taken by the designer to give us clues regarding how the artwork is configured, we must stop, ask questions, and seek clarification, which takes valuable time.

Working for an EMS provider, I am often asked to make sense of customers' PCB design data packages that must be audited for completeness and manufacturability. Quite often, EMS operations receive data to produce a PCB design and begin the auditing process, only to be called off due to customer changes. Sometimes the data is incomplete, or it is missing one or more of the data files required to fabricate the PCB at the supplier. There are also

### Your signal needs to get around the world fast... Why go halfway around the world to get your high-speed PCBs?

# ACE: your high-speed experts right here at home, specializing in microwave and hybrid PCBs.

Accurate Circuit Engineering 3019 Kilson Dr Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: James Hofer (714) 227-9540

www.ace-pcb.com

RoHS & WEEE compliant • Certified AS9100, ISO, ITAR, MIL-PRF-31032 & 55110

occasions where a customer has sent files that were supposed to be the updated version but were not changed at all.

All suppliers of PCBs, including assembly services suppliers, make great efforts to verify that the data they are using to build the product for a customer is the latest up-todate version. Every manufacturing process is tied to an internal product control number and revision. In production environments, the material does not move forward unless it has been checked, verified, and inspected to the revision control process in place. But what happens when the customer design data is not identified?

It is a fact that designing and engi-

neering PCBs requires changes. But the tragedy is that without organization and control, a quickly introduced change using data that is not clearly identified can wreak havoc on a supplier's manufacturing control systems. All too often in the rush to market a new PCB design, a customer's design layout template is used without the customer editing the file names to be appropriately descriptive.

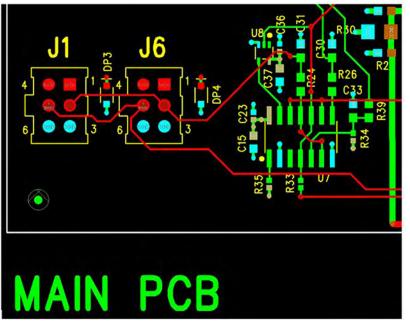

Here's an extreme example. Many designers send out data files for a "MAIN\_PCB" design to suppliers (Figure 1). Within the data archive for this generically named design, the files may also lack descriptive naming attributes. To make a point, let's examine the data archive for this four-layer, single-sided assembly design (Figure 2). As a manufacturing stakeholder,

could you quickly pick out the file that reflects the top-side legend (silkscreen)? How about the top-side solder resist artwork? Not a chance without importing the files into a manufacturing file viewer (Gerber) and putting the pieces of the manufacturing puzzle together.

In this case, the only file providing a clue to its functionality is the .NCD file. The supplier

Figure 1: Many PCB designs are named "MAIN\_PCB."

will probably assume that this is an NC Drill file. The other files will need further investigation. But even after assimilating the files into a viewer, determining the functional purpose of the files without any descriptive help is a challenge. Let's use the viewer to plunge inside the design files to see if we can determine how to use this data.

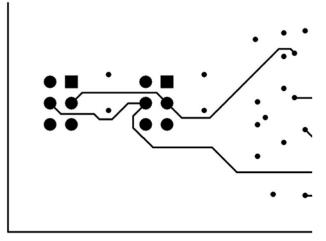

Is the view of the MAIN\_PCB\_1.pho file in Figure 3 the top-side artwork or the bottom side? How would your fabrication stakeholder know? Next, let's take a look at another file in the archive, the MAIN\_PCB\_6.pho file. It appears to be a power plane. Shall we assume that it resides on an inner layer (Figure 4)? If so, which one? There are two inner layers. I'm getting a headache. This is impossible!

| Name           | Date modified      | Туре            | Size   |

|----------------|--------------------|-----------------|--------|

| MAIN_PCB_1.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 146 KE |

| MAIN_PCB_2.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 206 KE |

| MAIN_PCB_3.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 150 KE |

| MAIN_PCB_4.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 147 K  |

| MAIN_PCB_5.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 145 KI |

| MAIN_PCB_6.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 151 K  |

| MAIN_PCB_7.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 149 KE |

| MAIN_PCB_8.NCD | 5/30/2014 11:53 AM | NCD File        | 1 KE   |

Figure 2: Name your files in a way that lets the fabricator know your intent.

Figure 3: Be sure to label your artwork "top" and "bottom."

Figure 4: This MAIN\_PCB\_6.pho file appears to show a power plane. Is it on an inner layer? Which one?

Lord, help our manufacturing stakeholders when the new, non-descriptive revision to the "MAIN\_PCB" design is subsequently released by the customer and sent to the supplier for processing. Figure 5 shows the new file, or maybe it is the old file by mistake. How can we know? Both files are named MAIN\_PCB\_6. pho. Is there a difference? Some may rely on the file's date stamp, but this can be very unreliable. PCB designers, please help. Can you tell us which file is the latest and if it is identical? Have any changes been made?

Without going any further, I think that all PCB designer readers can see the point. Good graphic data without descriptive attributes is confusing and down-right dangerous. There

Figure 5: This MAIN\_PCB\_6.pho file may be the new file. Or is it the old one?

is not an EMS stakeholder alive who would proceed to manufacturing without concrete answers to the many questions that result from trying to process these non-descriptive files.

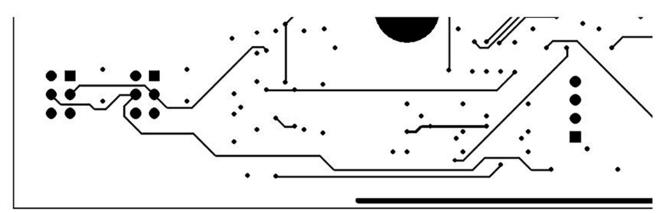

One thing PCB designers can do to help suppliers in the area of configuration auditing, control, and processing is to add specificity to the data file names when outputting and archiving the PCB data package.

Let's examine what descriptive information can be added to this PCB design data package to make it easier on the stakeholders' configuration auditing and control process:

1. Consider adding a graphic title block to the design database that can be output along with each artwork layer. This is where many informational blanks can be identified, including a descriptive name, part number, revision, date, responsible designer, and EE contact information. The title block can be placed within the design to print on all layers, and edited only once per revision (Figure 6).

|               | PCB, MAIN, MICRO-COMBOBULATOR |                          |              |  |

|---------------|-------------------------------|--------------------------|--------------|--|

| PART NO .:    | 424242-42                     | REV: A DATE:             | 2018-JAN-01  |  |

| DESIGNER: JEN | INY FINELINE                  | (800) 867-5309 ENGINEER: | SPARKY SMITH |  |

Figure 6: Adding a graphic title block to the design database for output with each artwork layer is a good idea.

Figure 7: Descriptive nomenclature for each artwork layer helps identify its function.

| Name                           | Date modified      | Туре            | Size   |

|--------------------------------|--------------------|-----------------|--------|

| 424242-42_A_DRILLFILE.NCD      | 5/30/2014 11:53 AM | NCD File        | 1 KB   |

| 2424242-42_A_LAY_1.PHO         | 5/30/2014 11:53 AM | CAM350 Pho File | 150 KB |

| 424242-42_A_LAY_2.PHO          | 5/30/2014 11:53 AM | CAM350 Pho File | 147 KB |

| 424242-42_A_LAY_3.PHO          | 5/30/2014 11:53 AM | CAM350 Pho File | 145 KB |

| 424242-42_A_LAY_4.PHO          | 5/30/2014 11:53 AM | CAM350 Pho File | 151 KB |

| 424242-42_A_LEGEND_TOP.PHO     | 5/30/2014 11:53 AM | CAM350 Pho File | 146 KB |

| 424242-42_A_SOLDERMASK_BOT.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 149 KB |

| 424242-42_A_SOLDERMASK_TOP.PHO | 5/30/2014 11:53 AM | CAM350 Pho File | 206 KB |

Figure 8: Data file names should correspond to the descriptive list on each layer of artwork.

- 2. Next, consider adding descriptive nomenclature to each specific artwork layer to identify its function, and graphically link it to its associated data file (Figure 7). Upon viewing, there is no question that this artwork represents the bottom-side signal layer as revision A of part number 424242-42 derived from the 424242-42\_A\_LAY\_4.PHO data file.

- 3. Lastly, name your data files to correspond to the descriptive list on each layer of artwork. With a naming format, files can be audited for completeness and moved to CAM without previewing and deciphering beforehand (Figure 8).

Adopting this simple, but descriptive, naming methodology for any manufacturing design data package will go a long way in helping your PCB manufacturing stakeholders to serve you better. **DESIGN007**

Kelly Dack provides PCB design and manufacturing engineering services for a dynamic EMS provider in the Pacific Northwest. Additionally, he serves on the executive staff of the IPC Designers Council and is

employed by EPTAC Corporation as a CID instructor. To contact Kelly, click here.

### **A NEW QUARTERLY MAGAZINE**

With original content dedicated specifically to flex system and PCB designers, electrical engineers and those responsible for integrating flex into their products at the OEM/CEM level, you won't want to miss a single issue of **Flex007 Magazine**!

Contribute

**Advertise**

### Digital Specs for Automated Manufacturing: Find the Missing Link!

#### **PCB Norsemen**

Feature Column by Jan Pedersen, ELMATICA

Automation and connected smart factories are the new manufacturing trend. Industry 4.0 and the Internet of Things (IoT) continue to enter PCB manufacturing. However, if we continue down the same path with specifications and requirements written on electronic papers and unintelligent production files, human interpretation is still crucial to avoid mistakes. CircuitData could solve this problem because having one language for automated smart factories is the future!

With the I-Connect007 article about the grand opening of the Unimicron factory in Germany fresh in mind, I also had the opportunity to visit it in June for the 50<sup>th</sup> anniversary of EIPC<sup>[1]</sup>. I have seen hundreds of PCB factories virtually, but this was my first time seeing a smart PCB factory in person. The tour showed me how far we have come if we use all available tools. Further, it reminded me of the missing links that disable a true digital chain of information needed to utilize systems in smart factories, such as Unimicron and Whelen Engineering's GreenSource Fabrication in the United States.

#### **Automating PCB Production**

Today, most processes in a smart PCB factory can be automated and monitored. Continued innovation is accelerating the Industry 4.0 transformation of the PCB factory. We strive to analyze and share time-production data to be able to understand and act immediately. When I have visited and audited PCB factories lately, I have seen a growing trend—even with more traditional factories—to have connected equipment, such as online and real-time process monitoring, remote production, and maintenance alarms<sup>[2]</sup>.

Observing this, it is puzzling to me that we still feed factories with specifications and requirements written on electronic papers and unintelligent production files. Experts in the indus-

# **RISE ABOVE** THE AVERAGE

THE HITCHHIKER'S GUIDE PCB DESIGN

Things You Wish You Knew Yesterday and Will Need to Know Tomorrow

100+ PAGES of valuable PCB knowledge they didn't teach in school, straight from industry veterans.

Ready to Learn? Download the Guide >

try continue to claim that a fabrication drawing printed on A3 paper is vital to understand customers' requirements. Corporate requirements—even the measurable parts—are given in an analog way into an increasingly digital environment. In almost every issue of I-Connect007's magazines and other publications, we read about how Industry 4.0 and smart manufacturing are growing and changing the production environment.

However, the missing link is how we transfer and communicate fabrication data between the product owner and the PCB factory. To avoid ambiguous specifications, we need a common language to communicate the specification and use the same terms in all parts of the transmission chain.

To avoid ambiguous specifications, we need a common language to communicate the specification and use the same terms in all parts of the transmission chain.

#### CircuitData and IPC-2581

CircuitData is the only language available today to digitally communicate a complete and accurate specification with all measurable corporate requirements and standards included, such as the IPC-6011 series <sup>[3]</sup>. CircuitData is an open source language for communicating PCB article specifications, corporate requirement profiles, engineering change notes, and engineering questions. It consists of a computer-readable file with tools to easily link with your existing software. The file can be updated in real-time from designers to OEMs, EMS providers, brokers, and the PCB factory. One file handles it all with no missing information or misinterpretations.

We also need an intelligent way of presenting the production data. IPC-2581 is one of the systems that communicates the electronic design into the digital environment of the smart PCB factory with sufficient intelligence <sup>[4]</sup>. IPC-2581 is a generic standard for PCB and assembly manufacturing description data and transfer methodology. Developed in 2004 by IPC, IPC-2581 is used for transmitting information between a PCB designer and a manufacturing or assembly facility. For nearly every step in the industrial process flow, IPC-2581 offers a standard to help companies ensure superior manufacturability, quality, reliability, and consistency in electronics assemblies built for their products.

#### Garbage In, Garbage Out

With tools like CircuitData and IPC-2581, we can secure correct description data, provide sufficient file intelligence, and enable a full digital data transfer to give value to the smart PCB factory. Without these tools, we retype specifications and accept human errors just like we did decades ago. By using a less intelligent transfer methodology than IPC-2581, we accept incomplete information. Garbage in, garbage out! A chain is no stronger than its weakest link.

Data for the future smart PCB factory requires the same digital quality for transfer between the designer and the smart PCB factory. Automated manufacturing requires digital specifications. Nothing less is acceptable. **DESIGN007**

#### References

1. Unimicron Germany Rises from the Ashes with New Smart Factory by Pete Starkey (I-Connect007) and Michael Weinhold (EIPC), PCB007 online, April 30, 2018.

2. The evolution of Industry 4.0, through the eyes of the PCB manufacturer by Shavi Spinzi, Evaluation Engineering online, June 22, 2017.

3. circuitdata.org 4. ipc2581.com

Jan Pedersen is senior technical advisor at Elmatica. To read past columns or contact Pederson, click here.

## HETEROGENEOUS INTEGRATION: THE PATH FORWARD REALIZING THE COST AND PERFORMANCE BENEFITS

#### WEDNESDAY, DEC. 5, 2018 | SEMI GLOBAL HEADQUARTERS | MILPITAS, CA SYMPOSIUM 8:00AM - 5:00PM | EXHIBITS 9:30AM - 6:30PM | RECEPTION 5:00PM - 6:30PM

#### **KEYNOTE SPEAKER**

Heterogeneous Integration Roadmap and SiP

William "Bill" Chen, ASE Fellow and Senior Technical Advisor, ASE Group

#### **KEYNOTE SPEAKER**

Disruption is Coming: Adapt, Change or Be Left Behind

Keith Felton, Product Marketing – IC Packaging, Mentor Graphics Board Systems Division

#### **KEYNOTE SPEAKER**

Heterogeneous Integration: Is it Ready for Changing the Packaging Landscape?

Risto Puhakken, President, VLSI

**MEPTEC** continues to cover leading-edge topics in semiconductor packaging with its Fall 2018 Symposium *"Heterogeneous Integration: The Path Forward."* Industry leaders will present the latest updates on technical and business issues related to integration of different types of semiconductor devices. This field has been identified as the next critical area for the semiconductor industry to continue to advance, as progress via Moore's Law scaling becomes increasingly cost-prohibitive or prevented by insurmountable technical challenges. With progress in many areas, cost and performance benefits are finally being realized, and previously impossible combinations of devices are now possible.

Don't miss this unique opportunity to get up to speed at MEPTEC's symposium "Heterogeneous Integration: The Path Forward" on December 5, 2018 in Milpitas, CA.

Sponsorship Opportunities and Exhibit Spaces Available

SPONSORS AND EXHIBITORS

#### **REGISTER ONLINE TODAY AT WWW.MEPTEC.ORG**

# **PGD PCB007** Highlights (

### EPTE Newsletter: New Materials for Wearable Electronics >

Technology continues to evolve, and wearable electronics are the focal point for many new concepts. The next generation of wearable products for the consumer electronics industry will create a new market with nothing but upside for manufacturers and suppliers.

#### Flex Talk: Mina–RFID, LED and What Else? >

"The science of today is the technology of tomorrow." This Edward Teller quote is an apt description of the Mina product. This advanced surface treatment recently developed to enable low-temperature soldering to aluminum in the RFID market is finding success in that market and quickly finding a home in other markets including the LED market—where the incentive is both cost and improved LED performance.

### PCB Designers: Perfect Your Data Package with New eBook from Prototron >

For PCB designers, producing a comprehensive data package is crucial. If even one important file is missing or output incorrectly, it can cause major delays and potentially ruin the experience for every stakeholder. Learn how to perfect your data package with I-Connect007's most recent title: *The Printed Circuit Designer's Guide to... Producing the Perfect Data Package.*

## Rogers to Highlight Latest Circuit Materials and Share Expertise at EDI CON USA 2018 >

Rogers Corporation will share its experience and expertise on circuit materials technologies at the 2018 Electronic Design Innovation Conference (EDI CON USA 2018) October 17–18, in the Santa Clara Convention Center (Santa Clara, California). EDI CON USA 2018 is entering its third year of serving the high-frequency RF/microwave design engineering community.

# Standard of Excellence: Working for the Future–Partnering with PCB Vendors on Innovative Technology >

The true test of the vendor-customer relationship comes when you need innovative PCBs—boards that are not easily found in the common marketplace and are so technologically advanced that they require your designers and suppliers to work together to go where neither has before.

#### Alun Morgan Named Technology Ambassador for Ventec ►

Ventec International Group Co., Ltd., announced that Alun Morgan, chairman of the EIPC, has been named technology ambassador for Ventec International Group.

#### American Standard Circuits Launches Fusion Bonding for RF Boards >

American Standard Circuits is now offering fusion bonding of PTFE-based materials. Fusion bonding of PTFE-based materials involves using high temperatures (≥700°F/371°C) to bond PTFE directly to the copper circuitry and surrounding PTFE.

#### Building a Better Board: It Always Comes Back to Communication >

For our experts meeting on the August's theme of reliability, we reached out to Colonial Circuits and asked them to participate in a conference call with our I-Connect007 editorial team consisting of Dan Feinberg, Andy Shaughnessy, Patty Goldman, and Happy Holden. Joining the call from Colonial Circuits was Mark Osborn, president and CEO, Kevin Knapp, quality manager, and Rodney Krick, manufacturing manager.

AS-9100D

# Your Passport to Global PCB Sourcing

PASSPORT

We are pleased to announce that with the same fine service, quality, delivery and attention to detail that our customers have grown to rely upon, we are now adding a complete global solution to meet all of your needs, both today and in the future.

#### **Our Solutions:**

- FLEX & RIGID-FLEX

- HDI / MICROVIA

MORE INFO

Global PCB Sourcing

- COMPETITIVE VOLUME PRICING

- PRE-QUALIFIED OFFSHORE PARTNERS

- QUICK-TURN PROTOTYPES

PROTOTRON.COM (888)847-7686

- COMPLEX MULTILAYER

- MIL-SPEC PRODUCTION

- SPECIALTY MATERIALS

E BOOK

REDMOND, WASHINGTON • TUCSON, ARIZONA • GLOBAL PARTNERSHIPS

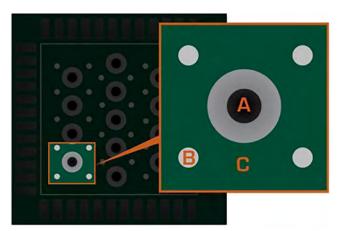

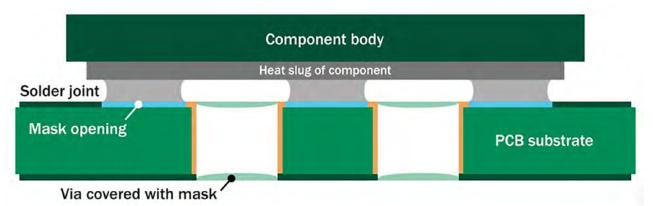

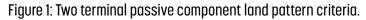

# New Landing Design to Reduce Thermal Pad Failures

#### Connect the Dots New Column by Bob Tise and Dave Baker, SUNSTONE CIRCUITS