### **OCTOBER 2020** DESERVICE MAGAZINE Connect00

# INTO THE FUTURE

# FIEIDUI FEATURESTORY ADM

PAGE 18

## Master the art of keeping cool!

Learn how to beat the heat in your designs with techniques and methods from a fabricator's perspective.

DOWNLOAD NOW 🛃

# Distinctly different.

Our books are written by recognized industry experts. At around 8,000 words, they are unique in that they are able to be incredibly focused on a specific slice of technology.

### "I-007ebooks are like water in the desert ...it's up to you to drink it in order to survive!"

Stephen V. Chavez PCEA Chairman, MIT, CID+

### **VISIT OUR LIBRARY**

#### **OCTOBER 2020 • FEATURE CONTENTS**

### **DESIGNOOT** MAGAZINE Roadmaps: Into the Future

Even the most experienced hikers can get lost if they don't have a map. The same holds true in the world of PCB design and manufacturing—if your company doesn't have a technology roadmap, it's hard to know where you're going technologically. This month, we take a look at a variety of technology roadmaps related to PCB design, and some of the milestones that may be in our not-too-distant future.

52

60

### FEATURES:

- 12 Looking Into the Future With Progressive Design and Analysis Interview with Todd Westerhoff

- 24 How Designers Can Help Facilitate Co-Design Interview with José Schutt-Ainé

- 36 IEEE's Heterogeneous Integration Roadmap, Part 2 Interview with Rita Horner

- 42 Managing Information Is Key for Altium's Next Generation of Tools Interview with Leigh Gawne

70 How the HIR Impacts Design Through Assembly Interview with Paul Wesling

Interview with

Jeff Demmin

**FEATURES**:

the HIR

by Michael Nopp

The Aerospace and

**Defense Chapter of**

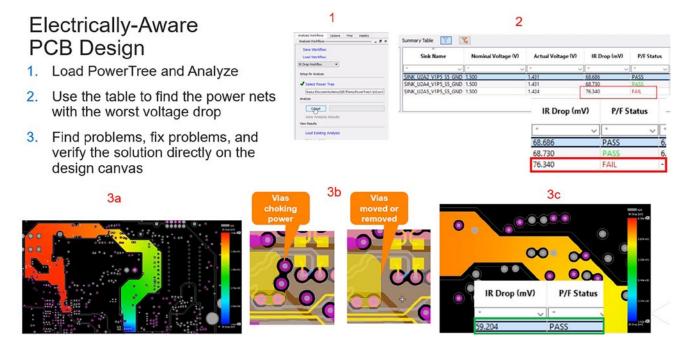

**Empowering Electronically-Aware**

**PCB** Designers of the Future

#

**COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

### **OCTOBER 2020 • ADDITIONAL CONTENTS**

# DESIGNOOT

### SHORTS:

- 31 Purdue Team's PCB Design Improves Electric Guitars

- 50 DigiLens Brings Ultra-Compact CrystalClear AR HUD to Any Auto Dashboard

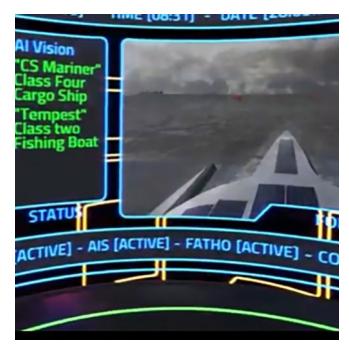

69 Mayflower Autonomous Ship Launches

### 76 Bear Robotics, SoftBank Robotics Group Create Food Service Robot

#### 6 DESIGNO07 MAGAZINE I OCTOBER 2020

### COLUMNS:

10 The Future Is Now by Andy Shaughnessy

- 18 Fringing Fields by Barry Olney

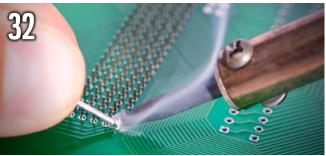

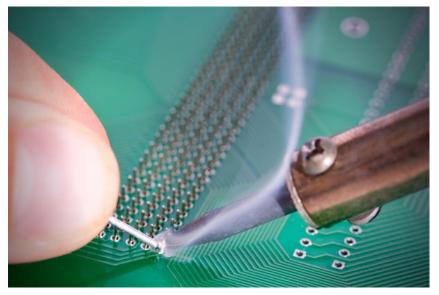

- 32 Unraveling the Mysterious BGA Routing Mess by Bob Tise and Matt Stevenson

- 46 Local Chapters: You Can Distance This Body But Not These Senses by Kelly Dack

- 56 Why Do High-Frequency Materials Have Different Dk Values? by John Coonrod

- 66 Pushing the Boundaries of Thermal Management by Jade Bridges

### HIGHLIGHTS:

- **59** PCB007

- 77 MilAero007

- 98 Top 10 PCBDesign007

### **DEPARTMENTS**:

- **101** Career Opportunities

- 110 Educational Resource Center

- 111 Advertiser Index & Masthead

HFI D

WANTEI

### System Analysis

10X Faster Simulation with Unparalleled Scalability

READ WHITE PAPER

### cādence<sup>°</sup>

### **OCTOBER 2020 • CONTENTS**

Creating a technology roadmap is never a simple task; companies and organizations often spend years editing and fine-tuning their tech roadmaps. This task is exponentially tougher for a segment like flexible and rigid-flex circuits, which seems to be evolving constantly. Would you care to hazard a guess about where flex technology might be in five or 10 years?

FLEXO07 FEATURE:

**Flexible Circuit 78 Technologies Offers** a Flex Roadmap for the Future

Interview with Carey Burkett and Mark Finstad

FLEXO07 COLUMNS:

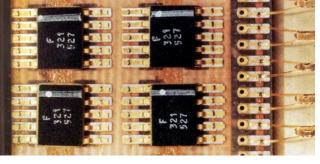

84 **Technology Roadmaps in the Electronics Industry** by Joe Fjelstad

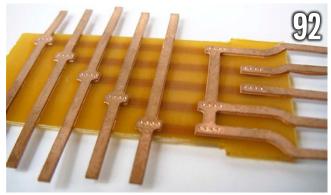

**92 Heavy-Copper Flex Circuits** See Large Growth by John Talbot

Make use of the expertise your product deserves.

#talktothePCBexperts

Our most experienced experts were already **solving PCB challenges** when man first walked the moon.

### **ELMATICA®**

NOBODY COMPLETES YOUR PURCHASING PROCESS BETTER THAN US PRINTED CIRCUITS SINCE 1971

www.elmatica.com

## The Future Is Now

### The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

Our technology roadmaps issue started with a question for Happy Holden.

A few months ago, we were planning content for the fall issues of our magazines. We had just launched the "Just Ask Happy" series, with readers sending him all manner of questions about HDI, automation, predictive engineering, TQM, markets—you name it.

But one question caught our attention: How will the PCB design process change to align with the IEEE Heterogeneous Integration Roadmap (HIR), and do you think this will happen? Good question.

Happy explained that IEEE is now referring to chip-on-board (COB), multi-chip modules (MCM), and system-in-packages (SIP) as heterogeneous integrated modules (HIM). As Happy noted:

"Heterogeneous was chosen because the future modules will incorporate not just IC chips, but also power devices, passive discretes, photonics, MEMS, sensors, antennas, and batteries. Systems-on-chip (SoC) will continue to be an activity, but as Moore's Law has flattened out, using multiple-cores processor chips with memory is more cost-effective for greater computing power. As applications grow—and size, cost, and weight are more critical—heterogeneous integrated modules offer the best choice to move all of these elements closely together in a module."

In other words, these packages are becoming a lot like little circuit boards.

In the future, we'll be mounting small PCBs on traditional PCBs. My first thought is, "Cool! What will they think of next?"

But there are going to be ripple effects from this. What kind of thermal, signal integrity, and EMC issues will traditional PCB designers have to contend with 10 years from now when each board is essentially a system, comprised

of smaller, fully functioning PCBs? This takes DFM and DFT to a new level as well.

This is another example of the "blurring of the lines" concept that IPC President and CEO John Mitchell discussed in a recent installment of "Just Ask John Mitchell." The move to heterogeneous integrated modules won't be an overnight, quantum leap in technology development, but it will be disruptive.

For this month's issue on technology roadmaps, we bring you several interviews with HIR contributors. Rita Horner of Synopsys offers a great overview of the HIR and the effects of heterogeneous integration on the technology of the future. Paul Wesling of IEEE explains the creative process that leads to the development of the 584-page, 23-chapter HIR. Dr. José Schutt-Aine, professor of electrical and computer engineering at the University of Illinois, takes us through his chapter in the HIR and explains how PCB designers can facilitate co-design at the IC and package level. And Jeff Demmin of Keysight Technologies discusses the effects of heterogeneous integration on the military and aerospace segments.

We also have a conversation with Todd Westerhoff of Mentor, a Siemens Business, who details the company's plans for the highspeed design tools of the future. Michael Nopp of Cadence Design Systems discusses the company's move toward creating the next generation of more electrically-aware PCB designers, and Leigh Gawne of Altium provides a roadmap for the company and the Altium 365 platform, in particular. Carey Burkett and Mark Finstad of Flexible Circuit Technologies share their thoughts on the direction of the company and some of the trends and challenges likely to face flex designers and manufacturers over the next few years. And Joe Fjelstad explains why technology roadmaps are so vital to technologists working to develop the processes of tomorrow.

We also have columns from Barry Olney, Kelly Dack, John Coonrod, John Talbot, Jade Bridges, and Matt Stevenson and Bob Tise.

If you missed the virtual SMTA International 2020 show, don't worry. Visit Real Time with... SMTAI 2020 and check out our video interviews with the top engineers, managers, and executives who attended this event.

Stay safe, and see you next month. DESIGN007

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 20 years. He can be reached by clicking here.

# **Looking to Hire New Talent?**

D.B. Management Group L.L.C. is currently working with a group of professionals who are seeking new positions.

(i) <u>click to learn more</u> MANAGEMENT GROUP Strategic Business Growth Consultants

### Looking Into the Future With Progressive Design and Analysis

#### Feature Interview by the I-Connect007 Editorial Team

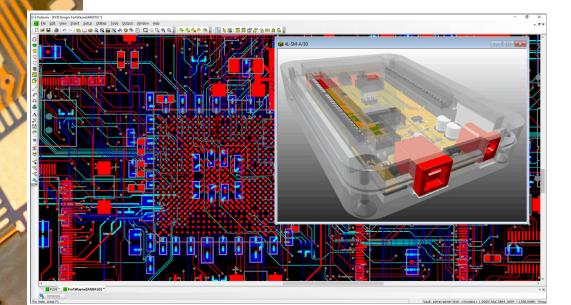

This month, we're focusing on technology roadmaps. We wanted to get a feel for the future of high-speed EDA tools, so we spoke with Todd Westerhoff, product marketing manager for high-speed tools at Mentor, a Siemens Business. Todd discussed the future of highspeed PCB design tools, as well as some of the many market forces that are driving the development of the company's tools and the overall EDA segment. He also details a new approach that Mentor is taking: progressive design and analysis.

**Andy Shaughnessy:** Todd, why don't you give us a look ahead at Mentor's high-speed tools and tie it in with what you see going on in the industry in the near future.

**Todd Westerhoff:** Thanks, Andy. When we met at DesignCon this year, we said, "It's the small stuff that gets you." We meant that if you look at what holds up design projects, it's often not the state-of-the-art problems you would expect. It's the stuff that you thought was straightforward that bites you in the end. As a design community, we're pretty good at

the complicated stuff because we pay careful attention to it, but we get can be tripped up on what should have been easy.

Most companies see signal integrity (SI) as too time-consuming or too complicated for system designers, so analysis gets put into the hands of dedicated specialists to make the process "more efficient." SI analysis then becomes concentrated at the end of the design cycle. Good post-layout verification will find problems before fab-out and avoid wasting money on prototypes, but you're still finding errors well past the point where they were introduced into the design. That means parts of the design have to be ripped up and rerouted, and there's a schedule impact associated with that. We want to give system designers tools where they can find and correct those errors as early as possible.

We need a class of analysis tools that will allow system designers to effectively evaluate trade-offs and make design decisions without having to get the SI expert involved. The accuracy doesn't have to be as good as what the expert uses—something we call first-order analysis. The goal is to look at things more qualitatively. We don't need to compute system margin down to millivolts and picoseconds on an absolute basis; we want to know how a

### Superior resins engineered for challenging environments

In Encapsulation Resins our comprehensive range meets the increasing demands of the electronics industry. Whether it's epoxy, polyurethane or silicone resin systems, our products are designed to protect and insulate printed circuit boards (PCBs) and electronic components from the threats of harsh and challenging environments.

Encapsulating the entire device in resin offers protection against moisture, vibration and rapid changes in temperature, thus offering superior performance under extreme conditions.

Whether for general purpose or tailored for individual requirements, every electro-chemical solution is within our spectrum. Our specialist approach to problems has established us as a key provider and developer to the technical electrical industry, both commercial and domestic.

Isn't it time you discovered how Electrolube can serve you?

Tel: 800-474-1472 www.electrolube.us

Electronic & General Purpose Cleaning

Encapsulation Resins Thermal Managemen Solutions Contact Lubricants Maintenance & Service Aids

Scan the code to discover our full spectrum of superior Encapsulation Resins and electro-chemical solutions.

THE SOLUTIONS PEOPLE

573 L. 19/2

change will affect signal quality and timing on a relative basis. We want tools that let system designers make more informed decisions on their own because the SI expert's involvement generally has to be scheduled, but the need to evaluate design trade-offs is constant. Giving system designers good first-order analysis tools means the design will be in better shape when the SI specialist looks at it, which helps reduce design spins.

**Shaughnessy:** Are you talking about having an analysis run in the background during the lay-out process?

**Westerhoff:** Not necessarily. Analysis is more useful as a "checkpoint" process, particularly at the interface level. There's not much point in running analysis on half of an interface; it's better to get to a point where the design has reached some level of completeness and then produces results quickly. After each checkpoint, you continue to refine the design and add detail, gradually predicting the system operating margin more and more accurately.

We refer to this process as progressive design and analysis. We're trying to match analysis to the way design normally takes place. You start by figuring out the big stuff and then add details as you go, checking your design each step of the way.

For this to work well, you need several things:

- 1. A repeatable analysis process that produces a numerical metric for system operating margin.

- 2. An established pass/fail threshold for system operating margin.

- 3. An ability to dial design details and physical effects in and out of the system model.

Let's take a closer look at each of these individually.

### **Analysis Process**

First, the analysis process and results have to be absolutely repeatable. Simulation isn't much good if you can't run the same analysis twice and get the same results. When you're assessing design trade-offs, you need to know that the simulation process you're using is rock solid, or you won't have much confidence in the design decisions you make. You want that process to be entirely automated so that you just define simulation parameters and the analysis process runs by itself, always producing the same results in the same format.

### **Pass/Fail Threshold**

Second, you need well-defined criteria for whether a design passes or fails. System operating margin can be specified in millivolts, picoseconds, decibels, or something else, but it needs to be specific, defined, and numeric, and it needs to match what the analysis process actually produces. That way, there's no ambiguity about success or failure and no ambiguity over which design alternative provides more margin.

### Variable Modeling Accuracy

Third, when we add more detail into a system interconnect model, the model takes longer to generate, and the resulting simulation runs slower. We don't need ultimate accuracy early in the design process when we're just roughing the design in; it slows the process down without adding much value. Matching the model detail to the task at hand will make the process more efficient. Equally important, being able to dial design details and physical effects in and out of the system model allows us to numerically quantify the impact they have on system margin. It doesn't make sense to spend a lot of time optimizing something that has a negligible impact, and the things that matter most will change from design to design. During active design, we want to focus on what matters most and optimize the design accordingly.

Progressive design and analysis means we use basic models at the start and add detail as we go. The level of detail in our model increases as the design progresses. Because we know there are things we're not modeling at any given point, there's an ambiguity, or "error band," in our analysis that's large at the start and small at the end. Thus, an analysis that exceeds the pass/ fail threshold by a small amount at the start of the cycle might fail with a more detailed analysis. It's important that we have a sense of how big that error band is, so we can interpret the results of any particular analysis appropriately. Generally speaking, we group analysis results into three categories:

**1. Green:** The design has a significant positive margin, even after accounting for the error band in the model. We could

perform a more accurate analysis to get a better assessment, but we may not need to. The design might be ready to fab-out as-is.

**2. Red:** The design has a significant negative margin, even considering the error band. The chances are that the design is broken, and something needs to change. Even though we could perform a more detailed assessment, it's probably best just to figure out what's wrong with the design and fix it.

**3. Yellow:** The degree of positive or negative margin is within the error band, so we're not really sure whether the design will work or not. A more detailed analysis is needed to be sure.

Process efficiency rises when the analysis result is green or red. In either case, the need for a more detailed analysis has been delayed, and design work can continue in the meantime.

This doesn't eliminate the need to perform a complete post-layout verification before fabout, and to have that verification performed by a SI expert. This final "gate" to fab-out is proven and valuable. The goal is to improve the quality of designs being passed to SI experts for verification so that fewer design changes are needed.

**Shaughnessy:** Are you saying you shouldn't have to be an analysis specialist to perform SI analysis?

Todd Westerhoff

**Westerhoff:** Exactly. Let's look at what happens in actual practice with DDR4 as an example. A lot of companies lay out their DDR4 designs based on the controller manufacturer's recommendations and then pass the layout back to the silicon vendor for review. Silicon vendors can't afford to set up and run detailed post-layout verification for all the designs customers want to pass their way, so they need to develop good design "screening" to find common problems. Think

of it as trying to find 95% of the problems with 10% of the effort of a full postlayout analysis. Those screening efforts typically take one of two forms:

**1. Automated electrical rule checks:** These go beyond simple physical rule checks to include things like trace impedance, the proximity of return path vias, etc. The silicon vendors configure rules for their specific device technologies, allowing them to do the same screening an experienced designer might do, but much faster.

**2. First-order simulation:** Design volume and turnaround time make this simpler than what the vendor would use internally for sign-off. For example, the process might simulate data nets with generic technology models, computing a delay and figure of merit for each signal's quality. This simulation can be run quickly to identify any discrepancies between signals in a data bus.

The question becomes, "If the silicon vendors are already doing this type of screening on the designs customers give them for review, why not put those same processes directly in the hands of customers themselves?" That's what we're looking to do.

We already offer comprehensive electrical design rule checking, and we're bringing out a first-order pulse response analysis patterned after the techniques some of the silicon vendors use. You don't need any simulation model at all. You load your design, set up the analysis parameters, and run. You can have simulation results within five minutes that give meaningful insight into what, if anything, you should change in your design.

As an industry, we keep getting caught up in the idea that an analysis tool has to do everything with maximum accuracy to be useful. We think that if a tool can meet the needs of the most demanding experts, it will work for everyone, but that's not really true. The "expert" tools are often standalone applications that users string together to form their own analysis flows. The typical system designer doesn't have the time to learn yet another complex tool, let alone multiple tools and a way to string them together. We need focused toolsets that let designers perform basic analysis quickly and that don't have a huge learning curve.

### We need focused toolsets that let designers perform basic analysis quickly and that don't have a huge learning curve.

Five years ago, 25-gigabit serial links were the hardest thing going, and you needed the best people in your organization working on them. Today, we're trying to put them in mass production across scores of designs. How are all the teams trying to deploy this technology supposed to get their work done? The experts have all moved on to 112-gigabit links, and they're busy doing that. I think the real challenge is, "How we deploy these advanced technologies once they've been proven?"

**Shaughnessy:** Do you see your typical users being degreed engineers?

**Westerhoff:** Let me change that question a bit. I think the challenge is, "Are the people running SI analysis dedicated specialists?" The unfortunate truth is the majority of designs still don't get simulated in any significant way.

HyperLynx has enabled a lot of people who aren't SI experts to run their own analysis. Our goal is to expand that pool of people because that's what the industry needs; the shortage of SI experts isn't going away anytime soon.

**Happy Holden:** Todd is preaching the gospel, based on the time that I spent at Mentor earlier in my career. But this is everything from modeling to simulation to the trade-offs. It was tough 20 years ago, but it's much tougher now.

**Nolan Johnson:** I spent my time in Mentor championing what we now call the digital twin—a brilliant design advisor that allows the user to make some high-level trade-offs between costs, productivity, thermal, SI, etc. early enough to keep you from running down the wrong alley. Whether or not you know anything about SI, Mother Nature is conspiring against you with very fast transistors. You can set the clock, but you can't change the fundamental characteristic of that transistor, which is going to turn on and off pretty fast.

**Westerhoff:** The phenomenon of high-speed behavior on slow-speed signals is very real. One of the common rules of thumb is that you need to consider a net as "high-speed" whenever the delay of the net exceeds one-sixth of the driver's edge rate. Consider what that means for a driver with a 250 ps edge rate, which is pretty slow by today's standards. The longest a net could be and not be considered high-speed would be about 42 ps or roughly one-fourth inch. That means pretty much everything is high-speed unless you're dealing with old driver technology on an old process node.

**Johnson:** And you can't escape it because, like death and taxes, Mother Nature is going to keep making things smaller and smaller, which favors SI, and we can't breed the SI gurus fast enough. We have to figure out how to simplify the first order to get you 80% there.

**Westerhoff:** We've been talking about simulation and modeling for as long as EDA has existed, assuming that the design community

would keep pace if we could provide tools with the right capabilities. In the SI space, at least, the shortage of experts isn't getting better, and it's time to do something different. We have tools for the experts; now, we need tools for the broader community and examples of how to apply those tools to common design problems.

We provide user workshops that show how to apply HyperLynx to a typical design problem. My point here is that training and education are just as important as the tool capabilities themselves, especially when we're talking about a broad audience. We've been conditioned to think about which things are critical when analyzing a high-speed serial link, but most of our input has come from people practicing at the state of the art. In our 25-gigabit serial link workshop, for example, the effect of surface roughness just doesn't matter that much. It's case-dependent, of course, but that's the point. Showing people how to isolate and quantify the different things that affect system margin is every bit as important as having the capability to do that analysis. How are people supposed to know what to do if you don't show them?

We all have these ideas about what matters and what doesn't based on what we've been told, but sometimes the actual results are quite surprising, providing additional opportunities to optimize a design.

**Holden:** The overall truth is that two things are conspiring against us. The first one is the schedule. Nobody's going to let us expand the schedule. They constantly seem to shrink because of time to market and who gets there first. The second thing is complexity. To attract customers, everything has to have more features and be more complex.

**Johnson:** You're absolutely right in terms of schedule. If you bring basic analysis to the desk of the engineer, you helped your schedule by a large amount. If you can put basic tools in that designer's hands, they can make a lot of those decisions. You'll actually win some on schedule there.

**Westerhoff:** I think it's a diminishing return problem. How much can we accomplish if our analysis accuracy is at the 90% level? A lot. If we defer all analysis until the end of the design, we run the risk of finding mistakes that will blow the schedule. When it comes to design analysis, we're saying less is effectively more.

**Shaughnessy:** Less information available quickly is better than 100% of the info two weeks from now.

**Westerhoff:** Exactly. Let's be clear; we're not saying that we don't need SI experts doing what they're already doing because we do. We're arguing that most designs have an "analysis valley" in the middle of the design cycle, where systems designers can't get the feedback that they need. Putting design-oriented analysis tools in their hands will enable them to make more informed design decisions and help offload the SI experts from what is probably the worst part of their jobs, running post-layout verification on other people's designs.

**Holden:** Mentor and Siemens have access to much of the electronic design space. Do you work with the thermal analysis or placement and routing side teams to help designers juggle the multiple balls that have to be kept in the air?

**Westerhoff:** Absolutely. That's a natural extension of everything that we've discussed here. The problem isn't unidimensional anymore; it requires balancing electrical, mechanical, and thermal trade-offs. How do you extend this design-oriented analysis strategy to play across all those disciplines? That's where we need to go next. Perhaps we can talk about that the next time we meet.

**Shaughnessy:** This has been really interesting, Todd. We appreciate your time. Maybe we'll see each other "live" again.

**Westerhoff:** Thanks for the discussion. This has been great. It will be nice to talk in person again. **DESIGN007**

# **Fringing Fields**

### Beyond Design

by Barry Oiney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

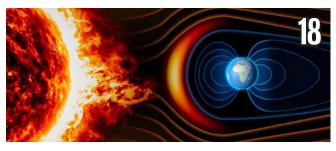

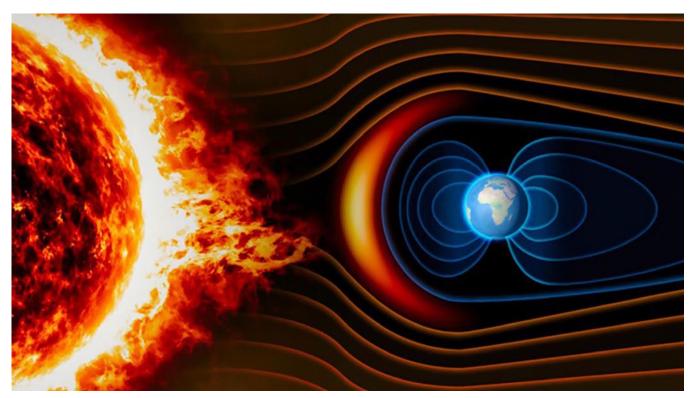

Electromagnetic energy is all around us from TV to radio and communication waves and the Earth's magnetic field and plasma shield that protect us from the sun's solar flares (Figure 1). This activity is driven by the sun's magnetic field. Like all physical phenomena, they tend to follow the same rules.

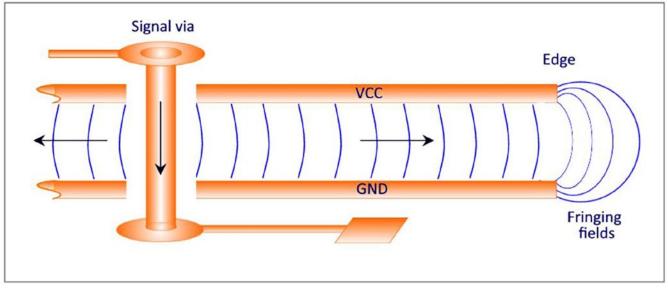

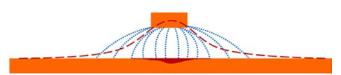

A parallel plate capacitor (or a planar pair) has two conductors separated by a dielectric layer. Most of the energy in the structure is concentrated directly between the plates. However, some of the energy spills over into the area outside the plates. The electric field lines associated with this effect are called fringing fields. In this month's column, I will look at how electromagnetic radiation can be emitted from the edges of planes in multilayer PCBs by the fringing fields, possibly causing electromagnetic compatibility (EMC) issues.

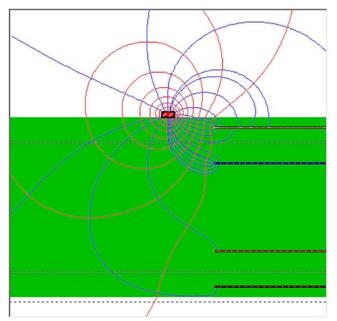

Fringing is the bending of the electric flux lines near the edge of the parallel plate capacitors. Fringing is also known as the edge effect. Normally, the flux lines inside the capacitor are uniform and parallel. But at the edges, the flux lines are not straight and bend slightly outward due to the geometry. Also, in a plane pair, signals passing through the cavity may intensify fringing fields (Figure 2).

When the return current flows through the impedance of a cavity between two planes, it generates voltage. Although quite small (typically in the order of 5 mV), the accumulated

Figure 1: The sun's corona discharge (solar flare) and Earth's magnetic field.

### LEAVING THE OTHERS IN OUR DUST BY INVESTING IN SPEED & TECHNOLOGY

While others struggle just to keep pace, we stay ahead of the curve by constantly investing in the equipment, people and resources needed to be the best total PCB solutions provider in the industry.

VIEW OUR CAPABILITIES

Figure 2: Signals passing through a plane cavity intensify fringing fields.

noise from simultaneous switching devices can become significant. Unfortunately, as core voltages drop, noise margins become tighter. This voltage, emanating from the vicinity of the signal via, injects a propagating wave into the cavity, which can excite the cavity resonances or any other parallel structure (for instance, between copper pours over planes). Other signal vias, also passing through this cavity, can pick up this transient voltage as crosstalk. And when the wave meets the PCB edge, the two reference planes form a slot antenna and will radiate noise with the potential to generate electromagnetic interference (EMI) to nearby equipment.

The more switching signals that pass through

the cavity, the more noise is induced into other signals; it affects vias all over the cavity, not just the ones in close proximity to the aggressor signal vias. This cavity noise propagates as standing waves, spreading across the entire plane pair. This is the primary mechanism by which high-frequency noise is injected into cavities by signals transitioning through cavities, using each plane successively as the signal return path.

Cavity resonance also affects the power/signal return layers at the edges of the PCB. Edge effects can be particularly problematic since it is the board edges that are in such close proximity to the chassis; hence, the radiation fields can induce currents into the chassis frame.

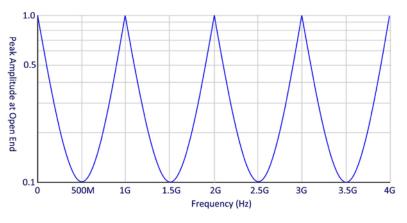

When the cavity has open end boundary conditions, resonances arise when a multiple of half wavelengths can fit between the ends of the cavity. Figure 3 shows the cavity resonance of a plane pair with a resonant frequency of 1 GHz. If the signal clock frequency (or harmonics) are multiples of 1 GHz, then noise can be injected into the plane cavity. When the clock or data harmonics overlap with the cavity resonant frequencies, there is the potential for long-range coupling between any signals that run through the cavity. This is one reason

Figure 3: Amplitude at the far end of planes as input frequency is swept. (Source: Eric Bogatin)

why all return planes should be GND layers so that stitching vias between GND planes can be placed adjacent to each signal via transition to minimize the possibility of exciting the cavity resonance.

Cavity resonances are (at first) a signal integrity issue, but the amplification of cavity resonance excited by fast rise time signals at high frequencies can also contribute to electromagnetic emissions. The frequency components of the voltage noise are related to the peak impedance of the cavity and the frequency components of the return currents. In any complex system, with typical interconnect density, avoiding signal layer transitions is not practicable and is an issue that designers must live with. However, one can learn to avoid injecting excessive noise into the cavity or at least minimize the impact.

Figure 4 gives an example of a signal trace on the top microstrip layer routed outside the reference plane area. I see this all the time when I analyze PCBs. The signal path is very close to the edge of the PCB, and the reference planes are not located directly under the trace to provide full field coverage. The electric fields (blue) tend to couple to the plane edges, whereas the magnetic fields (red) radiate outward omnidirectionally. The fringing effect

Figure 4: Trace routed outside the reference plane area (simulated in HyperLynx).

Figure 5: Microstrip plane return current distribution.

creates a very "hot" area and will radiate and possibly create coupling issues to nearby circuits, cables, and slots in enclosures.

Figure 5 illustrates the cross-section on a microstrip trace, and its associated plane return current distribution (red). Where the electric fields (blue) are more tightly coupled to the plane directly below the trace, the return current also exhibits tighter coupling. But where the field spreads out from the trace, the larger loop area between the signal and the return current path increases the inductance.

Return current tends to couple to the signal conductor, falling off in intensity, with the square of increased distance. A stripline (inner layer) return current distribution is narrower with the fields more intense above and below the trace. The electric field spreads out to approximately three times the width of the trace (on both sides), so it is important to ensure there is enough plane coverage to prevent radiation.

To reduce emissions and increase immunity, when routing a PCB, try to avoid positioning critical signals close to the edge of the board. This creates a more robust system for electromagnetic compatibility.

There are various approaches pertaining to reducing radiation edge effects from the PCB. In many cases, energy can be reflected, possibly creating additional internal cavity resonance effects and coupling to internal vias, also resulting in increased radiation. When plane pairs resonate, their emissions come from the fringing fields at the board edges. With ground/power plane pairs, edge-fired emissions can be reduced by reducing the plane separation and lowering the AC impedance. Alternatively, make the power planes slightly smaller (~200 mils) than the GND plane. This modifies the pattern of the fringing fields, pulling them back from the edge, and may help reduce emissions to some extent.

Edge plating, as the name suggests, is the process of plating the edges around the PCB. I first saw this technique used at NEC back in 1994. This is an elegant (but expensive) solution to prevent emissions from extremely high-speed SERDES signals on terabit routers, etc. but is an overkill for a typical high-speed design.

Another way to mitigate this problem is to create a via fence stitched to ground around the perimeter of the PCB. If the spacing between the stitching vias is less than or equal to oneeighth of a wavelength, the via fencing will appear as a short circuit, causing the propagating wave to be reflected back to the source rather than being launched from the PCB edge.

A post-production solution is to employ cavity resonance absorber material applied along the edge of the PCB, which dissipates the edge radiation from the PCB without using additional board real estate. It also reduces the possibility of board resonance problems by dissipating the energy and not reflecting the energy back into the interior of the board. However, it is always best to fix the problem at the source rather than applying as a quick fix after production.

#### **Key Points**

- Fringing is the bending of the electric flux lines near the edge of the parallel plate capacitors.

- A signal passing through a plane cavity may intensify fringing fields.

- As core voltages drop, noise margins become tighter.

- Signals passing through a plane cavity inject propagating waves, which can excite the cavity resonances.

- When the wave meets the PCB edge, the two reference planes form a slot antenna and will radiate noise.

- The cavity noise propagates as standing waves spreading across the entire plane pair.

- When the cavity has open end boundary conditions, resonances arise when a multiple of half wavelengths can fit between the ends of the cavity.

- Return current tends to couple to the signal conductor, falling off in intensity with the square of increased distance.

- Avoid positioning critical signals close to the edge of the board.

- Edge plating is an elegant (but expensive) solution to prevent emissions from extremely high-speed SERDES signals.

- GND stitching vias are placed at one-eighth of a wavelength as a short circuit, causing the propagating wave to be reflected back to the source.

- Edge radiation should be eliminated at the source. **DESIGN007**

### **Further Reading**

- Barry Olney, "Beyond Design: Plane Cavity Resonance," The PCB Design Magazine, September 2017.

- Barry Olney, "Beyond Design: Mythbusting— There AreNo One-Way Trips!" The PCB Design Magazine, April 2014.

- Barry Olney, "Beyond Design: The 10 Fundamental Rules of High-Speed PCB Design, Part 3," Design007 Magazine, November 2018.

- Basu (VU2NSB), "Solar Activity and Ionosphere," VU2NSB, November 19, 2019.

- Arturo Mediano, "Avoid Critical Signals in Edges of the PCB" In Compliance, December 27, 2018.

- Bert Simonovich, "Controlling Electromagnetic Emissions From PCB Edges in Backplanes," Signal Integrity Journal, January 18, 2017.

- Mast Technologies, "Reducing PCB Edge Fringing."

- Larry D. Smith and Eric Bogatin, *Principles of Power* Integrity for PDN Design—Simplified, Pearson, March 2017.

- Eric Bogatin, "What is the resonant frequency of a cavity? Rule of Thumb #30," EDN, July 19, 2016.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in board-level simulation. The company developed the iCD Design Integrity software

incorporating the iCD Stackup, PDN, and CPW Planner. The software can be downloaded at icd.com.au. To read past columns or contact Olney, click here. Create Comprehensive PCB Documentation to Drive Fabrication, Assembly and Inspection

# **BluePrint-PCB**

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings, successfully driving the procurement, fabrication and assembly process.

- 3D technology allows visualization of imported CAD data as a 3D PCB

- Lowers documentation cost and time

- Increases documentation detail & accuracy

- Shortens PCB design cycles

- Reduces documentation time by 60-80%

- Improves manufacturing & simplifies inspection

Download your free e-book "The PCB Designer Circuit Designer's Guide to Assessing Your PCB Documentation Process"

**CLICK HERE TO DOWNLOAD**

This book, written by Mark Gallant of DownStream Technologies, explains how an automated documentation solution like BluePrint-PCB<sup>®</sup> can eliminate post-processing errors and speed up time to market.

This book is a must-read for any PCB designers or design engineers who would like to adopt 21st-century PCB documentation processes.

### For more information visit downstreamtech.com or call (508) 970-0670

©2019 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

### How Designers Can Help Facilitate Co-Design

#### Feature Interview by the I-Connect007 Editorial Team

José E. Schutt-Ainé is an electrical and computer engineering professor at the University of Illinois, Urbana-Champaign, and a contributor to the Heterogeneous Integration Roadmap (HIR). In this conversation, José gives Nolan Johnson and Andy Shaughnessy an overview of the co-design chapter he co-authored in the HIR, the motivations behind advances in codesign, and why designers are the real drivers who must decide what is needed in EDA tools to facilitate the process of co-design.

**Nolan Johnson:** José, start by telling us what chapter of the HIR you were involved with.

**José Schutt-Ainé:** I was involved with Chapter 13, which is the co-design chapter, and that is supposed to be an extension of the modeling and simulation chapter. Initially, the co-design effort was part of the modeling and simulation, but we decided that in the context of heterogeneous integration, it had to be taken separately.

We look into the traditional methods that have been in use for co-design. We need to think about what's going to happen in the next 10–20 years and how co-design will affect future types of designs like neuromorphic computers or quantum computing, etc. We start with the traditional co-design methods, and we discuss what the challenges are. Co-design involves putting together different types of simulation tools. Placement and routing are very different than electromagnetic instruction, which is very different from circuit simulation.

How do you get these tools to talk to each other in optimizing a design? We also look at the domains, the chip, package, and board. How do they coexist? How do you transmit information from one domain to the other in a seamless manner? And how is it done traditionally? We looked at that, and then this led to pathfinding, which is considered as the ultimate method for doing co-design. Pathfinding not only optimizes the design itself, but it also looks at other considerations, such as cost and performance. We had a section devoted to that. We also looked at the impact of co-design and architecture. How do you want to design your

Because failure is not an option.

In your daily life you are dependent on a lot of products. The car you drive, the airplane you fly in or the ECG equipment measuring your heart. You expect them to work – because they have to.

All electronic products have a PCB inside. At first sight they may all look the same. But it could be a world of difference between a normal and a High Reliability PCB.

**High Reliability PCBs**. Because failure is not an option. computer in the future? How do you want to manage issues related to cache, memory, and processing? For each of these sections, we had different experts write various sections.

After that, we move to the future technologies like silicon photonics. How is that going to be affected by co-design? How can co-design improve silicon photonics? The more futuristic stuff was at the end of the chapter, where we addressed things like neuromorphic computers and quantum computing because they definitely will necessitate some type of co-design for their inception.

**Shaughnessy:** In the co-design chapter, you all talk about how EDA tool vendors now offer PCB design tools with packaging design functionality. Do you see that more often?

**Schutt-Ainé:** It all depends on who you talk to. What is heterogeneous integration? People think that Moore's law is going to run out of steam eventually. This whole idea of getting a new node every 18 months, people anticipate that at some point, it's going to come to a halt. Instead of cramming more components into one chip, you're going to have more creative methods for combining not only the different domains but also various levels—namely package, chip, and the board—and technologies. How do you combine them?

### What is heterogeneous integration? People think that Moore's law is going to run out of steam eventually.

What happens in optics is not necessarily compliant to Moore's law. At the same time, when you look at what happens at the PCB level, the components will scale according to the wavelength but not the technology. Things get smaller only as the frequency goes up. It's like you're dealing with different rules, and that's the whole idea. That's the impetus behind heterogeneous integration.

However, last December, I was at a conference in Taiwan, and that's where TSMC is. They don't seem to buy into HIR with the same level of enthusiasm as people do in other places, like they do in the U.S. In Taiwan, people really believe in Moore's law. According to them, when Moore's law stops, the impact on their economy will be quite visible.

**Shaughnessy:** One section explains how simulation has to move from a 2D view to 3D.

**Schutt-Ainé:** For instance, with 3D chips, there's a whole host of issues coming as a result of the third dimension. The thermal issues are going to become more serious. In the first version of our chapter, we did not have the electrical-thermal aspect included, but we just included that last month. The next version of the chapter will include a whole section on electrical-thermal co-design, and it touches on issues related to 3D. Removing the heat on the treated chips is a big challenge. Modeling is also a challenge.

**Johnson:** Depending on what you load inside, the package is going to change the thermal characteristics, which you then need to accommodate on the PCB. There's a lot happening.

**Schutt-Ainé:** I look at co-design as an enabler of heterogeneous integration. Our focus is more on what the EDA companies should be doing. What kind of tools should they be making available to the designers? It's a difficult task because you're looking at combining very different types of algorithms. There's also the database. How do you manage the information? The chip information is managed in one way, and the database is usually managed in a certain format. The package level is in yet a different format, and then there's the board level. How do you make all of that? How do you ensure good communication between the three different levels?

On the circuit side, you start with Maxwell's equations to help predict how the waves are

going to be interacting with the components. On the other side, you have placement and routing algorithms that have nothing to do with physics, but rely more on math principles such as statistics and graph theory. How do you optimize the placement? All of those things have to work together, which is the challenge.

In the end, you have your package that you place on an EDA tool. You put it on a tool like the major vendors. They get that. As of now, they have some offerings, but we're working on the roadmap. We're trying to figure out what it is that's going to be needed in the next 10–20 years. What they're doing now is more to satisfy the current needs of their customers.

**Johnson:** That's one of the places where the roadmap makes sense. That may not be the best way to frame the question. But one of the reasons for the roadmap is to give a long-term vision to part of the industry, such as the CAD tool sector, to help them understand what it is they need to put in with staff for development. What has the response been so far?

**Schutt-Ainé:** My experience is limited as far as my interactions with the EDA people, but they are very customer-driven. If you come up with a new idea, such as, "Here is this thing that you could use to design a quantum computer," they probably would not be excited by something like that because they don't have any customers right now that have that demand. They are always more excited by what customers are asking for. I don't know how you fix that, but most of what they put out is based on customer demand.

For instance, machine learning is a very exciting discipline right now in academia, especially for design. But it's a difficult sell to the EDA vendors because they're not getting that request from the consumers, from the customers. They tend to want more traditional things. It has always been my experience. Usually, that comes from the demand that they get from the customers.

**Johnson:** The readership that should create the demand for your audience is probably reading

Chapters 5, 6, and 7 around the application. This is where things start to dovetail. How do you coordinate those messages in the roadmap with your messages?

**Schutt-Ainé:** What would trigger the EDA vendors to get more on board is if you had the actual manufacturers and designers of these futuristic systems putting things together, say-

ing, "We need a tool to do that." Let's say you want to do an optical SerDes working 56 gigabits per second or even higher. They're talking about 128 gigahertz per second. I don't think that you have a commercial tool that can do that,

José Schutt-Ainé

especially if it combines optical with electrical components. But if you have an active program or designer looking into doing it and there's a budget for it, that would get the EDA vendors on board.

**Shaughnessy:** One thing you pointed out was that everything, including simple things like the data formats and types for packages and boards, is completely different than those used at the IC level.

**Schutt-Ainé:** PCB designers also have to learn about electromagnetics. The clock rates are getting faster, and the end result is that the signal that goes to your PCB is more like a microwave signal. Component dimensions are comparable to the wavelength, which means that the wire is not just a simple wire; it's a transmission line. The physics are completely different because it behaves like a wave. In the mid-'90s, I traveled a lot, giving basic electromagnetic courses to PCB designers. They didn't worry about that in the '70 or '80s because the clock rates then were relatively slow. Things started changing in the late 1980s. At the same time, they were working on things where the clock rates were approaching the gigahertz range. You had to think of everything as transmission lines.

**Shaughnessy:** When top PCB design instructors like Rick Hartley, Lee Ritchey, and Eric Bogatin teach, they say every wire and every trace is a transmission line, and you have to put it that way, or you'll be out of luck. With the rise times and speeds, everything is so fast, and there is no leeway.

**Schutt-Ainé:** But that's more at the PCB or package level. The chip is a different story because everything is so small. You don't worry too much about inductance or radiation or antenna type problems. The chip is going to be mounted on your package, and the chip is going to be running really fast.

**Shaughnessy:** It seems like it's even more of this system-level awareness. Almost every-body involved in designing or building a circuit board must have a system-level outlook, or they're not going to be able to make all the right decisions.

**Schutt-Ainé:** And it's going to become harder. In the course I teach, I always give the student this perspective. Look at a cellphone, for instance. With a typical design, back in the day, the voltage was 12 volts, and then it went to five volts, then to 3.6, 1.8, and 1.2. Now, it's coming down to even lower than one volt. The reason you're lowering the DC supply voltage is that you want low power, long battery life, and low power dissipation. But it makes the job a lot harder for the designer because the voltage budget is now very small. You need to have everything done within one volt. Even with a 0.6-volt drop, just running from the power supply to the power rail is bad news.

**Johnson:** Let's transition to talking about your presentation.

**Schutt-Ainé:** Sure. This is a modified version of the webinar that I gave two months ago as a chapter overview. We've had some discussions about the motivations for co-design, and

as we outline the application, the designers are the drivers. They have to decide what is needed in those tools to somewhat facilitate the process of co-design, such as data centers, IoT, automotive, etc., and especially things like SerDes and high-speed links. I highlighted those two because a lot of what I do in my research relates to these applications. The way our technical working group was structured is we wanted the chapter to address some of the questions listed. What is the state of the art in co-design? What will drive the creation of these tools? What will the challenges be? How much value will having co-design tools add to HIR? How will all of this happen in the next five to 10 years?

Traditionally, co-design is how you manage the chip, package, and board together. The chip level is very different than the package or the board. At the chip level, you worry about transistors, and their operation is highly nonlinear. MOSFETs are nonlinear devices, and with the tools used for verification like SPICE, it's important to notice that the scaling takes place with technology. Essentially, they follow Moore's law. By contrast, with the package into the board level where things don't follow Moore's law, the scaling happens with the electromagnetic wavelength.

Going to the board level, it is very similar to what you get at the package level, but you get additional tools because the dimensions are higher, so the electromagnetic extraction tools become more important. Given the fact that you may be dealing with different types of chips from different vendors, you need to have a way of handling the nonlinearities. For instance, the IC's form has come into play.

The goal is to combine all these domains and develop a successful flow. People talk about vertical or horizontal co-design, but the vertical one is when you go from one domain to the other. Co-design is when you make sure you are aware of many different constraints. You're going from chip to package to board, but you are also incorporating constraints related to security, test, and thermal. All of those also have to be integrated, which will make the process a lot more complicated.

### Because failure is not an option.

In your daily life you are dependent on a lot of products. The car you drive, the airplane you fly in or the ECG equipment measuring your heart. You expect them to work – because they have to.

All electronic products have a PCB inside. At first sight they may all look the same. But it could be a world of difference between a normal and a High Reliability PCB.

**High Reliability PCBs**. Because failure is not an option.

Traditional co-design requires trade-offs. You need to be aware of what those are, and you need to understand the trade-off at the chip level, as well as how it will impact the implementation at the package level. I've talked about formats, translations, and domains, which are important, too. How do you propagate information? If you have mapping at the chip level, what is that going to correspond to-the package or the BGA? Being able to propagate the information properly is part of the challenge. Managing connectivity is somewhat related. We also talked about the database format. We're looking at the board, package, and chip, all of that has to be done in a seamless fashion.

### We're looking at the board, package, and chip, all of that has to be done in a seamless fashion.

We also identified other challenges, such as multi-physics, thermal awareness, and mechanical constraints. Sometimes, you combine electrical with optical. The idea is that these are different domains where the scales and resolutions related to physics are very different. What's big in the optical domain may end up being very small in the microwave or electrical domain. And the design rules are different. One thing you will observe is that the tools are old and slow, meaning how long it takes to develop new algorithms is a lot longer than how quickly new technologies come into play. Some of the proposed solutions have been somewhat successful, such as behavioral and macro modeling. I talked a little bit about that earlier when I mentioned model order reduction. This has been quite successful in reducing complexity.

Statistical modeling is also helpful because, given the fact that the performance of these systems is highly sensitive with respect to small variations, the best way to handle those is really to perform statistical analysis. We talked about AI, and although we're looking at quantum computing as a potential application to co-design, if quantum computing ever becomes a reality, it could facilitate co-design.

One slide shows how things have evolved over the past 20–30 years. In the old days, wire on a PCB used to be considered as a simple capacitor. But as the clock rates increased, you had to use that same wire at that same channel that had to be treated differently. Over the years, the tools had to implement transmission line simulators in order to describe how a signal travels from point A to point B. Today, a channel is even more complicated because, in addition to transmitting the information from point A to point B, you also have to provide equalization.

When you clock in at a very high speed, the nature of the channel is much more complex than the simple wire. A good example is the SerDes. Imagine having two chips that are mounted on the board, and the two chips both have 256 pins. You're not going to be able to connect 256 pins from one chip to the 256 of the second chip. What do you do? You need to use a SerDes, and you need to somewhat select those wires and serialize them. You take them 16 at a time, and you use only one wire to transmit the information from those 16 pins. This means that you need to multiplex the information, serialize it, transmit it, and then de-serialize it when it arrives at the other end. Consequently, transmission must be done 16 times faster. That's a design of SerDes that is a very complex and demanding operation. Yet people have them working at these speeds, like 12.8, 4.4, and 25.6 terabits per second for the optical implementation. It's very ambitious.

Then, there's placement and routing. Again, this is a very different world because it has nothing to do with modeling and simulation; it has to do with optimizing how you're going to lay out your system. Where should the bumps be placed? Where would we expect to put the gate, and what's the best way of rerouting the wires? Placement and routing are very different for me, and modeling and circuit simulation are a different game. We're talking about using Maxwell's equations to extract the electrical components of the system, as well as using circuit theory to predict how the voltages and the currents are going to behave on a circuit that typically may have tens of millions of transistors. That's the challenge.

That's where pathfinding comes into play. Pathfinding is the solution to co-design in the sense that once you put everything together, you have something that you can refer to as a pathfinding methodology. Some of the things it will do include unified workflow, partitioning, floor planning, the capability to create the abstract package models, etc. As you optimize the process, you also optimize the cost. Somehow, the cost has to be thrown in, and the knowledge of the existing technologies that are available to you must be implemented in the pathfinding methodology, as well as enabling the interaction of the design tools from the different EDA vendors. Those are the key components that we examined. There's also a new section added for thermal-aware co-design. We have a section on co-design for architecture and silicon photonics. We also have this matrix that describes the interaction between the different chapters, which is very important.

The presentation also shows what the priorities are. We come from the simulation group, so co-design must have a tight interaction with simulation, and then there's IoT, 5G, and RF. Automotive co-design can play a major role.

**Shaughnessy:** This has been very helpful. Thank you for your time and insights, José.

**Schutt-Ainé:** I'm glad to know you find it useful. The difficulty with putting this together is that most of us are experts in only one discipline, so trying to assemble a group of experts to write on co-design is hard. In my case, I don't know much about placement and routing, so I had help from co-writers. **DESIGN007**

### **Purdue Team's PCB Design Improves Electric Guitars**

What makes a guitar electric? With a skilled person playing, any performance can be powerful, but for the moment, consider the mechanical aspects of the instrument itself.

Traditional electric guitars have a "pickup," a magnetic transducer made with miles of copper wire coiled around magnets via a tedious, time-consuming process.

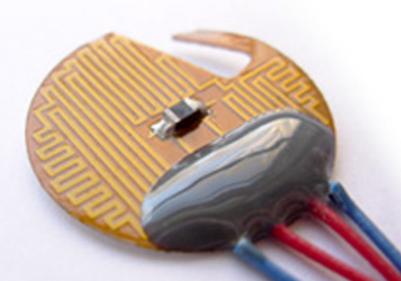

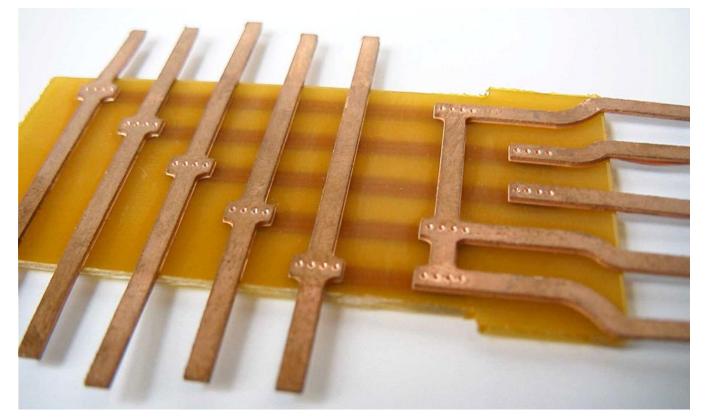

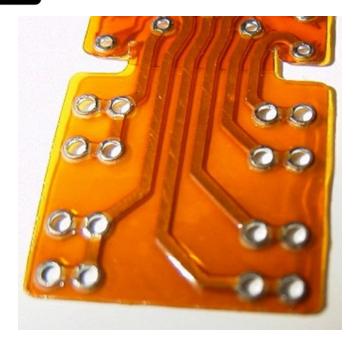

Purdue Polytechnic's Davin Huston and Mark French, along with Kathryn Smith, a former graduate student in Huston's lab, have been studying ways to improve the process, making the finished products better for both players and manufacturers. They created a flexible, printed circuit board that imitates the conventional copper wire configurations inside electric guitars.

"We came up with a new approach to the electric guitar pickup, the magnetic transducer that helps create the musical sound," said Davin Huston, assistant professor of practice in engineering technology. "Our circuit boards can be printed in large quantities and fit inside just about any electric guitar, which simplifies the manufacturing process but keeps the sound quality and reliability." With a conventional electric guitar pickup, string vibrations cause the electromagnetic field to oscillate, induce a voltage in the coil, and generate an electric signal. The team's circuit board works the same way.

"With typical pickups, the wire coils often produce undesired feedback and need to be potted with wax or a polymer," said French, professor of mechanical engineering technology. "Our circuit board provides an alternative that is easier to produce with manufactured consistency."

Davin, French and Smith worked with the Purdue Research Foundation Office of Technology Commercialization to patent the technology. A U.S. patent has been granted. (Source: Purdue Polytechnic)

### Unraveling the Mysterious BGA Routing Mess

### **Connect the Dots by Bob Tise and Matt Stevenson**, SUNSTONE CIRCUITS

A ball grid array (BGA) device can be a daunting component to route, especially in fine-pitch arrays featuring solder ball counts in the hundreds and pitch values as tight as 0.5 millimeters. With so much new technology requiring high-functioning processors and boards in increasingly miniaturized devices, it's safe to say higher pin density, reduced lead inductance, and finer-pitch BGA devices will become even more common in our industry.

That means the foreseeable status quo will be less and less space to route traces and vias between pins. BGAs represent a challenge from design through prototyping and manufacturing, but with some sharp attention to detail and a plan focused on best practices, this is by no means an impossible task. Let's look at how you can take the mystery out of BGA routing and create a PCB design that can handle all those pesky narrow spaces.

### Start With a Little Research

BGAs have been around a while, so there are many resources available to provide some guidance and help you not to reinvent the wheel. There are some good online resources that can be very helpful, such as YouTube videos, blog posts, and technical papers. Most of these resources are free to access, leaving you to sift through the marketing noise and extract available learning that will be useful to you.

#### Know Where Trouble Can Lurk

Solder joints are where you really need to mind your Ps and Qs. Smaller surface areas reduce the strength of the solder connection and increase the risk of fracture. Thermal issues can create flex between the component and board and put additional stress on the solder joints. Keep this in mind as you conduct research into BGA best practices.

#### **Vet Your Information Sources**

Device manufacturers will often have helpful information on their websites, such as routing examples and land patterns. Typically, the part manufacturer's footprint is optimized for soldering the part to the board but can leave you with an impossible routing solution. It's important to learn when to follow their guidance and when to improvise in the name of manufacturability and functionality.

In most cases, it's acceptable to reduce the BGA pad size sufficiently to allow for vias between

### Pulsonix PCB Design Software PCB design done right

### **Maximum Productivity in Minimal Time**

With a modern, easy-to-use interface and advanced capabilities to automate your layout process, Pulsonix can be the key to a critical reduction in your design time. That's PCB design done right!

### **Advanced PCB Design Features**

- Intuitive placement and routing

- Dynamic copper pour

- Full rules engine for automatic DRC

- High-speed design rules

- Heads-up display length matching

- Rigid-Flex, embedded components, and chip-on-board

- Revision control and PLM integration

Try Pulsonix yourself at pulsonix.com/trial

Figure 1: BGA solder.

the BGA pads. Typically, the BGA pad can be reduced to the same diameter as the BGA ball (nominal dimension) shown on the component datasheet.

### **Planning Is Key**

BGAs of any size require a lot of room around them for all the wires and vias you will need to effectively make all the desired connections. Different board patterns will need optimal fan-outs or escape routing tailored to fit them. Examine each pattern carefully, scrutinizing spacing between solder balls, confirming whether they are parallel and equidistant or have greater spacing in one direction, and establishing minimum trace width and spacing (Figure 1).

Make sure that the critical signal paths and decoupling capacitors are well situated to maintain signal integrity and reduce inductance. Starting with the via escapes and fanouts, keep some tried and true tricks in mind, such as high aspect ratio vias, micro-vias, or buried vias that will allow you to utilize real estate on all layers. These can be especially critical in the very large and fine pitch devices. Traces required to route between these pads and vias also can be reduced to provide an escape. You may need to use traces and spaces considerably smaller than the rest of the board in this case. Adding signal layers is another trick to effective routing. Typically, one signal layer is needed for every two rows of pins, but if the BGA pitch is below 0.8 mm, you will need one signal layer per row. Keep in mind that increasing layers can be a relatively simple way to route the traces, but it can also increase the cost of the board and open the door for reliability issues. In many cases, it's probably worth evaluating whether a change to your layout can reduce the layer requirements.

### Pro Tip

Make sure that you are working with a PCB manufacturer up front and understand their capabilities, especially as it relates to these aspects for the BGA routing. It is never fun to spend a lot of time on a design and then find out your preferred vendor simply cannot manufacture it.

### **Use Your Design Tool**

Many of the design tools today have functions to help make you more successful in your design efforts. Explore some of these functions and use them when they make the most sense for your design. Often, you can assign specific rules around your BGA that may differ from the rest of the board, saving you the time and effort of doing it on a trace by trace basis.

Good luck! Remember these best practices, and you too can make friends with the mysterious BGA. **DESIGN007**

**Bob Tise** is an engineer at Sunstone Circuits, and **Matt Stevenson** is the VP of sales and marketing at Sunstone Circuits. To read past columns or contact Tise and Stevenson, click here.

Bob Tise

Matt Stevenson

# Need help finding the right people for your team?

DB Management knows that finding the right people can be like looking for a needle in a haystack. We can streamline your hiring process with pre-qualified candidates.

Engineering · Management · Sales & Marketing

### Click here to get started

🔇 207-649-0879 🖾 danbbeaulieu@aol.com

### IEEE's Heterogeneous Integration Roadmap, Part 2

#### Feature Interview by the I-Connect007 Editorial Team

In Part 1 of this conversation from *SMT007 Magazine*, Rita Horner of Synopsys provided a general overview of the IEEE Heterogeneous Integration Roadmap (HIR)—a document that provides guidance for IC, PCB, and package designers, broken down by industry segment and performance requirements. In Part 2, Rita shares her perspective from the IC side, as well as how the HIR might affect what happens on the PCB design and manufacturing side in the next few years.

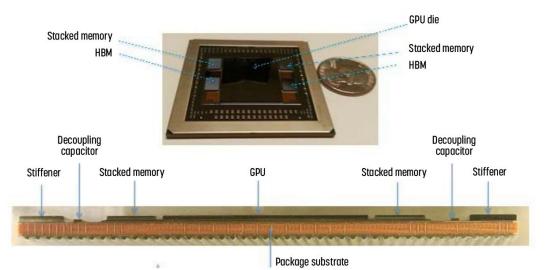

**Nolan Johnson:** You're working at Synopsys on multi-chip integration in a package EDA product. Compare and contrast the difference between multi-chip products today and where the HIR will take us. How is it different?

**Rita Horner:** As you mentioned, the HIR covers many grounds, and it's not just one market or application space. It's hard to just generalize that. I talked about technology limitations, but there is an economic aspect of it because

it's not cheap to make these devices. Even a monolithic die in a package is expensive when it's complex and large in the advanced technology nodes today, such as five nanometers or smaller. When you're not getting the yield, it's going to make it even more expensive. Very few people can afford to design in the advanced technology nodes. Heterogeneous integration in a package would enable an entry path to the high-end markets much more easily. They don't have to design everything in the most expensive technology nodes to achieve high levels of integration.

**Johnson:** Just because a small function of the design needs high density doesn't mean the entire design has to be that way.

**Horner:** Five-nanometer technologies may not be optimal for the high performance I/Os that may be needed. With the thinner oxide layers in the smaller technology nodes, the threshold voltages are lower and more challenging to design high speed I/Os. These are the physical layers. High-speed SerDes may be more optimal in older technology nodes, whereas the rest of

SUBSCRIBE

## Subscribe to the Polarinstruments YouTube channel for helpful impedance and stackup videos

#### PCB Signal integrity tools for design & fabrication

- Impedance & insertion loss modeling with Si9000e

- PCB stackup design & documentation

- Test systems for controlled impedance & insertion loss

- · Application notes on a wide range of Si topics

#### polarinstruments.com

the computing may be better off in a smaller technology node that would offer higher densities.

By doing heterogeneous integration, you can mix and match devices from different technologies and maybe allow devices to be implemented in their more optimal process nodes, instead of having to be in the same single die. It gives a lot more flexibility for optimization. Even filtering devices can be integrated within

**Rita Horner**

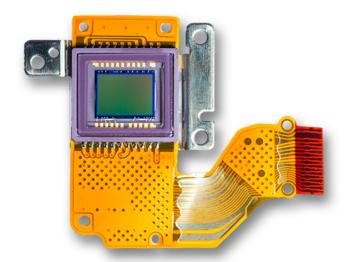

the package for smaller form factors. The package is becoming a miniature PCB.

**Johnson:** Is that where things get different with the HIR compared to traditional multichip modules? It seems there is a much greater demand on the interconnect part of the technology.

**Horner:** HIR has bucketed multiple market spaces. They have 5G, computing, and high performance, and they're identifying every one of these, like automotive, aerospace, and different market needs. The PCB traces that used to be 100-micron trace and spaces are shrinking further. On the multilayer PCB, the traces and spaces are about eight microns today.

**Happy Holden:** Eight microns was the leading edge of people I worked with in Asia, and it's

relatively high volume. They'll make 60–100 million of these 50-millimeter by 50-millimeter interposers on an 18- by 24-inch panel. It's very advanced printed circuit technology.

**Horner:** That's almost the same as the cutting edge in package traces. Packaged substrates used to be 10-micron spaces and width, and the cutting edge is about eight microns right now. The silicon is

smaller than one micron. The silicon interposers that are available in the market right now, there is less than one micron, width, and space traces. They tend to be much older technology silicon material. The smaller the width and spacing for die-to-die connection, the more optimal widths and spaces. But it's good and optimal for lots of trace connections, like two or four gigabit-per-second types of frequency.

But once you start going to higher data rates, you cannot maintain using silicon interposers. That's why people are moving more toward the organics, which have a lower loss, but then you're talking about much wider width and spacing traces. Effectively, people are approaching things both on the silicon side and on the packaging side, and trying to address die-to-die connection.

**Johnson:** Looking into the HIR, I see reference to the organic interposer.

All future applications will be further transformed through the power of AI, VR, and AR.

Figure 1: Six application spaces undergirded by AI, VR and AR. (Source: ASE)

| Materials           | Application                                  | Features (µm)         | 2018    | 2019    | 2020    | 2021    | 2022    | 2025    | 2028    | 2031    | 2034    |

|---------------------|----------------------------------------------|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Organic<br>laminate | FC-BGA                                       | Min. Bump Pitch       | 110     | 100     | 100     | 90      | 90      | 80      | 80      | 70      | 70      |

|                     |                                              | Min. Line width/space | 9/12    | 9/12    | 9/12    | 8/8     | 8/8     | 5/5     | 5/5     | 5/5     | 5/5     |

|                     |                                              | Min. µVia diameter    | 50      | 50      | 50      | 40      | 40      | 30      | 30      | 20      | 20      |

|                     | Chiplet (Fan-<br>out, Organic<br>interposer) | Min. Bump Pitch       | 50      | 50      | 50      | 45      | 45      | 40      | 40      | 30      | 30      |

|                     |                                              | Min. Line width/space | 2/2     | 2/2     | 2/2     | 1.5/1.5 | 1.5/1.5 | 1/1     | 1/1     | 0.5/0.5 | 0.5/0.5 |

|                     |                                              | Min. µVia diameter    | 30      | 30      | 30      | 20      | 20      | 10      | 10      | 5       | 5       |

| Silicon             | Chiplet<br>(Si Interposer,<br>3D)            | Min. Bump Pitch       | 40      | 40      | 40      | 35      | 35      | 30      | 30      | 20      | 20      |

|                     |                                              | Min. Line width/space | 0.6/0.6 | 0.6/0.6 | 0.6/0.6 | 0.6/0.6 | 0.6/0.6 | 0.5/0.5 | 0.4/0.4 | 0.3/0.3 | 0.2/0.2 |

|                     |                                              | Min. µVia diameter    | 0.6     | 0.6     | 0.6     | 0.6     | 0.6     | 0.5     | 0.4     | 0.3     | 0.2     |

Table 1: Substrate interconnect scale roadmap (micrometers). (Source: HIR, 2019)

**Horner:** These are the RDL layers that I was describing around two microns. The package substrate material is also referenced as organic, but that is different than an interposer organic, which tends to be referenced to more of an RDL layer that is used for die to die connection.

**Johnson:** We're now talking about having a semiconductor package that has multiple chips of different capabilities, plus an interconnect using different kinds of interposers. The interposer design is essentially a PCB that goes in the middle of the package. Is this interposer considered an IC design item, or is this a PCB design that then ends up inside the chip?

**Horner:** There are different materials used for the interposer. The most used interposer today is the silicon interposer. There's also glass that was mentioned earlier. Historically, a package did not have to deal with a lot of the complexities needed in today's multi-die integration. That's why a lot of these tools that were typically used for package substrate design are running out of bandwidth and capabilities for complex multi-die designs. Using EDA tools optimized for complex SoC design is more optimal in addressing silicon interposer design needs. Some vendors are trying to approach it from the package side, and they get a lot of complaints from customers and the people that we're interfacing with, saying, "They're out of juice. They don't have the bandwidth."

How do you do the modeling for your signal integrity analysis? How do you do your modeling in terms of power integrity analysis? How do you bring the information together from different technologies? Even the silicon EDA tools are not capable of doing that because, usually, when you design one IC, you deal with one technology at a time. It's 14 nanometers. You need a more enhanced tool environment that allows you to integrate multiple technologies now to be able to model them, analyze them, do analysis, and validate them in the multi-die environment.

**Johnson:** This inserts a different domain of knowledge into the IC design team's area of responsibility.

**Horner:** That's why I was mentioning the need for a collaborative environment. It's not just IC design's problem. It's not only the packaging design person's problem or a signal integrity problem. All disciplines have to work together to make this problem be more optimally addressed.

**Johnson:** Is this where PCB design experience becomes valuable to the IC team? Is this a place where you'd want to start bringing in

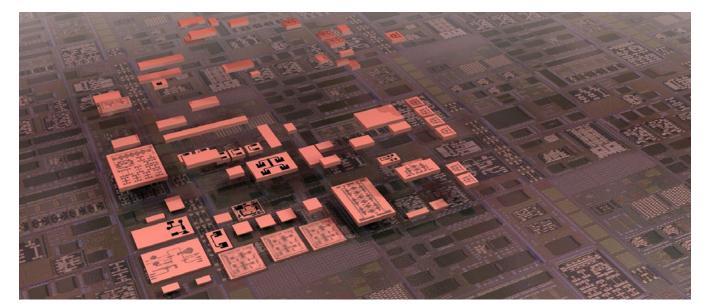

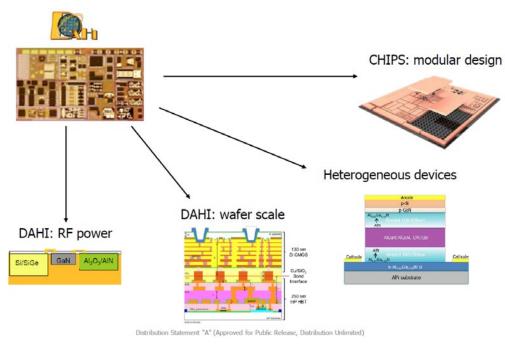

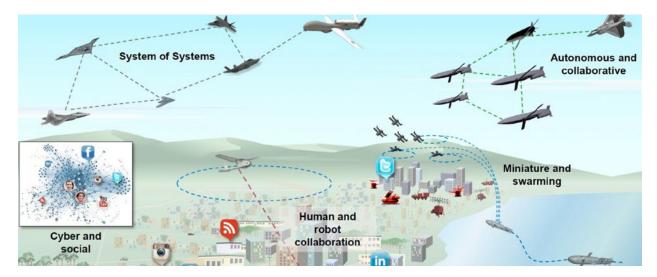

Figure 2: Heterogeneous integration. (Source DARPA)

somebody with board experience to work on the interconnect inside the chip?