## SEPTEMBER 2018 DESIGNOUT MAGAZINE

# Get heat relief with low-temperature soldering!

1

#### Low-Temperature Soldering

Morgana Ribas, et al. Alpha Assembly Solutions

**Download Now!**

I-007eBooks.com

## Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

#### View our eBook library

#### SEPTEMBER 2018 • FEATURED CONTENT

# DESIGNOOT

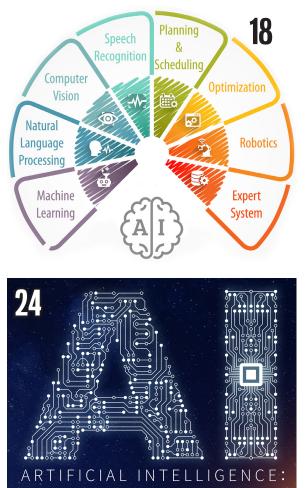

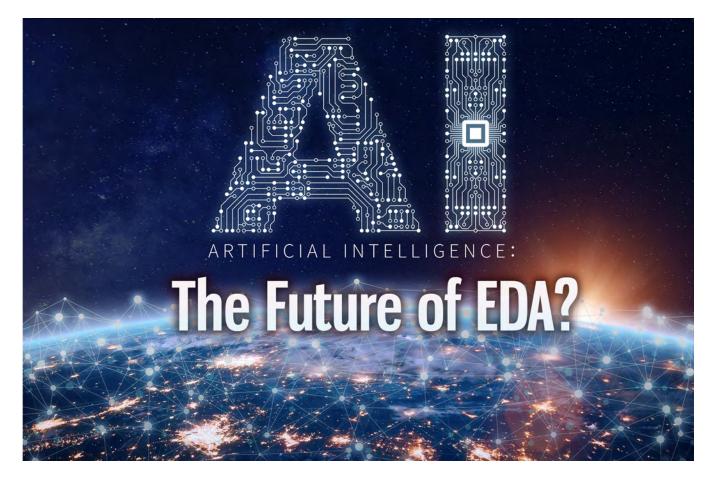

## **Artificial Intelligence**

Artificial intelligence has been grabbing headlines over the past few years. It's one of the hotter segments to watch, especially with drones, robots, autonomous vehicles and virtual reality applications becoming more popular every day. What does AI mean for PCB designers and their EDA tools? This month, we asked our expert contributors to discuss AI and what it might mean to PCB design and the rest of the electronics industry.

- 12 Artificial Intelligence: More Questions than Answers by Dan Feinberg

- 18 Cadence: Bullish on Al Interview with David White

24 Artificial Intelligence: The Future of EDA? Interview with Paul Musto, Mentor, A Siemens Business

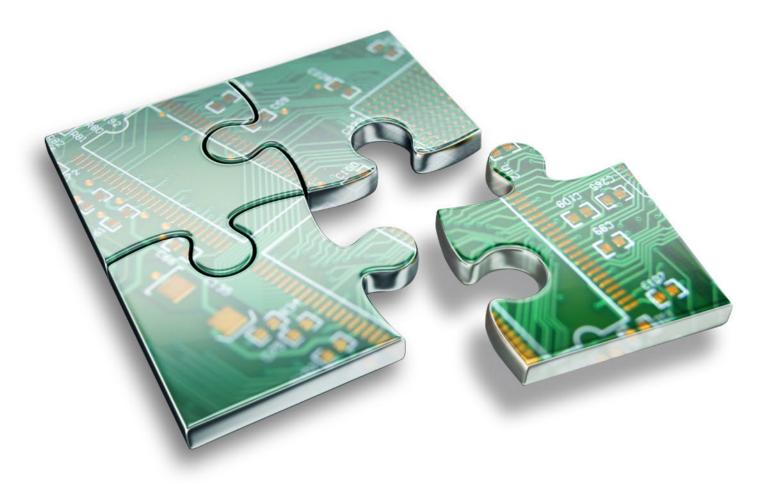

## **Contract Manufacturers:** Need the perfect fit? ASC is the missing piece.

Finding a reliable PCB supplier can be difficult for contract manufacturers with a wide variety of project needs. ASC has the technology, experience and engineering support needed to deliver on-time solutions for everything from quick-turn prototypes to the most demanding, complex applications.

#### More about our capabilities

## American Standard Circuits Creative Innovations In Flex, Digital & Microwave Circuits

www.asc-i.com | (630) 639-5444

#### SEPTEMBER 2018 • ADDITIONAL CONTENT

# DESIGNOOT

SHORTS:

- 10 Enabling 'Internet of Photonic Things' With Miniature Sensors

- 58 Bismuth Shows Novel Conducting Properties

- 64 Diamond Dust Enables Low-Cost, High-Efficiency Magnetic Field Detection

#### HIGHLIGHTS:

- 46 MilAero007

- 74 Top 10 PCBDesign007

#### **DEPARTMENTS:**

- 76 Career Opportunities

- 84 Events Calendar

- 85 Advertiser Index & Masthead

#### **ARTICLES:**

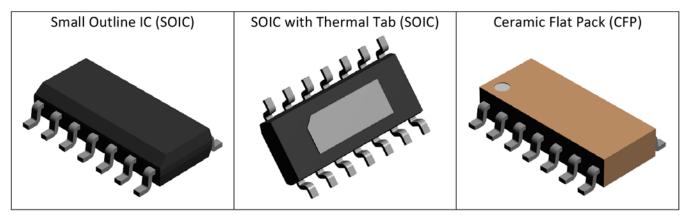

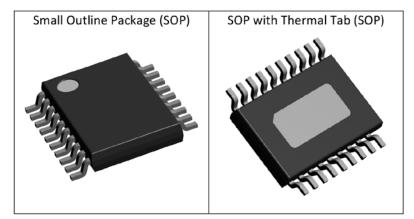

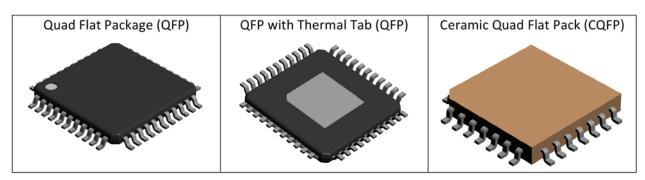

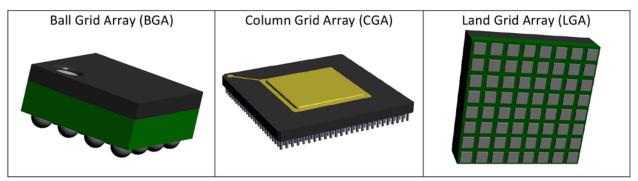

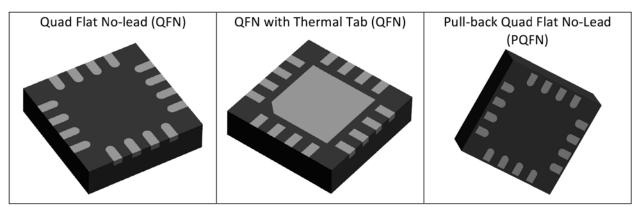

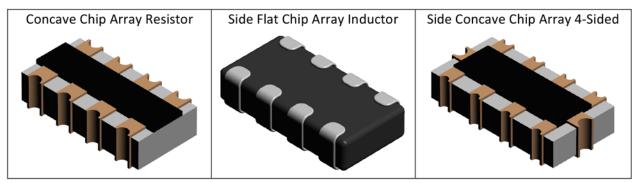

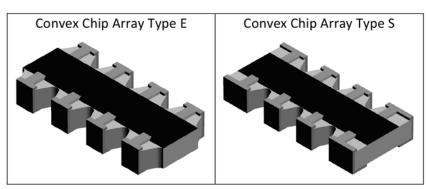

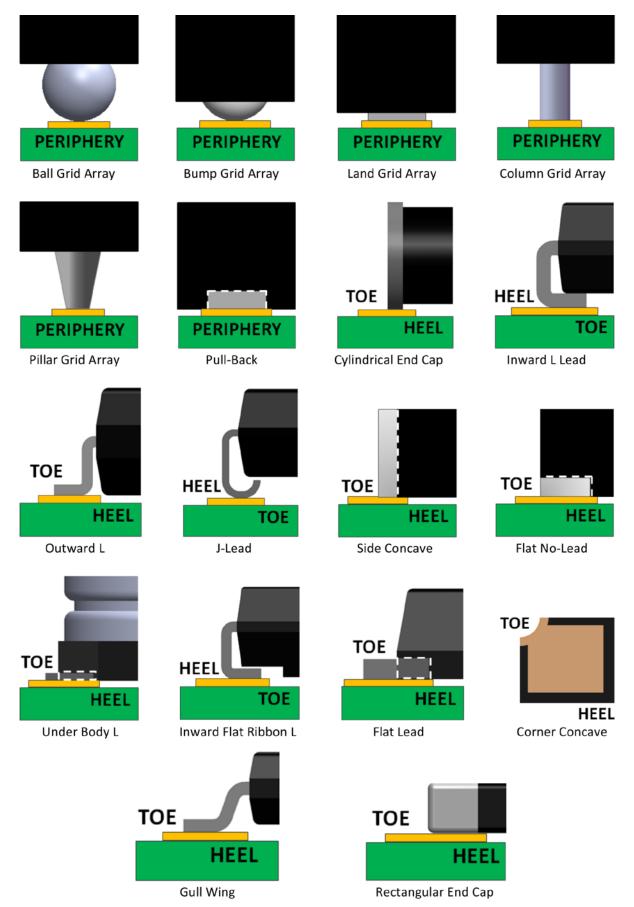

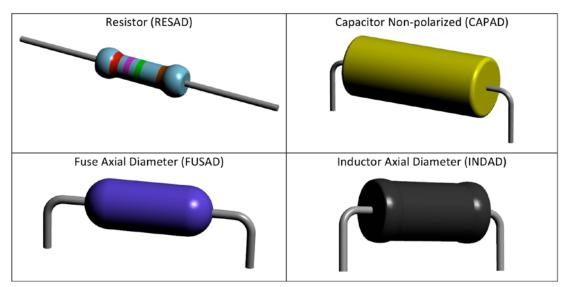

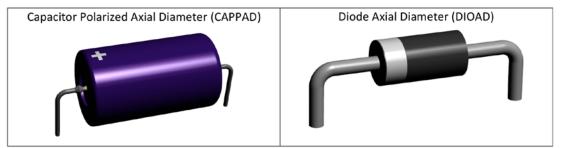

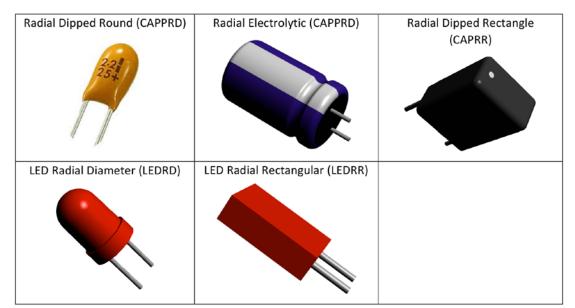

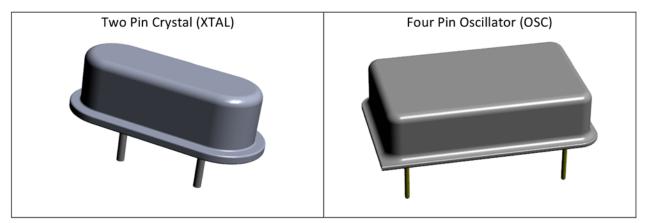

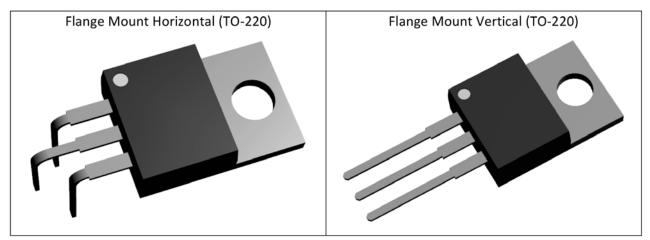

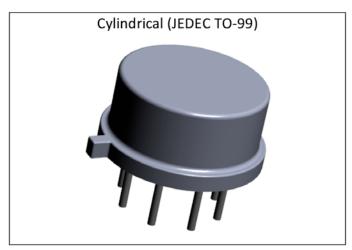

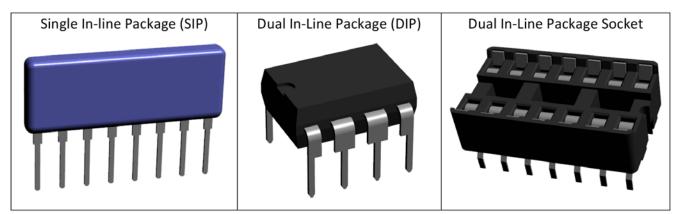

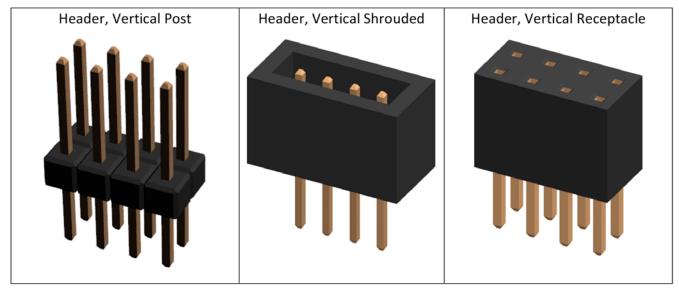

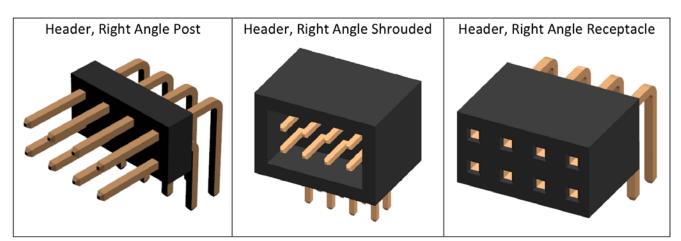

48 Standard PCB Component Families, Part 2 by Tom Hausherr

- 60 Achieving Minimal Crosstalk in Multi-Board Interconnect by Chang Fei Yee

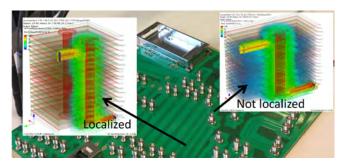

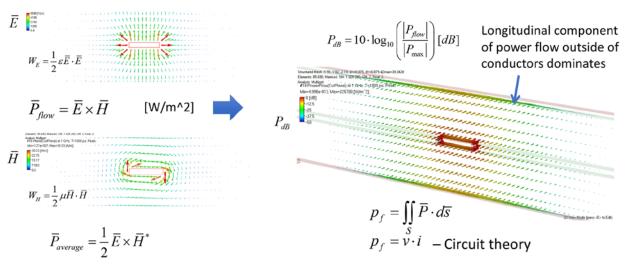

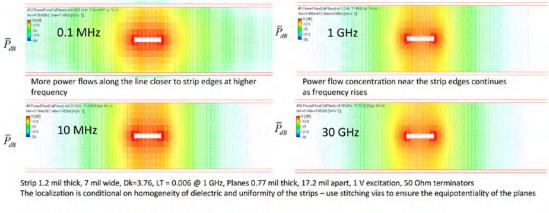

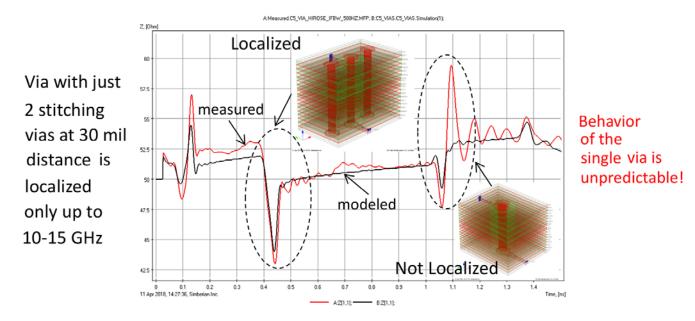

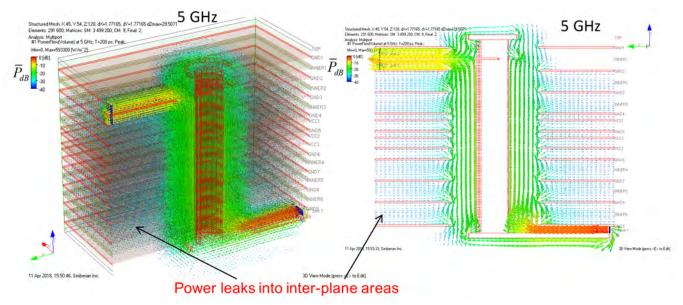

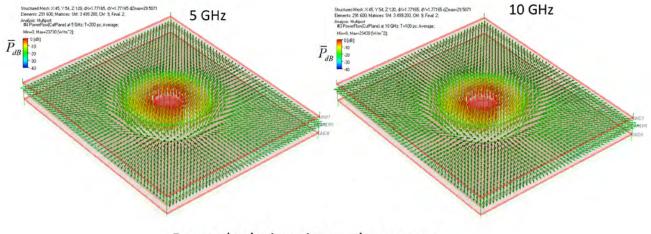

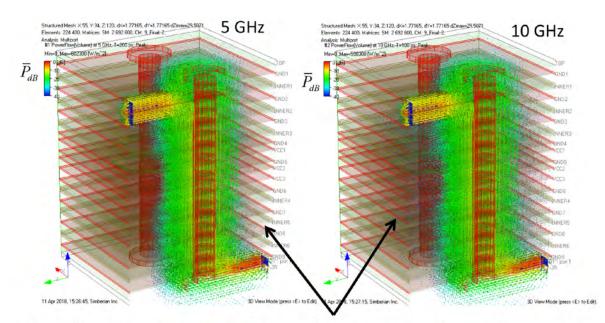

- 66 Life Beyond 10 Gbps: Localize or Fail! by Yuriy Shlepnev

#### **COLUMNS:**

8 Al at the Crossroads by Andy Shaughnessy

- 30 10 Fundamental Rules of High-Speed PCB Design, Part 1 by Barry Olney

- 36 Embedding Components, Part 3: Implementing Discrete Passive Devices by Vern Solberg

- 42 Contract Positions: Go the Extra Mile by Tim Haag

The Automotive industry is held to the highest standards by consumers and the highly competitive market alike; both of which expect constant innovation in safety and performance.

ENGINE START TOP

In todays' world innovation mostly comes through the advancement of electronic systems, which are critical to the smooth and safe operation of any vehicle. From interior switches and under-the-hood controls right through to exterior lighting and sensor systems, we develop innovative solutions that enhance performance, providing the 'complete solution' at all levels.

We work to the qualified standards of the world's most renowned automotive manufacturers, providing electrochemical solutions that not just meet, but constantly exceed expected standards.

The combination of our 70+ years' experience in producing performance enhancing electrochemical solutions, together with our high standards of customer service and global reach really begs the question ...

Isn't it time you discovered how Electrolube can serve you?

Tel: 888-501-9203

#### www.electrolube.com

Electronic & General Purpose Cleaning

Conformal Coatings

Encapsulation Resins

Contact

Maintenance & Service Aids

**ELECTROLUBE**

THE SOLUTIONS PEOPLE

Hullindu

Scan the code to discover our full spectrum of electro-chemical solutions.

#### electronica Electronica Germany Hall A2, Stand 437 13 - 16 November 2018 Hall B4, Stand 315 Munich, Germany

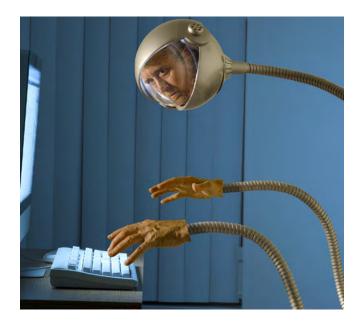

## Al at the Crossroads

#### The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

(Source: WikiCommons)

I don't know about you, but every time I hear the term artificial intelligence, it still reminds me of HAL 9000, the computer that took over the Discovery One spaceship in 2001: A Space Odyssey.

I always secretly rooted for HAL. I perfected my impression of HAL's voice when I was young. I'd walk around the house telling my little sisters, "I'm sorry, Dave. I'm afraid I can't do that."

AI has been grabbing the headlines for the past few years. It's one of the hotter segments to watch, especially

with drones, robots, autonomous vehicles and virtual reality applications becoming more popular every day. AI isn't just popular, it's fun.

And AI can be a lucrative area for investors. Companies that were unknowns not long ago such as NVIDIA, Twilio, Alphabet and Baidu are riding the AI train all the way to the bank. Baidu is the top AI company in China, and the firm stands to benefit from that country's drive to be the global leader in AI by 2030.

AI and its cousin, machine learning, are slowly making their way into EDA tools, most often to increase the speed of an existing process, or to reduce simulation times. All of the big EDA companies are involved in AI research, and we can expect to see more AI-driven functionality in the future. But some AI experts believe that the current crop of EDA tools can never take full advantage of AI, because most of these tools are based on code written many years ago, and true AI-driven EDA tools would have to be developed from the ground up. I doubt any EDA company is looking forward to the prospect of creating a whole new platform of PCB or IC design tools from scratch.

AI's development has continued despite a fear among Luddites that intelligent computers could eventually enslave or kill us all. Movies like 2001 and "The Ultimate Computer" episode of the original Star Trek helped scare people into worrying about what could happen if AI ever ran amok. That could never happen, right?

Some people think it's already happening. Your Alexa could be considered one of the benevolent bots, but bots have also hacked

## Solutions to Ensure PCB Manufacturing Success!

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

For more information please visit downstreamtech.com or call 800-535-3226.

into the IRS and manipulated world finance markets. We've also seen the effect that bots can have on social media platforms like Facebook and Twitter, automating posts, manipulating the ranking algorithms, and (potentially) affecting a presidential election. It's all relative: If the bots are helping your organization, they're helpful tools, not a reason to distrust everything you see on social media.

The Neural Information Processing Systems Foundation (NIPS) understands the benefits and dangers of AI, offering workshops with titles like Machine Deception and Security in Machine Learning, as well as AI for Social Good. There are pros and cons to every new technology, and we've barely begun to see the potential for AI.

This month, we asked our expert contributors to discuss AI and what it might mean to PCB design and the rest of the electronics industry. Technical Editor Dan Feinberg has been reporting on AI for years, and he offers a look at where AI is now in terms of consumer products, and some of the hurdles that AI faces in the upcoming years. David White of Cadence Design Systems has been involved with AI since his college days, and he shares his thoughts on Cadence's work with AI and what it could mean to EDA tools. And Mentor's Paul Musto explains how the company plans to harness the power of AI, and why oldschool PCB designers shouldn't feel threatened by AI-driven EDA tools.

We have Part 2 of Tom Hausherr's collection of standard PCB components, and an article by Chang Fee Yee of Keysight Technologies on reducing crosstalk in multi-board interconnect. And Simberian's Yuriy Shlepnev brings us an article on localizing interconnect structures at speeds above 10 Gbps. We also have columns from our regular contributors Barry Olney of iCD, consultant Vern Solberg, and consultant Tim Haag.

It's a great time to be in this industry. Show season is upon us, and I hope to see you at SMTA International in October. In the meantime, if you're not already a subscriber, click here. While you're at it, subscribe to our newsletters, too.

See you next month. DESIGN007

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 18 years. He can be reached by clicking here.

#### **Enabling 'Internet of Photonic Things' With Miniature Sensors**

A team of researchers at Washington University in St. Louis is the first to successfully record environmental data using a wireless photonic sensor resonator with a whispering-gallery-mode (WGM) architecture.

In the grand world of the Internet of Things (IoT), there are vast numbers of spatially distributed wireless sensors predominately based on electronics. These devices often are hampered by electromagnetic interference, such

as disturbed audio or visual signals caused by a lowflying airplane and a kitchen grinder causing unwanted noise on a radio.

But optical sensors are "immune to electromagnetic interference and can provide a significant advantage in harsh environments," said Lan Yang, the Edwin H. & Florence G. Skinner Professor of Electrical & Systems Engineering.

Yang's sensor belongs to a category called whispering gallery mode resonators, so named because they work like the famous whispering gallery in St. Paul's Cathedral in London.

Yang and her colleagues had to address stability issues, which were handled by the customized operation systems app they developed, and miniaturization of bulky laboratory measurement systems.

"We developed a smartphone app to control the sensing system over WiFi," Yang said. "By connecting the sensor system to the internet, we can realize real-time remote control of the system."

(Source: Washington University in St. Louis)

## **Engineering And Providing Balanced Interconnect Solutions**

nechanical environmental

electrical cost

Miraco, Inc. Manchester, NH miracoinc.com 603-665-9449

...connecting technology

SOLUTION

## **Artificial Intelligence:** More Questions than Answers

#### Feature by Dan Feinberg I-CONNECTO07

I've been covering artificial intelligence (AI) and related technologies for years, particularly at events such as the annual Consumer Electronics Show (CES). As I write this, we are in the run-up to CES 2019 and the Artificial Intelligence Conference in San Francisco, so the AI landscape is likely to change—at an ever-accelerating rate. Let's look at some of the challenges facing AI now, and then after CES 2019 we can take another look.

As the title suggests, in this quickly changing segment of the electronics industry, there may be more questions than answers. Fittingly, I think it's best for us to start with one great question about artificial intelligence, and we'll go on from there. **Q.** What is artificial intelligence (AI), and are machines capable of being intelligent?

**A.** The *English Oxford Living Dictionary* defines AI this way: "The theory and development of computer systems able to perform tasks that normally require human intelligence, such as visual perception, speech recognition, decision-making, and translation between languages."

Or how about simply, AI is something that hasn't been done yet without human intervention. Some technologies that were considered AI just a few years ago such as conversational speed language translation and optical character recognition are no longer considered AI.

It is obvious that we have entered the era of common use of AI. Autonomous transportation is now a case of when, not if, thanks

### **Everything's** about to change

Join us at AltiumLive for the dawn of a new era in electronics design and realization.

#### San Diego, California October 3-5 2018

Register today to secure your spot at the "most anticipated electronics design conference in the world": altium.com/live-conference/san-diego

Figure 1: An Al server farm.

Figure 2: Games such as "Call of Duty" have helped make AI a mainstream technology.

to groundbreaking companies like NVIDIA. Virtual personal assistants such as Cortana, Alexa, Hey Google and Siri are now part of our everyday lives. Today's military training simulators and popular first-person shooting games such as "Far Cry" and "Call of Duty" make significant use of AI by utilizing artificial enemies that can analyze the user's environments and actions, as well as find objects and calculate actions that might be beneficial to the user's survival and victory.

Drones and robots have made plenty of headlines lately. Contract manufacturers in Asia boast of their plans to replace workers with

robots capable of doing extremely technical assembly work. Drone hardware has also improved quite a bit in the past few years alone, and the cost of a drone has dropped dramatically. Once just expensive playthings, today's drones often feature an HD camera and sell for a few hundred dollars. As their AI improves, we will see more and more drones and robots.

As AI and machine learning continues to improve, there will be more communications and more humansounding conversations between us and our digital assistants like Cortana, Alexa and Google Home. At CES, I expect to see a horde of new assistants that have learned to speak naturally. I also expect to see significant progress from as-yet unknown companies. After all, none of us are really that happy with the digital assistants that are available today, and most of us are concerned that we are inadvertently providing way too much information to the likes of Google or Facebook.

Because of AI, we now have fraud detection that happens faster than the blink of an eye, and purchase prediction such as Amazon's predicted anticipatory shipping project. This handy feature plans to send you items before you think you need them. The point is that AI is part of our lives and it is not as new as the

Figure 3: Fraud detection has come a long way, thanks in part to AI.

Since we first began in 1985, delivering the highest quality products possible has been our first priority. Our quality control systems are certified and we renew our commitment to quality each and every day.

Delivering quality products on time, combined with timely and accurate communication from our customer service team is how we create lasting relationships with our customers.

#### Take a look at our quality »

#### **COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

average person might believe.

Overall, we can expect very significant advances in AI over the next few years. I would guess that there will not be a segment of modern civilization that will not see advances beyond what was envisioned at the turn of the century. AI will change things for sure, but will all these changes be for the good? We will have to wait and see.

Figure 5: In the future, will the human brain be integrated with AI functionality?  $^{10}$

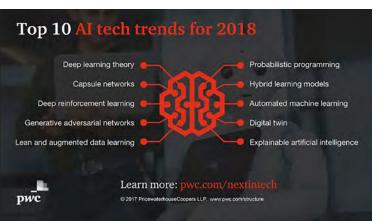

Price Waterhouse Cooper has

been following the top trends in AI in 2018 <sup>[1]</sup>, as shown in Figure 4.

Of all the trends shown in Figure 4, the most influential ones in the short term (and there are others) are what really get my attention as I study this topic: deep learning theory, probabilistic programming, and automated machine learning. If you want more examples and far more detail, see Reference 1.

In the meantime, I believe a prediction from my hero Nikola Tesla, in 1926, can help us to imagine what might be possible with AI. Remember, in 1926 global communication was possibly only by radio code, telegraph and basic one-way (at a time) radio with operatorassisted telephone. Primitive TV had recently been demonstrated. But Tesla knew this was the beginning of better things to come:

When wireless is perfectly applied, the whole earth will be converted into a huge brain, which

Figure 4: The top trends in artificial intelligence in 2018.

in fact it is, all things being particles of a real and rhythmic whole. We shall be able to communicate with one another instantly, irrespective of distance. Not only this, but through television and telephony we shall see and hear one another as perfectly as though we were face to face, despite intervening distances of thousands of miles; and the instruments through which we shall be able to do this will be amazingly simple compared with our present telephone. A man will be able to carry one in his vest pocket. —Nikola Tesla

The topic of artificial intelligence itself is immensely broad and the possibilities are vast. I expect CES 2019 will truly begin to show the integration of AI into the other disruptive technologies and the effect that will have on the devices our industry will be required to produce in the decade ahead. We'll touch base again after CES. **DESIGN007**

#### References

1. Price Waterhouse Cooper's Top 10 Artificial Intelligence Technology Trends for 2018.

**Dan Feinberg** is the owner and president of FeinLine Associates Inc. and the technology editor for I-Connect007. To read his past columns or to contact Feinberg, click here.

## **5G: Higher Frequencies!** Do you have the **right** circuit materials?

Frequencies at 28 GHz and higher will soon be used in Fifth Generation (5G) wireless communications networks. 5G infrastructure will depend on low-loss circuit materials engineered for high frequencies, materials such as RO4835T<sup>™</sup> laminates and RO4450T<sup>™</sup> bonding materials from Rogers Corporation!

Rogers RO4835T spread-glass-reinforced, ceramic-filled laminates are low-loss materials in 2.5, 3.0, and 4.0 mil thicknesses. They are well suited for millimeter-wave frequencies as part of the inner cores of 5G hybrid multilayer PCBs. They can work with other materials to provide the many functions needed by 5G wireless base stations, including power, signal control and signal transfers.

Н

Vehicle to

Rogers RO4450T bonding materials are available in 3, 4, and 5 mil thicknesses to help construct those 5G hybrid multilayer circuits. These spread-glass-reinforced, ceramic-filled bonding materials complement the different materials that will form these hybrid circuits, including RO4835T and RO4000° laminates. And for many 5G hybrid multilayer circuits, Rogers CU4000<sup>™</sup> and CU4000 LoPro° foils will provide a suitable finishing touch for many hybrid multilayer circuit foil lamination designs.

#### 5G is coming! Do you have the right circuit materials?

Learn more at www.rogerscorp.com/5G

Advanced Connectivity Solutions

\* IPC TM-650 2.5.5.5 Clamped Stripline at 10 GHz - 23°C

USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611 www.rogerscorp.com

| Product         | *Dk  | *Df    |  |

|-----------------|------|--------|--|

| RO4835T 2.5 Mil | 3.33 | 0.0030 |  |

| RO4835T 3.0 Mil | 3.33 | 0.0034 |  |

| RO4835T 4.0 Mil | 3.32 | 0.0036 |  |

| RO4450T 3.0 Mil | 3.23 | 0.0039 |  |

| RO4450T 4.0 Mil | 3.35 | 0.0040 |  |

| RO4450T 5.0 Mil | 3.28 | 0.0038 |  |

|                 |      |        |  |

lehicle to

mart Gri

Vehicle to Pedestriar

## **Cadence:** Bullish on Al

#### Feature Interview by Andy Shaughnessy I-CONNECT007

David White has been involved with artificial intelligence research for almost 30 years. Now, David is the senior group director of R&D for Cadence Design Systems, and I knew we'd have to speak with him for this month's issue on AI. In a recent interview, we discussed his decades of work in AI, Cadence's research into AI and machine learning, and what he believes AI could mean for the EDA tools of the future.

**Andy Shaughnessy:** Tell us a little about your background, your work with AI, and your thoughts on AI overall.

**David White:** I started working in AI in 1989 as a college student after discovering a copy of Parallel Distributed Processing, by David Rumelhart. I was so enthralled that I completed my undergraduate thesis on using neural networkbased controls for a robotic arm. That work led me to McDonnell Douglas, now Boeing, where I worked in the New Aircraft

a book on intelligent decision and control systems in 1992 with leaders in the machine learning world such as Michael Jordon, Paul Werbos and Andy Barto. I completed my graduate work at MIT where my research applied machine learning and chemometrics to semiconductor processing. I later co-founded and served as CTO of Praesagus, a company that was acquired by Cadence in 2006, and I have been working on electronic design automation with Virtuoso technology since 2009.

I joined the MIT AI Laboratory where I con-

tinued my research and edited and co-authored

In terms of my thoughts on AI, I am really excited about the prospects of building intelligent decision systems that can learn from users and their environment. We believe we are bringing a unique perspective to how we build these systems. We are combining innovations in machine and deep learning with large scale optimization and distributed processing in unique ways. Much of what we are working on has applications beyond EDA and extends to how we can build design and analysis soft-

ware that tailors itself to the user and their mission.

Products Division on machine learning research for manufacturing and flight controls. As a result of this work, NSF asked me to chair the first NSF Workshop on Aerospace Applications of Neural Networks, which included machine learning researchers from across the country as well as a presidential science advisor and government officials.

Planning Speech & Recognition Scheduling Computer Optimization Vision Natural Language Robotics Processing Machine Expert Learning System

**Shaughnessy:** How did Cadence first get involved with AI?

> White: I joined Cadence in 2006 when our company was acquired, so my frame of reference begins then. Cadence's research in machine learning (ML) for physical design and electrical analysis started in the

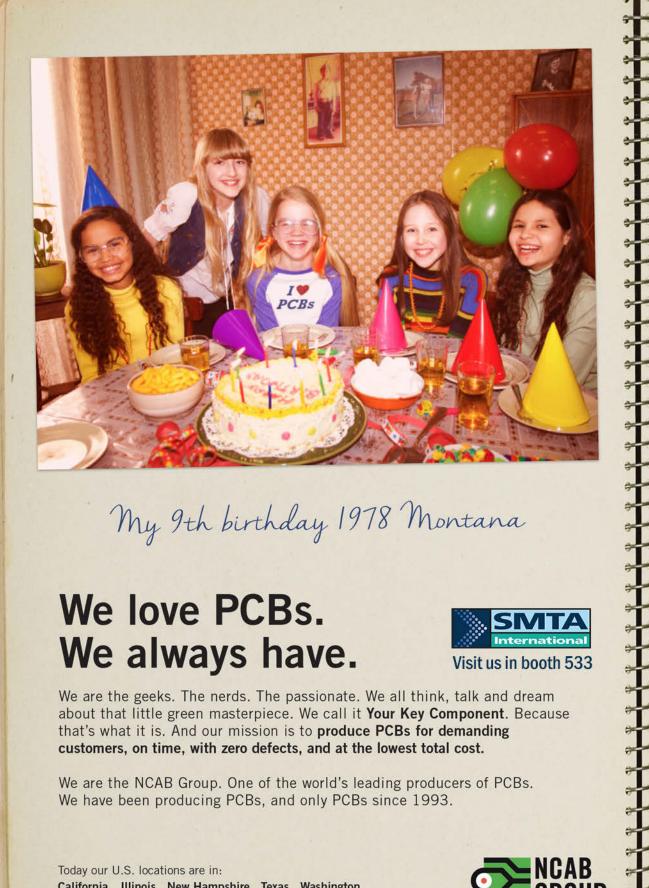

#### ME, 1979. JUST FOUND MEANING OF LIFE.

## We love PCBs. We always have.

We are the geeks. The nerds. The passionate. We all think, talk and dream about that little green masterpiece. We call it **Your Key Component**. Because that's what it is. And our mission is to **produce PCBs for demanding customers, on time, with zero defects, and at the lowest total cost.**

We are the NCAB Group. One of the world's leading producers of PCBs. We have been producing PCBs, and only PCBs since 1993.

Today our U.S. locations are in: California Illinois New Hampshire Texas Washington

www.ncabgroup.com

2009-2010 timeframe, with two persons and myself. Our motivation came from observing the scale and complexity that grew with the increase in data such as larger designs, larger simulations, etc.

To address these problems, we began to look at data-driven solutions such as analytics and machine learning. When we began the work, there was not the same buzz around machine or deep learning, and we just found it to be a useful tool to create fast models of complex non-linear problems that required long compute times using more traditional methods. Two machine learning-based solutions were released in 2013 in the Virtuoso Electrically Aware Design (EAD) environment and Virtuoso Analog Design Environment (ADE).

**Shaughnessy:** Tell us about Cadence's current research into AI. Are you continuously working to implement more AI in EDA tools?

**White:** As you can understand, I can't go into details on research and development that has not been released in our products.

First, we are fortunate to have a brilliant team of engineers who continually push the edge. Our machine learning team includes members of our Virtuoso technology team, which focuses on placement, routing, and analog design and electrically aware design as well as our OrbitIO package and board solution—so they have hands-on experience with the applications we are trying to automate.

We are constantly evaluating data-driven solutions such as machine and deep learning, as well as analytics, optimization and distributed processing. You always hear about machine and deep learning, but those other solutions are often required as well. Optimization is often overlooked in discussions about building intelligent, adaptive systems. From a decision systems perspective, you want to use optimization in conjunction with ML/DL to drive the system or decision sequence to some desired state (e.g., a placement and routing alternative that meets design intent). One solution is no more important than the other.

The biggest challenge in productizing AI is addressing the verification, deployment and support issues that every new technology faces. Most of the available open source software focuses on the creation of ML or DL models and not as much on how to verify, calibrate or adapt those models in environments that change. However, those factors are critical in CAD/EDA tools where design intent may not be fully observable or the environment changes

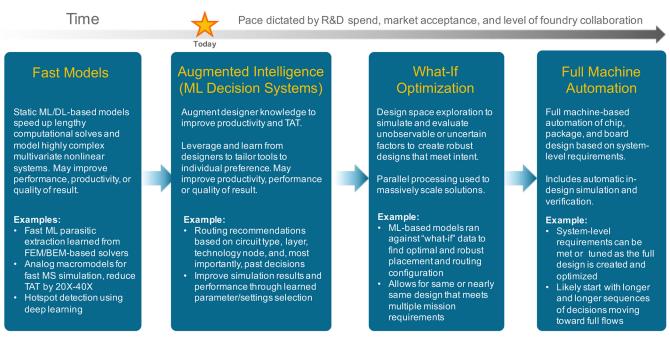

Figure 1: A graphic showing the development of machine learning and EDA over the years.

My 9th birthday 1978 Montana

## We love PCBs. We always have.

We are the geeks. The nerds. The passionate. We all think, talk and dream about that little green masterpiece. We call it Your Key Component. Because that's what it is. And our mission is to produce PCBs for demanding customers, on time, with zero defects, and at the lowest total cost.

We are the NCAB Group. One of the world's leading producers of PCBs. We have been producing PCBs, and only PCBs since 1993.

Today our U.S. locations are in: California Illinois New Hampshire Texas Washington

www.ncabgroup.com

with the introduction of new silicon technologies.

**Shaughnessy:** Outside of EDA, what are some examples of AI that really impress you?

**White:** It is hard to answer that question—there are quite a few. I am impressed with the work Google has done under Jeff Dean. His understanding of the algorithms, and more importantly the implementa-

tion details, seems to put him on a different plane than many others. His presentations are mini-courses on problems you should be thinking about if you are not doing so already.

Overall, I am fascinated with how far speech processing has progressed with AI/ML technology fueling it. We played around with neural network-based speech processing for a summer when I was at MIT, and I learned what a hard problem it is ...(and I have not attempted to solve it ever since). Google, Amazon and others have overcome some challenging problems with AI technology, extending it from improved recognition to include translation as well.

I am a fan of Netflix and over the years have seen large improvements in their recommendation engine. There are some interesting talks that describe the AI and analytics-related innovations that go into their ability to personalize and tailor their recommendations, as well as how they tailor the quality of the user experience across many countries and cultures. That is a really dynamic and adaptive environment in which to work and as a user, I see improvements regularly.

**Shaughnessy:** Some PCB designers are worried that AI will put them out of a job. I've told them not to worry, but do they have a point?

**White:** Our view is that the introduction of machine and deep learning into electronic design and CAD systems in general will be an evolution not a revolution. In other words, I foresee several stages of innovation as the

David White

technology and methodology align. In the first stage, ML/ DL is used inside existing products to improve productivity, performance or quality of results, and we can see that occurring now.

In the second stage, machine and deep learning will be used to augment the knowledge of the designer and allow them to work at high levels of abstraction. They can move away from pushing shapes

and move toward thinking about system design enablement. It is difficult to capture the intent of the designers, so the challenge is building ML/DL technology that can discover user intent and tailor recommendations accordingly. Think of a design assistant that makes recommendations to speed productivity through the manual steps of a design.

In the third stage, we use large-scale optimization to drive multiple design decisions to one or more desired states (e.g., in EDA it could be design intent, QoR, or PPA) within a set of constraints (e.g., reliability and design rules). In the fourth stage, we will be able to automate sequences of decisions and eventually achieve longer sequences leading to full flows.

Automation will continue to impact electronic design as it has impacted other industries, but I don't see it happening overnight. If we can automate lower level tasks in the next few years, those same designers can spend more time at the systems level focusing on higherlevel goals and how to manage mission profiles where single solutions are used or tailored for multiple missions or uses. The lead architects of our OrbitIO solution are working on nextgeneration solutions to address these goals and have already achieved promising results.

**Shaughnessy:** Thanks for your time, David. We appreciate it.

White: Thank you, Andy. DESIGN007

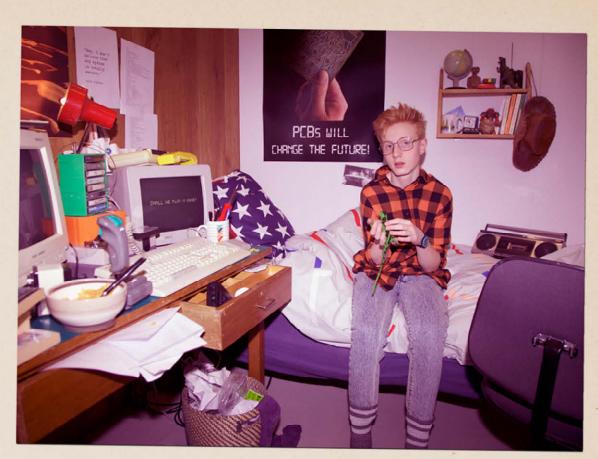

### ME AND GERBER THE LIZARD 1986

## We love PCBs. We always have.

We are the geeks. The nerds. The passionate. We all think, talk and dream about that little green masterpiece. We call it **Your Key Component**. Because that's what it is. And our mission is to **produce PCBs for demanding customers, on time, with zero defects, and at the lowest total cost**.

We are the NCAB Group. One of the world's leading producers of PCBs. We have been producing PCBs, and only PCBs since 1993.

Today our U.S. locations are in: California Illinois New Hampshire Texas Washington

www.ncabgroup.com

#### Feature Interview by Andy Shaughnessy I-CONNECTO07

Artificial intelligence (AI) has been making inroads into a variety of industries in the past decade or so, from automobiles to medical devices. Naturally, EDA tool companies are taking a look at AI. Does AI offer a way forward for PCB design tool developers?

I recently interviewed Paul Musto, director of marketing for the Board Systems Division of Mentor, A Siemens Business. We discussed Mentor's plans for integrating AI into EDA tools, and why we may be at the very beginning of understanding the pros and cons of this new technology.

**Andy Shaughnessy:** Paul, what do you think about AI and where it is right now?

**Paul Musto:** Artificial intelligence, where computers are trained to perform tasks that normally require human intelligence, will have a place in almost every facet of our lives. We

are really at the beginning of understanding the implications and opportunities of AI. As the technology matures, it's not hard to imagine that AI will have a critical role in product development.

**Shaughnessy:** How likely it is that we'll see more AI in EDA tools? With chunks of AI in EDA tools already, like for reuse and things like that, is there a place for more AI in EDA tools?

**Musto:** It's very likely, and we are at the beginning of this journey. If you look at the mechanical engineering world, you see examples, like generative design. With AI software and the cloud-based computing power, generative design enables engineers to create thousands of design options by simply defining their design problem, such as basic parameters like height, weight, strength, and material options. As AI becomes more integrated, you will see better, more productive application of generative design principals. There is reason

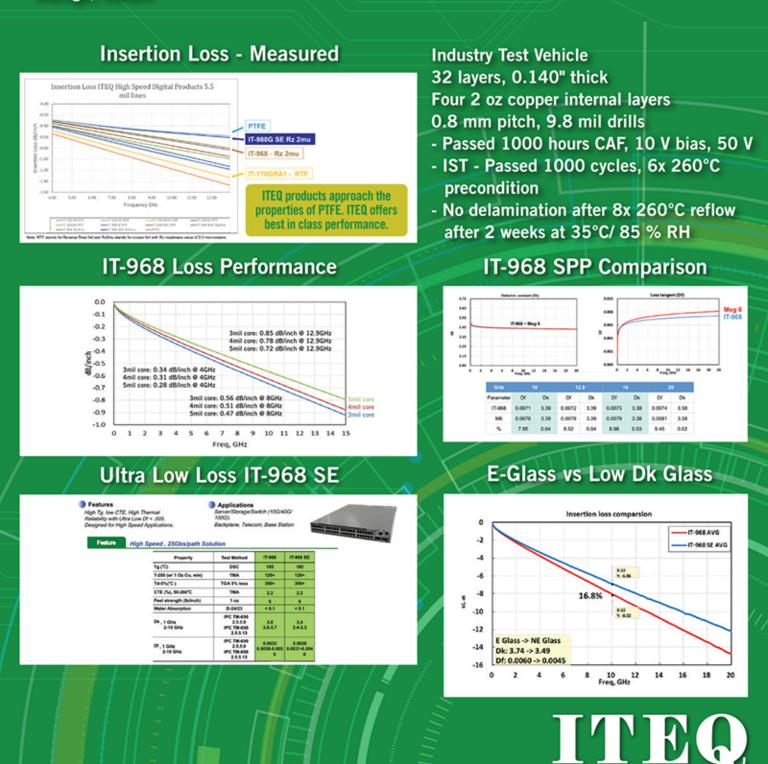

## IT-968 / IT-968 SE

High Thermal Reliability Designed for High Speed Digital Applications - Telecom, Backplane, Base Station, Server, Storage, Switch IT-968 SE Dk @ 10 GHz - 3.85 Dk @ 10 GHz - 3.30 Df @ 10 GHz - 0.0043 Df @ 10 GHz - 0.0019

to expect that to happen in the EDA world and in PCB design. Mentor, as part of Siemens, is well positioned to take advantage of Siemens' delivery of a digital thread, which includes product design, manufacturing process, and product performance. We will be able to capture and rationalize data from a myriad of sources like requirements, actual manufacturing data, or field performance, and use that intelligent data to drive better design practices. The basis of our future AI

won't be built on design

Paul Musto

automation alone, but on predictive principals based on actual manufacturing and field performance.

**Shaughnessy:** Can you describe what Mentor is doing in AI?

**Musto:** Being part of Siemens gives us real advantages to deliver cutting-edge solutions to our customers. A key area of investment is in simulation technologies and in design exploration and design recommendations.

**Shaughnessy:** What consumer applications have you seen that use AI?

**Musto:** Obviously, I am a gadget freak. I have home automation assistants in my house. All of us are familiar with Amazon and digital services like Netflix or Spotify that give users recommendations based on past consumption behavior and search history. Can you imagine these applications in EDA? Like implementation wizards based on predictive analytics, simulation models, manufacturing resources and availability, or field performance.

**Shaughnessy:** Should designers be worried that they'll be out of a job if AI has a greater role in

EDA? Some designers tell me, "We're the AI!"

Musto: Obviously, the topic of AI brings anxiety to any workforce. My recommendation is that we focus on the upside versus downside. We have been here before with automation, like Mentor's automated Sketch Router technology, or our concurrent platforms for design collaboration. All of these met some resistance in that productivity advances could eliminate skilled workforces. This simply did not happen. What has

happened is that design teams are much more productive than ever, and design starts seem to be increasing all the time. These automated technologies actually allowed design teams to invest more time in design innovation.

With designs becoming more complex and with increased electronics content in everything, it's hard to imagine that AI will completely replace entire workforces. What it will mean is that our expertise will be focused on areas where we are underinvesting now, such as better simulation techniques or innovation initiatives in product design or packaging. With the electronics industry growing at an amazing pace, it's hard to imagine the work ending any time soon. If anything, we need more engineers to apply these emerging technologies, and Siemens is committed to industrial digitization and innovation.

**Shaughnessy:** Sounds like we're in a really interesting time, for designers and for EDA companies. Thanks for your time, Paul.

**MUSTO:** Thank you, Andy. Always good to talk with you. **DESIGN007**

Undoubtedly, China has become the largest supply base of PCBs and Printed Circuit Board Assemblies. With so many self-styled "reliable cheap PCB Manufacturing Solution suppliers", are you capable of picking up a long-term partner for your projects?

#### CHECK HOW TO MAKE THE BEST OF CHINA'S PCB MANUFACTURING RESOURCES

PCBCart is among the very first Chinese suppliers who take care of international customers' PCB manufacturing demands. Till now, we've been manufacturing PCBs for over 10,000 customers from 80+ countries, most of them have been working with us since our establishment. Here are our commitments:

- We never offer poor quality PCBs

- We give the best balance on price-quality-service

- We never share customers' project design with third parties

## **PGD PCB007** Highlights

#### Industry Veteran Nolan Johnson Joins I-Connect007 Editorial Team >

I-Connect007 welcomes the recent addition of industry veteran Nolan Johnson to its editorial team. In his new position, Johnson will take over as managing editor of *SMT007 Magazine* and *PCB007 Magazine*. Nolan brings 30 years of career experience focused almost entirely on electronics design and manufacturing.

#### An Owner's Positive Take on IMPACT 2018: American Standard Circuits' Founder & Chairman Gordhan Patel ►

During a full day at IMPACT 2018, I had a chance to speak with American Standard Circuits' founder and chairman Gordhan Patel. We had much to talk about after listening to several speakers from the departments of Defense and Education, and the International Trade Administration.

#### Welcome to the Silicon Valley Neighborhood: Nano Dimension Arrives in California >

I-Connect007 Technical Editor Dan Feinberg accepted an invitation recently to tour Nano Dimension's new USA headquarters in Santa Clara's Silicon Valley, which included a sitdown with President and Co-Founder Simon Fried.

#### The PCB Norsemen: Lean Challenges— Standard vs. Non-Standard Products >

Writes Didrick Bech: People tend to treat standard and non-standard products in the same way; however, they represent two parallel product segments and consequently different challenges for your Lean manufacturing process, especially in relation to production and logistical operations. When you fail to differentiate the processing of standard and non-standard products, not only is the Lean manufacturing process disrupted, but you also introduce a variety of production, financial and logistical challenges.

#### Graphic PLC Team Completes Business Improvement Apprenticeship >

The 12-month program is a formally recognized NVQ apprenticeship qualification combining classroom-based learning and simulations alongside practical improvement projects, providing an opportunity to apply the skills they have gained.

#### DSBJ Completes Acquisition of Multek >

Multek announced the completion of its previously announced acquisition by Suzhou Dongshan Precision Manufacturing Co. Ltd., a diversified manufacturer headquartered in Suzhou, China.

## It's Only Common Sense: A Peek at Future Technological Advancements >

It's that time again—time for a peek into the future. The following ideas come from an excellent book by Mark Penn called Microtrends Squared: The New Small Forces Driving Today's Big Disruptions.

## One World, One Industry: Automotive Electronics–Past/Present/Future >

As electronics play an increasingly important role in automotive manufacturing, tremendous change and great progress have been made worldwide. We are at the crossroads of incredible technological advancements, and it's been exhilarating to watch. I am eager to see what happens next.

## **Mendr**® A Siemens Business

## Speed up your **PCB** design verification by up to

## Get HyperLynx DRC for FREE for 12 months **COMPATIBLE WITH ANY PCB LAYOUT TOOL!**

www.mentor.com/get-drc

## 10 Fundamental Rules of High-Speed PCB Design, Part 1

#### **Beyond Design**

by Barry Oiney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

Over the years, I have focused on highspeed design, signal and power integrity, and EMC design techniques in a plethora of published technical articles—all of which have key points to consider and present a tremendous amount of information to absorb. In my next few columns, I will elaborate on ten of the most important considerations to embrace to achieve successful high-speed PCB designs that perform reliably to expectations.

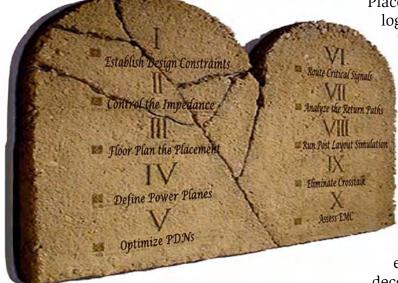

Figure 1 lists the 10 fundamental rules of high-speed PCB design that I deem the most important to follow, although they may change after months of deliberation, like what happened with the laws of thermodynamics. The first established thermodynamic principle, which eventually became the second law, was formulated by Sadi Carnot in 1824. By the late 1800s, three laws of thermodynamics were clearly defined. However, in the 1930s—long after these three laws were already widely

Figure 1: The 10 fundamental rules of high-speed PCB design.

accepted—Sir Ralph Fowler and E.A. Guggenheim felt that another law, which they saw as the foundation of earlier laws, should be incorporated. Hence, it was numbered the zeroth law. Thus, there is always room for one more at the top!

The 10 fundamental rules of high-speed PCB design are:

#### I. Establish Design Constraints

Always create a strategy for high-speed design requirements and set constraints based on pre-layout analyses or recommendations and guidelines prior to commencing the design.

#### II. Control the Impedance

Match the transmission line impedance to the driver and load. Create the stackup and define terminations to match the impedance.

#### III. Floor Plan the Placement Based on Connectivity

Place components by functionality and analog and digital groups to minimize interac-

tion between different logic families and improve routability and timing.

#### IV. Define the Power Delivery Planes and Paths

Define the power/ground regions and plane layers. Partition (not split) the ground planes.

#### V. Optimize the Power Distribution Networks (PDNs)

Create a low AC impedance delivery path by optimizing the bypass and

decoupling capacitors and mounting inductance and plane resonance from DC to the

#### www.nisteceltek.com

## eltek

a Nistec company

## Helping people live longer, healthier lives for more than 25 years.

Eltek is trusted supplier of complex PCBs for medical devices. Our manufacturing expertise ranges from implantable devices like pacemakers and neurostimulators, to insulin delivery systems and advanced medical imaging products.

Product quality and reliability are critical to success in this field. Eltek's advanced manufacturing capabilities and technical support are designed to mitigate risks and deliver products that meet and exceed the most stringent standards of the industry regulatory bodies.

For over 25 years, Eltek's PCB solutions have been helping people live longer and healthier lives.

#### Learn More

maximum required frequency (including harmonics).

#### VI. Route the Board Based on Critical Signals

Adhere to the defined routing strategy. Clock signals should always have the longest delay of the group. Differential pairs should maintain constant impedance along the entire length.

#### VII. Analyze the Return Current Paths

All signal traces should be tightly coupled to a contiguous reference plane and have a clearly defined minimum loop inductance return current path.

#### VIII. Run the Post-Layout Simulation

Simulate critical signals and match signal propagation and timing. Check for signal ringing and eye jitter.

#### IX. Eliminate Crosstalk

Scan the board for possible crosstalk. Crosstalk can be coupled trace-to-trace on the same layer or broadside coupled by traces on adjacent layers.

#### X. Assess Electromagnetic Compliancy (EMC)

Control EM radiation at the source. Ensure that differential mode signals do not convert to common mode and eliminate any possible antennae.

Without further ado, I will begin with an elaboration of the first rule: Establish design constraints.

Complex, high-speed multilayer boards should be designed using a proven design methodology incorporating a pre-layout simulation before placing a single chip on the board. This includes reviewing component datasheets and design recommendations prior to the schematic capture. Simulation tools can be used to analyze various issues, such as reflections due to impedance discontinuities, crosstalk, signal attenuation, and PDN noise—all of which can impact interconnect performance.

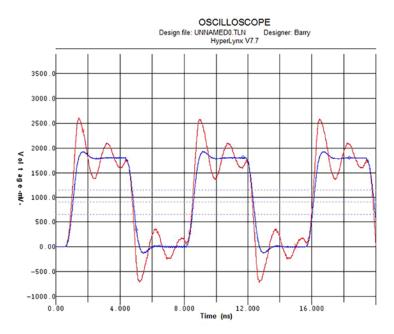

Simulation of a PCB design after placement

Figure 2: Pre-layout simulation with correction of clock ringing. (Source: HyperLynx)

and routing is recommended, but simulation early in the design phase is even better. Both are essential. Pre-layout analyses allow critical interface topologies, termination schemes, and I/O buffer selections to be defined and analyzed for synchronous, source-synchronous, and clock interfaces before placement and routing. Figure 2 depicts a simulated clock signal with (blue) and without (red) a series termination. Simulation opens one's eyes to what the circuitry is doing. It also leads to an enhanced perception of what might be a potential issue once the system is built.

There are multiple facets to pre-layout analyses, including:

- Stackup planning for controlled impedance, signal integrity, and crosstalk

- Dielectric material selection for highfrequency operation, manufacturing yield, and cost control

- I/O buffer and drive strength selection

- Topology optimization for signal integrity, timing, and EMC

- Series and parallel termination strategy

- Derived layout routing constraints, including trace width, spacing, and delay/ length matching

- PDN analysis and decoupling capacitor optimization

- Signal integrity analysis to meet the design specifications with respect to noise margins, timing, skew, crosstalk, and signal distortion

Pre-layout simulations also allow a designer to identify and eliminate signal integrity, crosstalk, and EMC issues early in the design process. This is the most cost-effective way to design a board with fewer iterations. However, if you do not have access to simulation tools, then follow best practices from Design007 Magazine, IC manufacturers guidelines, etc.

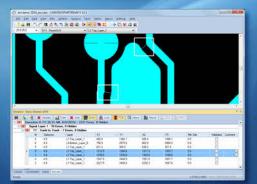

While designs continue to increase in complexity and time-to-market remains critical, it is imperative to have a constraint system that is integral to your design flow. The constraints based on a pre-layout simulation—manufacturing restrictions, and IC manufacturer's recommendations and guidelines should flow from pre-schematic to PCB layout, routing, fabrication, and assembly. Before starting placement and routing, detailed interconnect routing constraints should be established (Figure 3). Of course, these are based on the pre-layout simulation and impedance requirements. Firstly, determine the single-ended and differential impedance required for each technology used. Synchronous bus delay or length matching should be set up in the constraints editor along with differential pair rules and clearance between signal groups to prevent crosstalk while giving priority to critical signals.

Appropriate grouping and defining of net and constraint classes in the early stages of the design process significantly simplifies constraint definition and management. Grouped constraints can increase layout efficiency, reduce design time, and ultimately lower PCB design costs.

The prime objective behind setting constraints up front is to ensure that the design is going to perform to expectations. It is essential that the system can alert the designer to any errors as they occur. Interactive design rule

| avigator + # ×<br>B Schemes<br>Net Classes                                                           | Constraint Class/Net                   | ▪ O A | Net Class          | Topology |         |

|------------------------------------------------------------------------------------------------------|----------------------------------------|-------|--------------------|----------|---------|

|                                                                                                      |                                        |       |                    | Туре     | Ordered |

| (Default)                                                                                            | E Mp (All)                             |       | (Default)          | MST      |         |

| DDR2_Addr_Cntrl<br>DDR2_Clocks<br>DDR2_Clocks                                                        | 🗄 🦮 DDR2                               | -     | (Default)          | MST      |         |

|                                                                                                      | DDR2_Unused                            |       | (Default)          | MST      |         |

|                                                                                                      | 🖯 🦮 DDR3                               |       | (Default)          | MST      |         |

| DDR2_Strobes                                                                                         | 🗄 🦬 Address                            |       | ddr3_address       | MST      |         |

| ddr3_clocks                                                                                          | 🗄 🦮 clocks                             |       | ddr3_clocks        | Chained  |         |

| ddr3_control<br>ddr3_extra<br>ddr3_extra<br>ddr3_group0<br>ddr3_group1<br>ddr3_group1<br>ddr3_group2 | 🗄 🦮 control                            |       | ddr3_control       | MST      |         |

|                                                                                                      | 🖃 🦮 Data                               |       | (Default)          | MST      |         |

|                                                                                                      | E >>> Group0_1                         |       | (Default)          | MST      |         |

|                                                                                                      | E M Group2_3                           |       | (Default)          | MST      |         |

| ddr3_group3                                                                                          | ExpoDemoAnalog3v_(All)                 |       | ExpoDemoAnalog3v_( | MST      |         |

| Diff Diff                                                                                            | ExpoDemoPower0_9_(All)                 |       | ExpoDemoPower0_9_( | MST      | 1       |

| ExpoDemoAnalog3v_(Defa.                                                                              | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |       | ExpoDemoPower_(Def | MST      |         |

| ExpoDemoPower0_9_(Defa                                                                               | 🕀 🎠 fs_addr                            |       | (Default)          | MST      |         |

| EpoDemoPower_(Default)                                                                               | 🗄 🦮 fs_data                            |       | (Default)          | MST      |         |

| PCI_Diffpairs                                                                                        | 🕀 🦮 mictors                            |       | (Default)          | MST      |         |

| PCL_RX_Diffpairs<br>PCL_TX_Diffpairs<br>Power<br>Special<br>Constraint Classes<br>Pats               | PCI_Express                            |       | PCI_Diffpairs      | MST      |         |

|                                                                                                      | Power_0_9_(All)                        |       | (Default)          | MST      |         |

|                                                                                                      | Power_1_5_(All)                        |       | ExpoDemoPower_(Def | MST      |         |

|                                                                                                      | Power_1_x_(All)                        |       | (Default)          | MST      |         |

|                                                                                                      | Power_3_0_(All)                        |       | ExpoDemoAnalog3v_( | MST      |         |

|                                                                                                      | Power_3_x_(All)                        |       | (Default)          | MST      |         |

Figure 3: Typical high-speed design constraints. (Source: PADS Professional Constraint Manager)

checks (DRCs), which are adhered to throughout the design cycle, provide for an error-free, correct-by-construction design when carefully planned early in the design phase.

A robust constraint management system should be unified and integrated into the schematic and layout editors with cross-probing, including:

- Integrated topology-driven constraint definition

- Controlled impedance rules, including spacing and clearance to other nets

- Length or time-based constraints

- Electrical constraints with custom equation capability

- Physical trace and spacing rules (class-to-class rules, etc.)

- Region and technology rules

- Same net DRCs for advanced technologies (HDI)

- PCB fabrication, assembly, and testability rules (if required)

Although all designs are different, one should reuse existing rules where possible as a template to eliminate the need for re-entry of any common constraints. These include DDRx, PCIe, USB, SATA, Ethernet, differential pair rules, manufacturing requirements, etc. This also minimizes the possibility of input errors.

When constraints are defined at the beginning of the design process, designers can be confident that once the design phase is completed, the product will move through the production phases with fewer errors. A constraint management system that can check work in real time as the design process is executed provides reduced risk and peace of mind that the constraints will prevent the PCB designer from violating the rules set up front. Although we cannot plan for the unexpected, having a reliable constraint management system in place will ensure that the majority of issues are covered and will alert you if any unforeseen issues arise.

Stay tuned for next month's column that will continue to elaborate on the 10 fundamental rules of high-speed PCB design.

#### **Key Points**

- Simulation of a PCB design early in the design process is essential

- Pre-layout simulation leads to an enhanced perception of what might be a potential issue once the system is built

- It is imperative to have a constraint system that is integral to your design flow

- Detailed interconnect routing constraints should be established before starting placement and routing

- The prime objective behind setting constraints up front is to ensure that the design is going to perform to expectations

- Reuse existing rules when possible to eliminate the need for re-entry of any common constraints

- A constraint management system that can check work in real time as the design process is executed provides reduced risk and peace of mind

#### **Further Reading**

• Beyond Design: Pre-Layout Simulation by Barry Olney, The PCB Magazine, July 2012.

• Beyond Design: Split Planes in Multilayer PCBs by Barry Olney, The PCB Design Magazine, March 2015.

• Beyond Design: Plane Crazy, Part 1 by Barry Olney, The PCB Design Magazine, December 2015.

• Beyond Design: Interactive Placement and Routing Strategies by Barry Olney, The PCB Design Magazine, December 2012.

• Beyond Design: Controlling Emissions and Improving EMC by Barry Olney, The PCB Design Magazine, August 2011.

• 5 Ways to Assess PCB Constraint Management Systems for High-Speed Designs, EMA Design Automation Blog.

• Why impose PCB design constraints? by Steve Hughes of Mentor, a Siemens Business.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in board-level simulation. The company developed the iCD Design Integrity software incor-

porating the iCD Stackup, PDN, and CPW Planner. The software can be downloaded from www.icd.com.au. To read past columns or contact Olney, click here.

## VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

## **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

©2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

#### Visit downstreamtech.com or call 800-535-3226

## Embedding Components, Part 3: Implementing Discrete Passive Devices

#### **Designers Notebook**

by Vern Solberg, CONSULTANT

Note: Part 1 of this column appeared in the June 2017 issue of *The PCB Magazine* and Part 2 appeared in the June 2017 issue of *The PCB Design Magazine*.

For many, the driving force to integrate passive components within the layers of the PCB structure was the need for providing the consumer with smaller and lighter products. Once the commercial sector began developing and refining embedded component processes and overcoming quality and reliability issues, the automotive, telecom, aeronautic, and aerospace industries recognized the advantages of embedded passives technology for the following benefits:

- Improved density and functionality

- Reduced PCB area and weight

- Increased assembly process efficiency

- Improved functional performance and reliability

Most of the passive components used in electronics are discrete surface mount components configured to mount onto land patterns furnished on the surface of a PC board. Designers have several choices for providing passive functions in a system design, such as discrete surface-mounted passives, array passives or passive networks, integrated (Rs and Cs) passive devices, and embedded discrete passive components. A growing number of PCB sup-

# Candor Circuit Boards

# Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

#### www.candorind.com | (416) 736-6306

pliers with experience in build-up of circuits can embed both passive and active components. Although a majority of companies furnishing high-volume embedded component circuit boards are in Europe and Asia, there are number of proficient North American suppliers as well.

Providing formed resistors and capacitors within the circuit structure remains the most economical process with the least level of risk; however, value range and tolerance control is somewhat limited.

Providing formed resistors and capacitors within the circuit structure remains the most economical process with the least level of risk; however, value range and tolerance control is somewhat limited. Placing discrete component elements furnishes a greater value range and superior tolerances.

#### **Embedded Component Process Planning**

The process for embedding discrete passive component elements within the multilayer PCB structure is a sequential process requiring specialized SMT process skills and assembly systems typically outside the realm of the average circuit board supply chain—a process capability more common to OEMs and boardlevel assembly service providers. To prepare for efficient high-volume production, the PCB fabricator will need to establish in-house component placements and attachment capabilities and reliable component sources or develop partners for the procurement of components that are suitable for embedding. The PCB supplier must also determine which systems and methodologies will be required for applying termination materials (conductive polymer or solder) that can ensure precise component

placements, curing polymers or reflowing solders, and specialized systems required for electrical testing during the progressive stages of the fabrication process.

When choosing discrete resistor, capacitor, and inductor components for embedding, both device outline and thickness must be considered. While some passive components are very thin and require no special preparation, others may have profile dimensions requiring encroachment into contiguous circuit layers.

#### **Discrete Resistors**

Several companies are now able to furnish thin, small outline resistors and capacitors that prove to be ideal for embedded component applications. The outline of currently available components can be as small as 0.4 mm x 0.2 mm (01005) and 0.6 mm x 0.3 mm (0201). Discrete thick-film resistors are offered in a 0.015-mm profile. Specifically developed for embedding, these devices are described as a flat thick-film resistor furnishing a value range of 1.0  $\Omega$  to ~ 10 M $\Omega$  with a power rating of 0.063 watts and working voltage maxing out at 50 volts.

Although these devices have a relatively low power rating, the operating temperature range, resistor value, and tolerance (1% and 5%) specified for the smaller devices are the same as the larger resistor variations and available with copper terminals. While tin-based alloy terminals are acceptable for solder or conductive polymer termination, copper terminals will be necessary when using plated microvia interface technology. For applications requiring resistor value tolerances less than 1%, an alternative nickel-chromium thin-film family is available, but the package dimensions are significantly greater than the thick-film resistor previously described.

#### **Discrete Capacitors**

Low-profile ceramic capacitors have been developed for height-restricted applications where device thickness is a key design constraint—perfect for embedded or other applications with thickness limitations. Ideal for decoupling and filtering applications, the comPowerful Schematic Capture and PCB Design Software

# Are you looking for cost effective **PCB Design Software?**

### Look no further, **Pulsonix** is the answer

- Very easy to learn and use

- Co-design in integrated PCB/3D design environment

- Import design data from your existing CAD tool

- High Speed design with Constraint Manager

- Free access to over 13 million library parts

- STEP integration with Mechanical CAD

- Reverse Engineer feature to PCB from Gerber files

# Download a FREE trial from **pulsonix.com**

Contact us today and see how Pulsonix can work for you:

Email sales@pulsonix.com

### www.pulsonix.com

ponents are available with the same small outline dimensions as the resistor family, but device thickness will vary somewhat due to the dielectric type and required volume.

For example, the body thickness for the 01005 capacitor is specified as 0.20 mm while the 0201 outline component thickness can increase to 0.30 mm. Additionally, the dielectric type and working voltage will impose limits on the capacitor value range for these smaller device outline families. The 01005 and 0201 type capacitors with a COG dielectric are available in a value range of 5-100 pF. The X7R dielectric capacitors can furnish a value range of 68-470 pF for the 01005 capacitor and 68-10,000 pF for the 0201 variation. The standard terminal plating is tin-alloy over a nickel base metalization for solder and conductive polymer attachment. Because the base layer is a nickel-alloy, termination of the component to the circuit conductor pattern with copperplated microvias may be possible.

#### **Discrete Inductors**

A limited value range of miniature inductors is available from several leading suppliers. The multilayer ceramic inductor family is available in both 0402 and 0603 (1.0 mm x 0.50 mm and 1.60 mm x 0.80 mm) outlines with a thickness equal to the device width (0.50 mm for the 0402 device and 0.80 mm for the 0603 variation). The terminal plating is a nickelalloy with a tin-alloy based coating for solder or conductive polymer interface.

The available inductance value ranges between 6.8 nH for the low and 220 nH for the high with a tolerance value of +/-5%. An alternative thin-film small outline and lowprofile inductor family is available too. For this variation, the inductor element is printed onto the surface of a ceramic base material, passivated and fired to protect the printed pattern, and furnished with a tin-alloy terminal for joining to the circuit structure. Small outline thin-film inductor elements will range in size from 0402 to 0603. The actual dimensions for the 0402 device are 1.0 mm x 0.50 mm x 0.35 mm, and 1.6 mm x 0.8 mm x 0.50 mm for the 0603 device. The value range for these two thin-film inductor components is between 1.0 nH and 82 nH with a tolerance of +/-2%. Manufacturers claim that the miniature inductors furnish up to twice the rated current and half the DC resistance of comparable ferrite inductors. Designers should be aware that inductors size and value range varies somewhat between suppliers.

#### **Next Column**

Part 4 of this embedded component technology series will focus on land pattern development criteria, ways to accommodate higher profile passive components, and alternative termination methodologies.

#### **Upcoming Appearance**

Vern Solberg will be conducting a half-day professional development course on "Design and Assembly Process Principles for High-Density Flexible and Rigid Flex Circuits" at SMTA International 2018 in Rosemont, Illinois, on Sunday, October 14 from 8:30 a.m.–12:00 p.m.

This tutorial has been developed primarily for design professionals with a focus on applying best design practices for fabricating flexible and rigid-flex circuits. Participants will have an opportunity to study and discuss alternative fabrication methodologies as well as practical guidelines for implementing automated assembly processing. Information presented will also include the selection criteria for base materials, alternative fabrication methodologies, SMT component selection, land pattern development, and features required to accommodate SMT-on-flex assembly.

For further information on this conference and to sign up for this tutorial (PDC 01), click here. **DESIGN007**

**Vern Solberg** is an independent technical consultant specializing in surface mount technology, microelectronics design, and manufacturing technology. To read past columns or contact Solberg, click here.

### Your signal needs to get around the world fast... Why go halfway around the world to get your high-speed PCBs?

# ACE: your high-speed experts right here at home, specializing in microwave and hybrid PCBs.

Accurate Circuit Engineering 3019 Kilson Dr Santa Ana, CA 92707

(714) 546-2162 • sales@ace-pcb.com

For technical assistance, call: James Hofer (714) 227-9540

www.ace-pcb.com

RoHS & WEEE compliant • Certified AS9100, ISO, ITAR, MIL-PRF-31032 & 55110

## **Contract Positions:** Go the Extra Mile

#### Tim's Takeaways by Tim Haag, Consultant

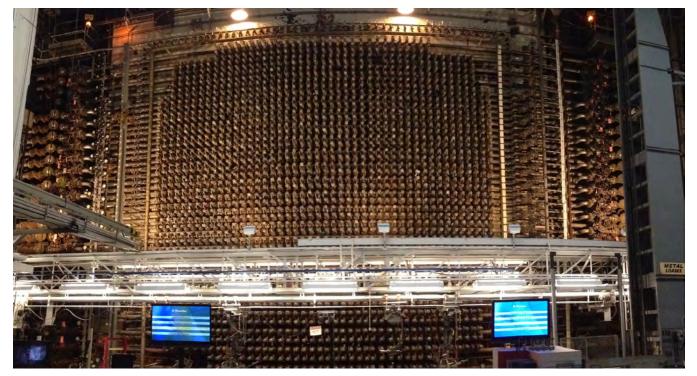

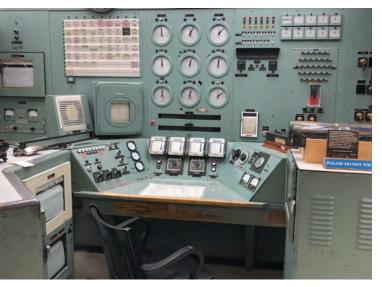

A few years back while vacationing in the Tri-Cities area of Eastern Washington, my wife and I took a tour of the Hanford Site near Richland. The Hanford Site contains nine nuclear reactors used to produce fissionable materials in atomic weapons. These reactors were all shut down by the fall of 1989 and are now being cleaned up and entombed to protect the environment. However, the very first one built—B Reactor—has been designated a national landmark and refurbished for tours<sup>[1]</sup>.

The tour was a fascinating experience and I would highly recommend it if you are ever in the area. The fact that the whole project was put together during World War II, in such a short amount of time, is amazing. Hundreds of thousands of people were involved in different sites across the country and most did not know what was being produced—only that it was critical for the war effort.

A whole city was created at the Hanford Site, with housing, shopping, hospitals, schools, and entertainment facilities for those who worked there <sup>[2]</sup>. Of course, the creation and use of atomic weapons is a very serious matter and I am not trying to comment on either side of the issue. Instead, I want to look at how and what these people did to accomplish something that had never been done before. For example, simply providing dessert for the workers required machines to create over 7,000 pies for just for one meal served in the cafeterias that totaled eight football fields in size.

The reason I bring this up is to highlight an engineering achievement. The original design for the reactor came from scientists at the Metallurgical Laboratory (Met Lab) in Chicago, and they specified that the reactor needed to be built with 1,500 fuel tubes <sup>[3]</sup>. However, the engineers from DuPont who built the reactor

Figure 1: Fuel tube loading face at B Reactor. Go ahead-count them.

Flexible, reliable Supply<br/>Chain Solutionshigh quality copper clad<br/>laminates & prepreg<br/>bonding materials

Ventec International Group is a world leader in the production of high quality and high performance copper clad laminates and prepregs, with full R&D and product development capabilities. Our global distribution means we can readily supply our products to all markets in all geographic areas.

Get your free copy of The Printed Circuit Designer's Guide to...Thermal Management with Insulated Metal Substrates.

DOWNLOAD NOW

# Ventec - wherever technology takes you, we deliver

#### Ventec International Group

ventec

INTERNATIONAL GROUP

**螣**輝雷子

179 Ward Hill Ave, Ward Hill, MA 01835, United States T: 978-521-9700 E: ordersCA@ventec-usa.com Y Follow @VentecLaminates

www.venteclaminates.com

Figure 2: Control room.

argued for additional fuel tubes even though many scientists seriously objected. The engineers based their request on years of experience building industrial plants. In the end, they won the argument and were able to build the reactor the way they wanted. Although it was a significant increase in cost, the engineers completed the reactor with a total of 2,004 fuel tubes.

Early in the morning on September 27, 1944, the first nuclear reaction started in reactor B (Figure 1). Engineers decided to only use the original 1,500 fuel tubes in the first test and the reactor performed above expectations. However, after less than a day of operation, the reactor experienced a problem that caused it to lose power and shut itself down. This problem initially baffled the reactor operators, but they eventually discovered the issue was caused by xenon that had been produced as a byproduct of the fission process. The operators determined that the solution was to increase the power of the reactor. After some recalculations, the full array of 2,004 fuel tubes was loaded and the reactor was back to full power with the xenon problem eliminated by December 26.

If not for the persistence of the engineers wanting to build in a safety margin in the original reactor design, the reactor would have required a complete rebuild to operate. This would have affected the reactor's ability to produce fissionable material for the war effort by a considerable amount of time while it was upgraded.

My dad used to say, "A job worth doing is worth doing right." I cannot tell you how many times I heard this axiom growing up—too many to keep count—and I eventually started to hate hearing him say it. But in the end, he was right, and the story about the DuPont engineers over-building the Hanford reactor is a great example of it. They saved the day by going the extra mile.

I'm sure there are many other stories of engineering feats that saved the day due to the persistence of those who made sure that the job was done right the first time. So how does this apply to us now?

#### **Contract Positions**

With the way the PCB design industry is changing, many folks are undergoing career changes. Some are changing jobs or fields, and others are looking for contract work rather than full-time employment. For newbies just entering the industry or experienced designers who have always worked for a corporation, the transition to contractor can be a real culture shock. The allure of working from home and setting your own hours can quickly be replaced by the realities of chasing jobs and wondering where your next payday will come from.

However, there are some wonderful aspects of working as a contractor that can make it very worthwhile. You have more freedom to make your own choices about what you will be doing and where, and you are not as tied to a single company or specific way of doing things. Working as a contractor can be great, but the key to success is being prepared for the differences.

#### Tips

Here are some ideas to help anyone starting a contract position:

• Show up ahead of schedule: I've heard from more than one manager who has a negative impression of contractors because they don't seem to follow through on commitments they have made. I've experienced this myself with contractors outside of the PCB design industry, such as painters or builders who arrive days or even weeks late with excuses that would make for excellent plot twists in a novel. Don't be that person. When you commit to being somewhere or doing something, make sure you are ready to go ahead of schedule.

• Close your mouth and open your ears: I'm always amazed when I work with someone new in a job and they try to come across as an expert in something they aren't. I realize that the temptation is to try to make a good impression, but doing so when you clearly don't know what you are talking about only makes you look worse. Meanwhile...

• Don't be afraid to show your expertise when required: It is likely that you were hired as a contractor because of your expertise in a certain area. When your boss or co-workers look to you for help, this is when you need to shine. However, be cautious of shining so brightly that you blind everyone. You want to be a flashlight that can expertly help others through the darkness as opposed to a floodlight that leaves everyone squinting from too much light.

• Don't overcharge: When you bill for the time you've worked, make sure you work more than what you bill. I'm not talking about giving away the farm—just make sure your customers feel like they are getting more than their money's worth. The last thing you want is to become known as the person who cuts out early and isn't worth what they're being paid. It is much better to add a few minutes to your schedule each day so that your customers feel that paying you is a good deal for them.

• Do the job right: Thanks for the advice, Dad. I have known people who don't always give their best while at work. This can happen with full-time employment as there are often ways to work the system in order to get away with it. If you've ever read the Dilbert comic strip, you know there are real-life "Wallys" in the work world that always seem to be on a coffee break. This lazy attitude won't work for you as a contractor. If your customer doesn't feel that they are getting the work out of you that they are expecting, they will simply cut you loose. Again, don't be that person. Do your job the best you can.

• Go above and beyond what is expected of you: You have the opportunity to show your customers they made a great choice when they hired you. Don't be afraid to go that extra mile and give them more than they expect. Of course, you do have to balance this out with the reality of being paid for your work. You don't want to give away hours of extra work for free, but when you have the chance to take a little time to overachieve, go for it. Be the person that your customers want to continue to work with for a long time.

#### Conclusion

Most of us do not build nuclear reactors. However, we can learn from the example set by the DuPont engineers at Hanford and make a commitment to be better employees—contractors and part-time or full-time personnel. Not only will this elevate your status in your employer's eyes, but who knows—maybe one day you will get an opportunity to save the day with your extra efforts. It's worth a shot, so go the extra mile.

P.S. I really appreciate you all reading my columns. I hope that my musings have been helpful or at least entertaining. PCB design has been my passion for a long time, and I enjoy sharing my thoughts with the design community. If you have any feedback, shoot me an email. Until next time, keep on designing. **DESIGN007**

#### References

1. Preserving the Hanford B-Reactor: A Monument to the Dawn of the Nuclear Age by Robert F. Potter, American Physical Society.

- 2. B Reactor, Hanford Government.

- 3. Section 8: B Reactor, National Park Service.

**Tim Haag** is a PCB design consultant based in Portland, Oregon. To read past columns or contact Haag, click here.

#### IPC Lauds Government Act to Advance Workforce Education >

IPC—Association Connecting Electronics Industries is applauding the U.S. Congress for sending legislation to President Trump that will strengthen workforce education and training efforts.

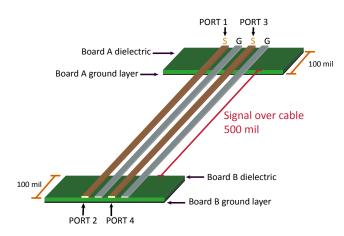

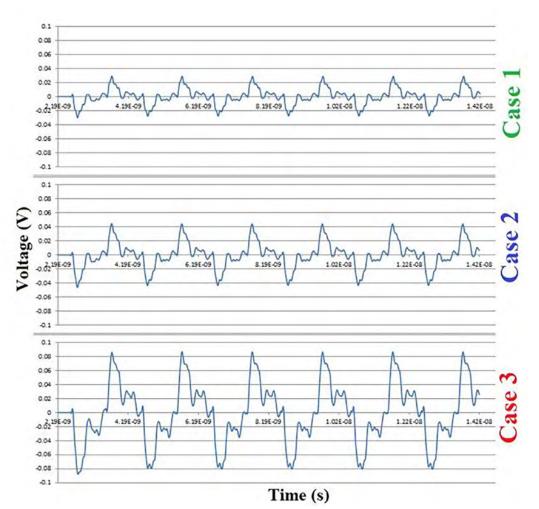

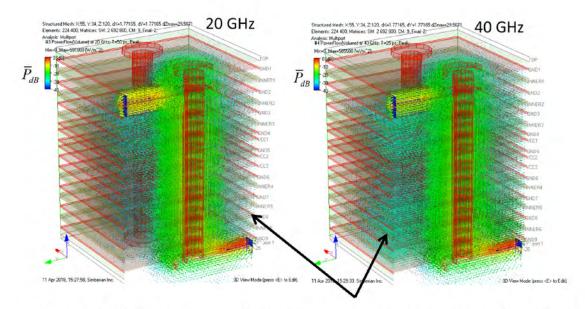

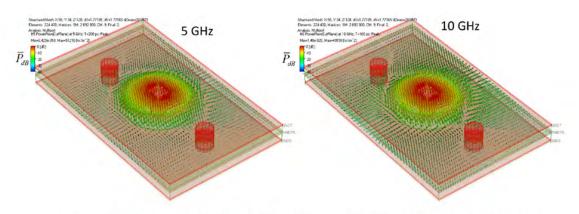

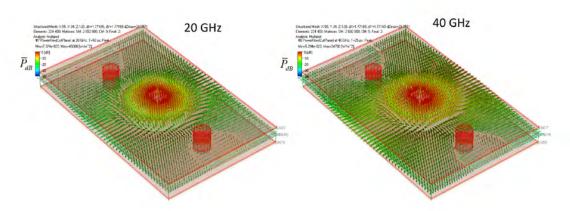

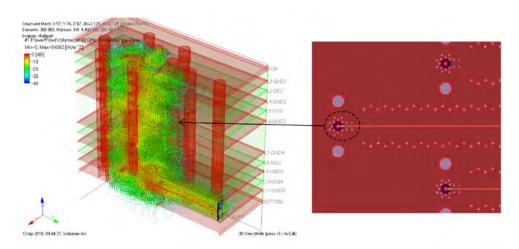

### Eltek Receives Non-Compliance Notice from Nasdaq >