#### PCB007 PRESENTS

Pricing and the Technology Life Cycle by Bill Burr & Nick Pearne

Building HDI Structures Using Thin Films and Low Temperature Sintering Paste by Catherine Shearer, James Haley & Chris Hunrath

# LEARNING CURVES AHEAD NEW NEW INTERCONNECTS

www.mutrack.com

Why did you choose THAT fabricator?

Designers: when you choose a fabricator, what guarantee do you have that they won't deliver scrap?

We can connect you with manufacturers that we have audited and are **qualified to deliver the product that you need**, on time and on budget.

#### How we qualify PCB manufacturers

CLICK TO VIEW

(360) 531-3495 www.nextlevelpcb.com

### THE best way to find a PCB fabricator, anywhere.

Quick Search

Advanced Search

PCB007 PRESENTS

## **New Interconnects**

This month, *The PCB Magazine* looks to the horizon at new and emerging interconnects, with features by BPA and Ormet, along with a comprehensive collaboration between nScrypt and the University of Texas, El Paso.

#### 12 Printed Circuit Structures: The Evolution of Printed Circuit Boards

by Kenneth H. Church, Harvey Tsang, Ricardo Rodriguez, Paul Defembaugh and Raymond Rumpf

28 Pricing and the Technology Life Cycle by Bill Burr and Nick Pearne

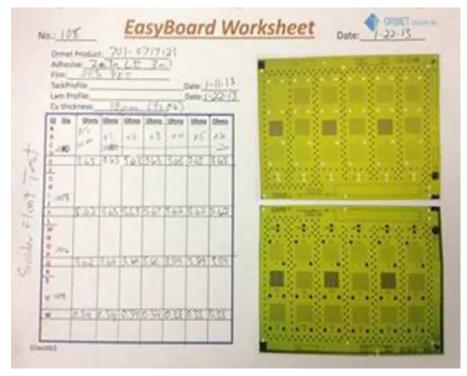

38 Building HDI Structures Using Thin Films and Low Temperature Sintering Paste

by Catherine Shearer, James Haley and Chris Hunrath

# Is Your Coating HYDROPHOBIC PLUS?

## **PlasmaShield™ Conformal Coating**

Protect against liquids, gases & salts Reduce masking of connectors & components Simplify manufacturing & rework

## **SPF™ Semblant Plasma Finish**

PCB Final Finish for tarnish & corrosion protection Flux containment, corrosion protection & reliability PCBA & component mixed flowing gas protection

**Semblant's exclusive focus on the electronics industry** allows it to deliver the ideal protective coating solution addressing the performance needs of traditional high-reliability segments while addressing the un-met total manufacturing cost constraints of high-volume electronics manufacturers.

www.semblant.com

JULY 2013 VOLUME 3 NUMBER 7

THE DEFINITIVE INTERACTIVE MAGAZINE DEDICATED TO THE GLOBAL PCB INDUSTRY the become of the second secon

PCB007 PRESENTS

thepcbmagazine.com

- 8 Here We Go! by Ray Rasmussen

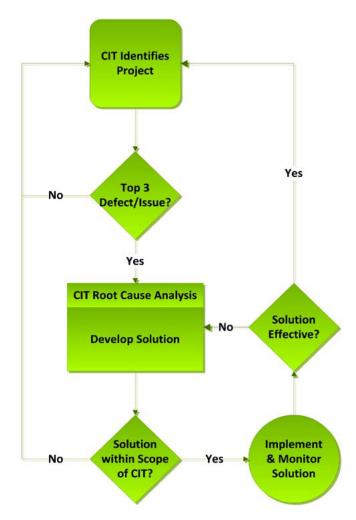

- 46 Operational Excellence Through Continuous Improvement by Steve Williams

- by Steve Williams

52 PTH Voids: Getting to the Root Cause, Part 2

- 60 The Impact of Soldermask Processing on ENIG/ENEPIG Deposit Quality

by George Milad

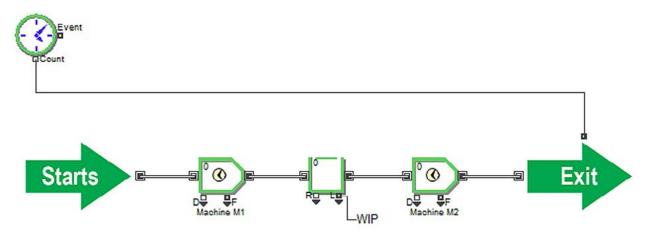

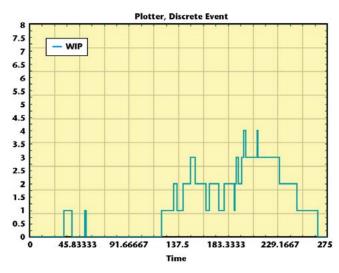

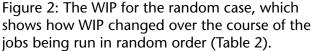

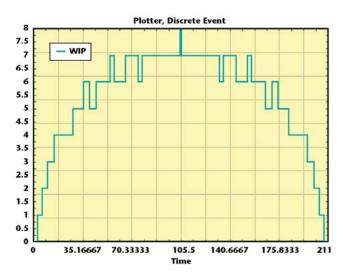

64 What is the DAM Problem with Scheduling? by Gray McQuarrie

EXTRAS

74 Events Calendar

75 Advertisers Index & Masthead

#### VIDEO INTERVIEWS

56 The Future of PE: Assuming the Shape of 3D

63 EMC Laminates and Technica Discuss New Relationship

#### SHORT

26 New Magnetic Phenomenon Leads to Better Data Storage

NEWS HIGHLIGHTS

Mil/Aero007

50 Market

58

- 72 Top Ten PCB007 News Highlights

Military

Test & Measurement

Telecom

I-Speed

Infrastructure

Backplane

### The Next Generation High Speed Product from Isola

- Global Constructions available in all regions

- Optimized Constructions to improve lead free performance

- I-Speed delivers 15-20% lower insertion loss over competitive products through reduced copper roughness and dielectric loss

- Improved Z-axis CTE 2.70%

- I-Speed IPC 4101 Rev. C /21 /24 /121 /124 /129

- Offer spread and square weave glass styles (1067, 1086, 3313, etc.) for laminates and prepregs

- Minimizes micro-Dk effects of glass fabrics

Servers

- Enables the glass to absorb resin better and enhances CAF capabilities

- Improves yields at laser and mechanical drilling

- A low Df product with a low cost of ownership

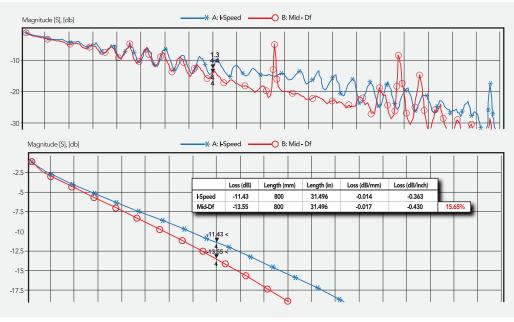

#### Effective Loss @ 4 GHz on a 32 inch line

I-Speed delivers 15-20% lower insertion loss over competitive low Df products.

The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these materials will be goveremed by the terms and conditions of the agreement under which they are sold.

**Isola Corp.,** 3100 West Ray Rd., Suite 301, Chandler, AZ 85226, +1-480-893-6527, www.isola-group.com

## Here We Go!

by Ray Rasmussen I-CONNECT007

I recently talked with a friend of mine who works at Intel. He manages big OEMs that buy ICs in huge quantities for their PCs and other consumer products. We had a short conversation about the market in general, and he said that his customers were starting to put a lot of pressure on him to provide them with the information they need for their next acquisitions.

These OEMs are becoming really impatient; they seem to be under a lot of pressure themselves. My friend said something along the lines of, "I don't know what people are talking about when they mention a slow economy. We're not seeing it." In his world, which slices through consumer electronics, they're all busy. Demand is up.

It sounds to me like the normal build-up to the Christmas season is driving the demand. Maybe the big PC makers feel that if enough folks have figured out how to use Windows 8, more consumers and businesses will take the plunge and upgrade their PCs. We know Apple will likely introduce a new phone this fall (it's

already being built, I suppose), which will generate a lot of activity.

IPC sent over a press release in mid-June titled: *Slow Growth Ahead for Economy and Electronics Industry, According to IPC*. I retitled it, <u>IPC:</u> <u>Economic Growth Ahead</u>. Now, I'm not trying to discount the experts at IPC, but I do believe the market out there could be better than we might think. IPC did talk about the second half being potentially better. Here's a paragraph from that news item.

Economic activity in the U.S. manufacturing sector expanded in March for the fourth consecutive month, and the overall economy grew for the 46<sup>th</sup> consecutive month. IPC's North American Electronics Industry Performance Index reflects an outlook for slow growth in the months ahead. Another leading indicator for electronics supply chain sales growth in North America is the PCB bookto-bill ratio, which reached a 34-month high in April at 1.10, indicating that sales across the supply chain may resume positive growth momentum in the latter half of 2013.

## "Any sufficiently advanced technology is indistinguishable from magic."

-Arthur C. Clarke

# Throw away the rule book—a better way of inner layer production has arrived.

Lunaris will change PCB manufacturing forever. Imagine guaranteed 100% yield into the etch line. Imagine etched and stripped inner layers in less than five minutes from CAM. Imagine replacing 11 of 15 process steps. Imagine all this available on an innovative pay-per-use model. It's time for a better way of inner layer production. It's time for Lunaris.

www.mutracx.com

IPC seems to be taking a very cautious approach, not wanting to appear too optimistic. It just doesn't feel dreary and dismal out there to me, but rather bright and cheery. At least, that's how I see it.

I sent another item to a friend who works in the construction industry: <u>Homebuilder</u>

<u>Confidence in U.S. Rises to a Seven-</u> <u>Year High</u>. That's always a good sign and bodes well for the overall economy.

Now, check out this PBS interview with Charles Morris, the man who predicted the crash of 2008. The article, Comeback: Why the U.S. Sits at the Brink of a New Boom, talks about an unprecedented recovery and boom, the likes of which the U.S. hasn't seen in decades. In the article, Morris makes this prediction: "It's the best-kept secret in the economics media: The United States is on the brink of a period of solid, long-term growth rivaling that of the 1950s and 1960s.

It is not a finance-driven, self-de-

structive boom, like the 2000's housing bubble. No, the new economy will be durably grounded in energy and heavy manufacturing, even though it will take several years to come to full fruition."

Things feel good right now and if Morris is right, we're in for a good ride. Not that I'm an expert, but in a <u>2009 column</u>, I did say that the fundamentals would become strong and allow for a longer, stronger recovery. It just made sense to me that if you fixed the fundamentals, the rest would take care of itself. Keep in mind that the U.S. is still the largest, strongest economy in the world. When it rights itself, things will really start to move. I'm sure of it.

#### Irrational Exuberance

Not all is rosy out there, however. The global economy faces a variety of challenges from China.

Having experienced several boom and bust cycles over the years—in the U.S., in Japan

Morris makes this prediction: "It's the best-kept secret in the economics media: The United States is on the brink of a period of solid, long-term growth rivaling that of the 1950s and 1960s.

in the '90s and with the recent European defaults—I've learned that when things get out of balance, the markets tend to seek equilibrium. The more out of balance things are, the more correction is needed. Another article from Fitch Ratings claims that China is on the verge of some dramatic "rebalancing." Published

in the Telegraph, the article, <u>Fitch</u> says China credit bubble unprec-

edented in modern world history, is a bit scary. Charlene Chu, Fitch Ratings' senior director in Beijing, said, "There is no way they can grow out of their asset problems as they did in the past. We think this will be very different from the banking crisis in the late 1990s. With credit at 200pc of GDP, the numerator is growing twice as fast as the denominator. You can't grow out of that." Chu does believe the Chinese government, with its deep reserves, can handle a potential banking crisis. They've already been trying to manage a soft landing. If you're vested in

China, read this article.

For the sake of our economies and businesses, let's hope that the Chinese are able to stay on top of this. The last thing we need is to derail this fragile recovery and take the wind out of the coming boom.

Call me an optimist, but it really is our turn for a bit of good economic news. I think we can all use a break from the struggles of the last decade and a chance to enjoy the good years ahead.

That's the way I see it. **PCB**

Ray Rasmussen is the publisher and chief editor for I-Connect007 publications. He has worked in the industry since 1978 and is the former publisher and chief editor of *CircuiTree Magazine*. Contact Rasmussen <u>here</u>.

# **Direct Image Solder Mask**

## EMP110 LDI

Carapace<sup>®</sup> EMP110 LDI is the next generation in Liquid Photoimageable Soldermask for Direct Imaging.

- Low Exposure Energy (50-80 mJcm<sup>-2</sup>) to Resolve Small Features

- Tack-free Surface During Exposure

- Fine Solder-dam Resolution (50µm, 2mil)

- Lead-free Compatible

- High Chemical Resistance to ENIG & Sn Processes

- RoHS Compliant and Halogen Free

- Non Toxic

EMP110 LDI soldermask is ideally suited for high-reliability, HDI PCB production where ultimate resolution and registration is required.

The EMP110 LDI formulation has been engineered to deliver straight sidewalls and fine solder-dam resolution over the wide range of coating thicknesses associated with screen-printed and sprayed PCBs.

Optimised radiation curing characteristics deliver high levels of through-cure at low energy levels without compromise in surface tack or chemical resistance.

www.electrapolymers.com

## **Printed Circuit Structures:** The Evolution of Printed Circuit Boards

#### by Kenneth H. Church, Harvey Tsang, Ricardo Rodriguez, Paul Defembaugh, Raymond Rumpf

nScrypt Inc., Orlando, Florida and the University of Texas at El Paso

#### Abstract

The printed circuit board is the backbone of electronics and a large number of consumer devices. The challenge to put more function in a smaller space requires more components utilizing smaller bond pads, smaller lines and tighter pitch. The electronic packaging industry has aggressively pursued novel ways to shrink and stack multilayer boards inside smaller volumes. The industry is approaching serious obstacles in the continued size reduction requirements with the need for wires, epoxy, vias, solder and sometimes bolts and screws to mount the boards. The next logical step is to move beyond 2D stacking, which is 2.5D, to make 3D packages and to utilize the third dimension directly. Eliminate the traditional 2D FR-4 board and the wires, epoxies, vias and solder and make the next-generation packages utilizing 3D: the printed circuit structure (PCS).

The PCS concept will allow passives, actives and even antennas to move out of the XY plane and into the XZ and YZ planes. This new dimension will appear to be very complex and next-generation circuit optimization will be required, but the end result will net a significant improvement in volume utilization. In addition, if new materials are developed and utilized properly, the PCS will be the box or the package, thus eliminating all the bolts and screws necessary to mount a PCB in a traditional box or package, saving space and reducing weight.

In this paper, nScrypt and the University of Texas at El Paso will present 3D printing of printed circuit structures. A demonstration of true 3D electronic structures will be demonstrated and shown as well as novel approaches that utilize CAD to 3D printing, including the electronics portion.

#### Introduction

Printed circuit boards are a critical component in almost every electronic device. Electronics come in a variety of shapes and sizes, determined by function, environment and physical shape of the device. The electronics

portion of the device is limited to a standard 2.5D approach. This implies building a multilayer board with dimensions in X and Y and then mounting that board to a structure of specific shape and volume. But data transfer speeds are seeing their limitations in this conventional PCB approach. New materials are being used to overcome these limits, but the actual structure will need to see improvements too<sup>1,2</sup>. Wires, epoxy, vias, solder and connectors all contribute parasitic harmonic effects to standard PCBs due to impedance mismatching and/or sharp turns that create electromagnetic (EM) reflections<sup>3,4</sup>. Using 3D printing, there will no longer be a need for wires, epoxy, vias, solder or bolts and screws. The 3D printing process can move from building a circuit which is flexible enough to be rolled into a cylinder, to building a cylinder with a curved circuit within it. These structures will be solid or even porous depending on the applications of the PCS. 3D printing has been around since the 1980s and started as a novel demonstration, but is now becoming more ubiquitous. With the introduction of tabletop fused deposition manufacturing (FDM), machines and even home users have the opportunity begin exploring possible 3D prints. These printers allow users to convert their CAD into physical structures for prototyping or even small part replacements<sup>5</sup>.

#### **3D Printing**

3D printing or additive manufacturing (AM) is an efficient and green form of manufacturing that fabricates products by building successive layers of material, thus creating little to no waste. Traditional subtractive techniques start with bulk materials and machine away unwanted excess. The first concept of AM known as selective laser sintering (SLS) places a thin layer of the powdered material onto a work surface and a laser beam patterns metal thin shapes by sintering the powder particles together. The work surface is lowered and a second layer of powder is spread on top of the existing metal shape. Through multiple lowering, powder spreading and sintering cycles, a 3D structure can be built with features and voids that subtractive processes cannot achieve; resolution of lines are around 0.005" and layer thickness of 0.004".

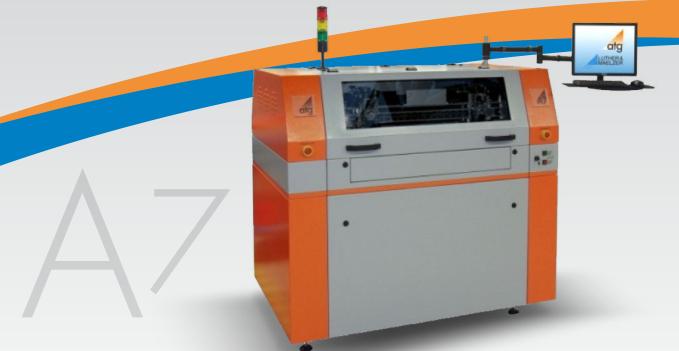

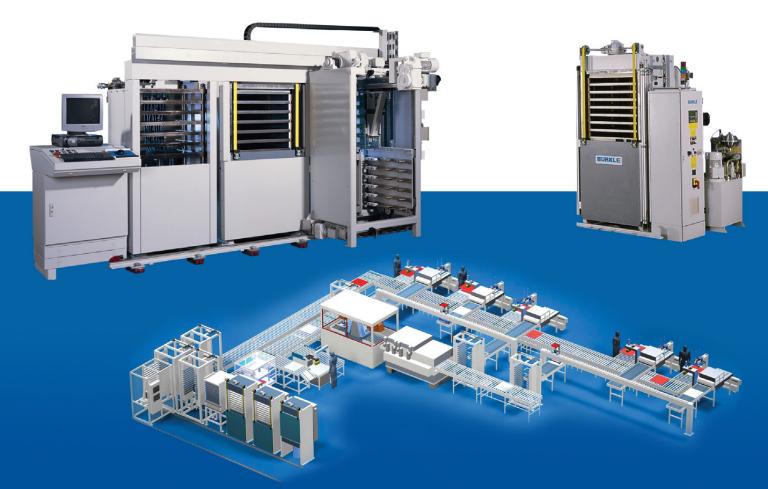

Stereolithography apparatus (SLA) is another 3D printing approach that is a similar SLS but instead of sintering powder, it hardens photosensitive resin (liquid). There are some builds that require support structure materials if there are large gaps in the 3D structure during the build. Support structure materials are temporary and typically dissolved with water. SLA, like SLS, is an expensive process given the time it takes to build a part (minutes to hours) and the photosensitive resin is very expensive. The features created are solid and the surface finishes can be smooth: feature sizes can be as small as 0.001" for commercial grade tools, but research tools have achieved 0.0001" features. Figure 1 shows commercial tools for 3D printing and direct printing.

Fused deposition manufacturing (FDM) is another 3D printing approach using a heated nozzle to extrude plastic directly onto a surface. This will print a pattern and then repeat the print, thus layering for 3D builds. Like SLA, FDM will sometimes require a support structure material during builds. The nozzle and head is moved mechanically on a motion platform and coordinated with the flow of melted plastic flow rate to the XY motion. A disadvantage of FDM is in the printing process which induces porous structures during the build. This is due to the shape of the extrusion and the fact the material is not self leveling as this would be counter to the 3D build concept. This process typically requires an 80-90% overlap of the lines to be placed into the building parameters creating

Figure 1: Commercially available SLA machine (I) and commercially available direct print machine (r).

a stable build but also small air pockets. The problem can be improved with high resolution prints and control of the overlapping parameters. This type of build imposes surface finishes that are rough and additional post-processing is sometimes needed to smooth the surfaces. This approach for 3D printing has larger features (0.005" at high resolution), but the parts produced are more rigid which allow for functional parts.

#### **Printed Electronics**

Printed electronics is a printing process that can pattern an electrical circuit onto various substrates, including cheap substrates

such as vinyl. These processes were designed to be fast, low-cost and achieve small features. The screen printing process is well known for its use in solar cell manufacturing, low temperature co-fired ceramic (LTCC) and multi-chip modules, where a screen with a set pattern is laid on top of a substrate and a thick film ink is pressed through the screen. Screen printing can achieve throughputs of 50 m<sup>2</sup>/h with a resolution of 100µm. This is standard for manufacturing in industry and has the ability to produce thick layers from a wide range of high viscosity materials.

In addition to using screens, there are direct digital manufacturing (DDM) approaches such as inkjetting. Similar to household printers, inkjets use a low viscosity ink with solvent materials which are deposited via droplets onto a substrate, line by line. These inkjettable materials can exhibit a number of electrical attributes, including conductivity. For many applications, low temperature processing is required and many of these materials contain additives to enhance adhesion to the surface after low-temperature post-processing. Inkjetting can have a throughput of around 100 m<sup>2</sup>/h with a thickness of around 0.0005".

Electroless plating is another common printing process used extensively in the production

Just like the inkjet method, aerosol printing requires custom inks that can be aerosolized, but aerosol has the widest range of working distances and line widths.

of PCBs. This process deposits a metallic film with the aid of a chemical reducing agent in solution. This allows plating of non-conducting substrates and is typically used to coat vias after drilling with copper. While electroless plating is typically slower than electrolytic plating, the resolution is better and finer, and thinner lines can be achieved. This is becoming more attractive as circuits are becoming smaller and require higher frequency performance, which require higher resolution.

Other forms of printed electronics include the direct print methods (DP), which some have coined direct write. These include nozzle, quill

and aerosol<sup>6</sup>. (The nozzle method is covered in the 3D Printed Circuit Structures section later.)

The quill method deposits material much like a quill pen on paper. The quill tip is dipped into a container of material which adheres to the tip and then the tip is moved onto a substrate where the material is transferred from the tip and onto the substrate with 3-axis movement. This method is able to produce 14 nm line widths with 5 nm spatial resolution, but only able to build small length scales and requires flat surfaces and custom inks. Inkjet printing has been covered before and

the advantages include high-speed printing due to parallelization of print heads, but these approaches typically require flat surfaces and custom inks that have low viscosities.

Just like the inkjet method, aerosol printing requires custom inks that can be aerosolized, but aerosol has the widest range of working distances and line widths. Aerosol requires the material to be atomized into a mist which is surrounded by a coaxial sheath of air flowing out of an orifice directed at the substrate; dimensions as small as 5µm have been done using this approach.

Since these are all forms of 3D printing, it is natural to combine some or all of these methods to create a complete electronic product with small feature sizes and fine conductive line

# smaller IS BFT TFR Design with ROGERS materials for smaller antennas

obile

ALS A

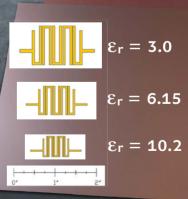

#### The Leader in HIGH Dielectric Constant Circuit Materials

In today's mobile and connected world, designers must compact increased functionality into smaller spaces. Smaller circuits are possible with highdielectric constant (high- $\varepsilon_r$ ) printed-circuit-board (PCB) materials. Rogers offers the widest variety of high- $\varepsilon_r$  PCB materials for high frequency circuit designs that simply must be made smaller.

Look to Rogers Corporation not only for PCB materials with high- $\varepsilon_r$  values, but for circuit materials with the widest range of  $\mathcal{E}_{r}$  values in the industry. Rogers' PCB materials provide circuit designers with true flexibility, not just for the electrical performance they seek, but to achieve it in the smallest-sized circuits possible.

| Product   | ٤r   | Df @ 2.5GHz |

|-----------|------|-------------|

| RO4360G2™ | 6.15 | 0.0030      |

| RO3006™   | 6.15 | 0.0018      |

| RO3010™   | 10.2 | 0.0020      |

If it's a circuit that has to be smaller. make sure it is also better, with Rogers!

ews

wifi

widths. The possibilities for enhanced performing circuitry will grow when the boundaries imposed by a 2D plane are removed.

#### **Printed Circuit Structures**

The printed circuit structure (PCS) is a new area for 3D printing. While early demonstrations were done in the early 2000s, recent studies and demonstrations are being presented as a viable alternative to traditional circuit board manufacturing. Unlike conventional PCBs that build 2D layers consecutively on top of each other (otherwise known as 2.5D), a truly 3D PCS would utilize side walls, curves and reduce unused volumes that exist in current electronic devices. A graphic artist's rendition of a true PCS is shown in Figure 2.

The idea of utilizing the structure as the circuit carrier implies there will be no need for PCBs. This reaches beyond simple conformally printing circuits and changes the structure to an electrically functional structure; the electronics are the structure. In 2D, components can only be placed on a level plane while in 3D components and traces can be built up, around and within structures. Components can be smoothly integrated into a structure and even hidden within a solid structure which makes reverse engineering much more challenging. It will also enhance the ruggedness of the device as the device will become a monolithic piece with no glue, snaps, solder, wiring or bolts. This

Figure 2: A graphic rendition of future PCS.

monolithic piece could also be water proof as the electrically workings could be buried within the structure leaving no entry point for liquid. The shapes of the structures will not restrict the printability of electronic components and traces, therefore enhanced performing devices may be possible to include higher gain antennas. Additionally, this will be most the most volumetrically optimized approach to electronic packaging, thus enabling many more functions per cubic volume. A few examples of PCS are shown in Figure 3.

But as these structures get smaller, the electromagnetic (EM) interference between traces and components become a larger problem. But with the introduction of anisotropic materials and spatially variant lattices, it would be possible to manipulate fields around and directed towards other components to achieve complex structures that perform in ways that 2D structures cannot<sup>7,8</sup>. Current research demonstrates that 3D structures can manipulate

Figures 3a-c: 3D printed dice and charger (a), 3D printed magnetometer (b) and 3D printed accelerometer (c).

Figure 4: Metal components with dielectric field management equals complex functional structures.

fields using meta material designs in ways that standard 2.5D structures cannot. Figure 4 is an artist rendition of designing material properties in 3D, thus providing control over EM fields. This will be an enabling technology as more and more functions are packed into smaller volumes.

Unfortunately, PCS building methods are still premature and are labor-intensive since automation has not yet been achieved. Currently, 3D printing and DP are used in succession to achieve such results, but a tool which can combine these two methods with the same resolution as DP would require a new definition. A direct printing additive manufacturing system (DPAM) is being developed to obtain the build and curing of such structures within one automated tool.

#### **Automation Within a Single Tool**

The primary strength of the nScrypt 3Dn-600HPx DPAM system lies in its many integrated tools. Rather than performing only one function and requiring operators or conveyors to move parts from system to system, time is saved by being able to perform all functions in just one machine on one gantry. Future, larger 3D electronic printing systems may use conveyors connecting several dedicated machines; however, for low-volume experimental fabrication, the compact nature of a single, integrated system is easily seen. An additional advantage is that because the part never moves from start to finish, less alignment fiducially is required, thus easing the realization of high accuracy printing.

Here is a list of hardware that the DPAM tool is equipped with:

- Precise 3D Cartesian gantry allowing all tools to reach any point in a 600 mm x 600 mm area

- Four independent precision valve dispensing pumps

- 650 nm laser displacement sensor

- 12.4W/cm2 (3 mm beam diameter) 385 nm UV LED lamp

- 30-watt CW or pulsed (150 ns) 1080 nm laser

- Rotating vacuum pick-and-place nozzle and 7-bay tool changer

- 18" square milled-flat porous ceramic vacuum chuck

- Motorized dual camera Ethernet-based machine vision multi-tool automatic calibration system embedded below the printing deck

- Ethernet-based machine vision camera with automatic computer vision and recognition software

- Motorized process-view camera

Here are a few possible applications for these tools, arranged in a hypothetical order of operations. Each of the concepts has been successfully demonstrated.

1. Place either plastic sheet on vacuum chuck or remove vacuum chuck and place an arbitrary part in printing area as the printing substrate

2. Scan the object contours using the laser displacement sensor for conformal printing on the substrate. A 3D scan file is produced and used to accurately print on the arbitrarily-contoured part

3. The machine camera using image recognition software automatically identifies markers fiducially and adjusts and rotates the design files to match the actual substrate or to orient and accurately place components using the pick-and-place system

4. Using one of the four dispensing pumps, layer-by-layer print UV-curable dielectric/structural material such as the photopolymer used in SLA equipment

5. Between layers of photopolymer, use the 385 nm UV lamp to cure the dispensed material

6. Pick-and-place surface mount components into photopolymer structure

7. Another pump dispenses thick film, micro-silver flake conductive traces to form electrical interconnects. A second laser displacement sensor scan may be used in order to print nonflat interconnects

8. Thermally cure the thick-film ink using the high power 1080 nm laser

9. Continue process of printing structure, conductor, curing, and placing components until a finished 3D structural electronic part is formed

#### Process Integration, Synchronization, and Control Hardware

Each of the integrated tool technologies is centrally-controlled by the precise motion control platform. The motion control platform is connected via IEEE 1394 serial bus to the PC. The motion control platform uses multi-axis synchronous motion in order to print along arbitrary 3D paths as is needed in the case of following the contours measured by the laser displacement sensor. From the

same control system are many digital, analog, and serial inputs and outputs connected to each of the subsystems such as the UV light, pickand-place, etc. In this manner, complete integration of machine operations is easily achieved because the hardware operations of each device are directly controlled from the central motion control platform. Each device does, however, have some type of interface electronics so that the complexities of each device's control are

Using this method with the excellent hardware motion control system allows accuracies of better than 1 micron to be realized.

masked from the central motion control platform. In the case of the laser, for instance, an RS-232 serial port and a set of digital IO lines are used to set the optical power and operation mode of the laser. Each of these signals is adapted by electronics within the laser control box to control the actual laser diode. In the case of the pick-and-place system, digital output modules convert 5V signals from the motion control platform to control pneumatic solenoids for pick-and-place vacuum, up/down actuation, and tool changer operation. Each of the tools is controlled in a similar manner.

From a software perspective, designs start as 2D layer drawings in the DXF file format such as slice files generated from 3D model files in STL format. Each of these layers is called a job and are arranged as an ordered list of separate tasks called a job tree, which the machine executes when the run button is clicked. Each job has particular attributes such as which tool is to be used (pump, UV light, laser, etc.) as well

as more advanced settings such as 3D laser displacement sensor scan data in order to print conformal to the actual measured surface. Within each job, a text-based script file is provided which contains the motion commands as well as custom commands such as "light on/off" or "pick/place" which control each specialized tool. In order to achieve smooth, accurate, and perfectly synchronized operations, each of the jobs is precompiled into a single program code file which is first downloaded to the precise motion control hardware from the computer running a real-

time kernel (RTX) via IEE 1394 serial bus before execution begins. Using this method with the excellent hardware motion control system allows accuracies of better than 1 micron to be realized.

#### Operation

From a user's perspective, the entire system is controlled from a Windows PC running proprietary software. Designers start with a 3D

#### FROM THE WORLD'S LEADING CAM & ENGINEERING SOFTWARE VENDOR

# Impedance Field Solver

- Calculate impedance for multiple PCB structures

- True field solver for crosshatch reference layers

- Use the same proven solver engine used by board designers

- Speed up automatic stackup in InPlan<sup>®</sup>

Powered by Mentor Graphics HyperLynx<sup>®</sup> technology, InSolver<sup>®</sup> is a cost-effective PCB impedance field solver that is available both as a standalone application for engineers, QA and sales, and as an embedded impedance solver in Frontline's industry-leading Engineering solutions.

#### To sign up for a free six-month trial, contact your regional Sales Representative: **ODB**+

North America Tel: 617-480-8208 ben.guarles@orbotech.com

r-Impedance Solver Calculation

Search : Diff [13 M ...el

Diff Coated Microstrip 2B

Diff Uncoated Micros

**NEW**

Crosshatch

Support

+

Diff Upper Embedded

Help

er Models

Single En

Differentiz Coplanar St Differential Cop

Diff

> Pacific Region Tel: (852)-2827-6688 pierce.weng@orbotech.com

Japan Tel: (81)-3-3280-3878 koichi.uchida@orbotech.com

claudio.bellistri@orbotech.com www.frontline-pcb.com

Europe

Tel: (32)-2-727-4863

Intelligent &

data

manufacturable

nSolve

স

www.orbotech.com

**In**Plan<mark>Flex</mark>

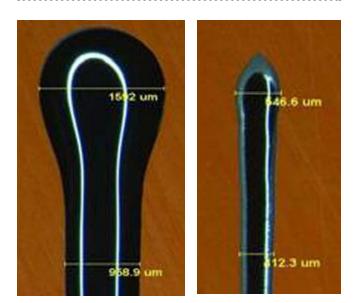

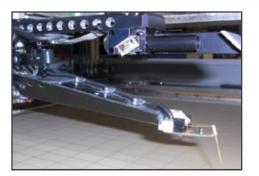

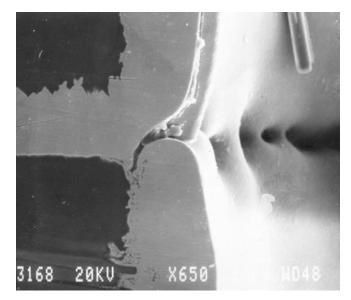

Figure 5: Cross section of printing tip.

modeling software; then, each surface mount component is modeled in 3D and each conductive trace is drawn. The structure of the part is also modeled around the components and traces. The structural or dielectric components (analogous to the FR-4 PCB substrate) are sliced and a set of 2D layer files are produced. Conductive areas are also converted to 2D files. The positions of each component to be pick-andplaced are measured and saved to a pick-andplace file. The resulting set of design files are then imported into the proprietary software as individual jobs and the specifics of each job are assigned, such as whether the given job will be a conductive trace or a layer of structural material. Added to this are jobs which perform 3D laser displacement scans of the part that will be used to modify the exact printing height of each print job or execute automated recognition fiducially. Once all the design files have been imported into configured jobs, the set of jobs, called a project, constitutes a fully automated 3D printing program code which can be run over and over at the touch of a button.

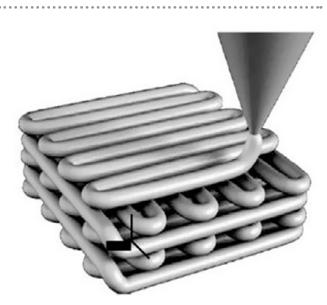

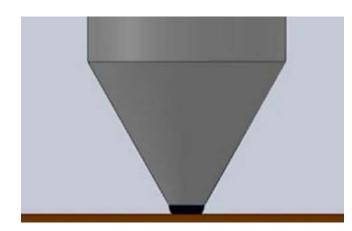

## 3D Printed Circuit Structures using a 3D Layering Process

Building three dimensional objects through a DPAM nozzle process is done through the deposition of layers in a process known as layering. Similar to stacking pages of papers to form a pile, a nozzle (or pen tip) dispenses material at a certain thickness (in the Z direction) onto an initial substrate, then, repeating the process, creates a 3D object. Each layer is deposited on top of the previous layer in a continuous, serpentine fill pattern. Figure 6 below is an artist's rendition of the direct print layering process.

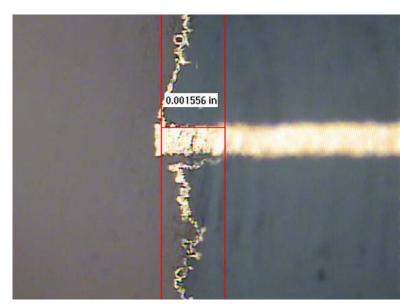

The pitch between the dispensed lines is a critical factor in how successful a build is. It determines not only the volume of the objects, but the surface finish of the print surface of the subsequent layer. Maintaining a constant layer thickness ensures that each layer is consistent and thus the reliability of the build. Little variation in layer thickness cuts down the overall build time by omitting an intermediate step for measuring the exact layer thickness. The thickness of each layer is primarily controlled by the space (or dispense gap) between the pen tip and the surface it is dispensing on. Several dispense parameters (see the 3D Build Optimization section) can be tuned to allow for different thicknesses; however, these are governed by the physical characteristics of the material itself (i.e., viscosity, particle size, thixotropic or Newtonian, etc.). Consideration of the large spacing between lines can lead to material not adhering in the following layer, thus causing the build to fail. Lines that are overlapping produce an irregular, non-flat surface. This can lead to an uneven amount of material deposition in the

Figure 6: Example of building a three dimensional object through a direct print layering process<sup>6</sup>.

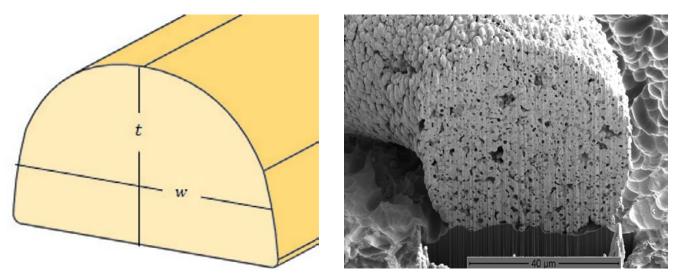

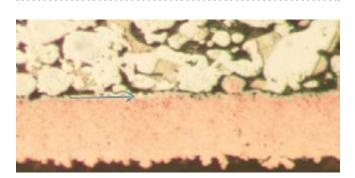

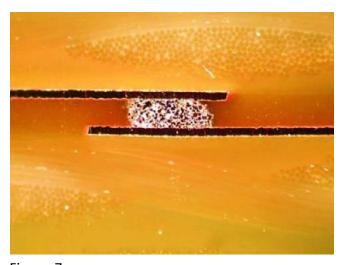

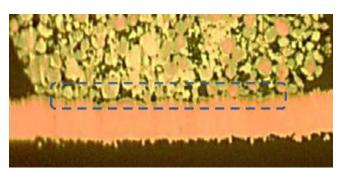

Figures 7a and b: Graphic of a cross-section of a printed line showing dimensions (a) and a directly printed line of silver on silicon cross sectioned (b).

superstrate. The consistency of lines deposited lines can be studied by measuring their width (w) and thickness (t) as shown in Figure 11.

#### **Optimizing the Printing Process**

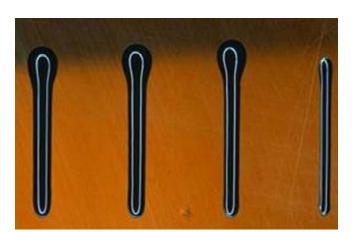

A process that can employ the dispensing of multiple materials is essential to characterize and study how these materials will behave during the process. The current DPAM nozzle technology has several different parameters that can be adjusted for optimal dispense control. A side-by-side comparison of controlled and uncontrolled resistive paste is shown in Figure 8.

The large, circular blob seen in the Figure 8a that was made at the beginning of the print is caused by improper settings of the different print parameters. In this particular case the dispensing pump was set to dwell on the start for too long (on the scale of milliseconds). In this case, the gantry system was idle during the valve opening sequence; hence, material would flow out of the pen tip, accumulating around the sides. Another issue is the steady state or continuous print condition which can cause the line to be much wider than intended. By drastically decreasing the dwell time and increasing the print speed, the line from Figure 8a was able to be narrowed and made into a much more uniform shape, as shown in Figure 8b.

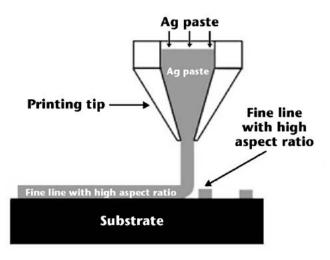

Determining the dimension of the nozzle tip, also known as the pen tip, is the first step

when designing a process to build an object. As previously mentioned, a material's dispensed dimensions can be affected by the size of the pen tip, the material composition of the pen tip and the material being dispensed. The surface energy of the substrate must overcome that of the pen tip's orifice in order for the material to release from the pen tip and adhere to the substrate. Additionally, there is a pressure from the pump that will add an additional force down-

Figures 8a and b: Uncontrolled material dispense (a) and controlled material dispense (b).

ward and away from the pen tip. Combined, these two forces will provide continuous flow that will force the material to release from the pen tip and onto the substrate. Maximum accuracy is achieved when the pen tip is kept close to the substrate (less than 1 mm) so that material will lie down onto the surface. The outer diameter of the pen tip (OD) will dictate the width of the printed line given the surface tension drawn to the pen tip. If the print parameters are set accordingly, then only the bottom surface of the pen tip should come into contact with the pen tip before being applied onto the substrate and subsequent superstrates.

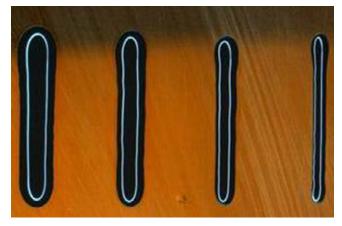

The inner diameter of a pen tip restricts a material's ability to flow. Depending on the distribution and particle size within the material carrier, the material can be made to flow reliably during a printing process. Typically the bulk of the material's particle size is onetenth the size of the pen tip's inner diameter for consistent flow, d<sup>3,4,9,10</sup>. For "large gap" applications, the inner diameter (ID) of the pen tip will determine the width of the line. This is because the bottom surface of the pen tip is no longer in contact with material being dispensed. However, the flow rate of the material through the pen tip must be high enough so that it forces material away from the pen tip and breaks the surface tension that can be created from the outer edges thus forming good adhesion to the surface of the substrate. The flow rate can be controlled by the valve displacement, essentially restricting material from flowing out of the pen tip. A larger displacement increases the volume of material flowing while a smaller displacement restricts and decreases the volume of material flowing. The rate of valve displacement can also contribute to the control of the material dispensing process. Higher speeds of valve movement cause the initial shear force on the interface of material and valve to be high. This transient mechanism can cause an accelerated flow rate out of the pen tip which yields less control on the initial dispense of material. However, this parameter is critical for low viscosity and thixotropic materials. Figure 14 shows four lines dispensed while only increasing the valve displacement by 100 µm from right to left.

Restricting how much material can flow through the opening between the seal of the valve and inner chamber of the dispensing pump can help control how much volume is displaced within the printing system. However, the rate at which the material is actually displaced is dependent on the amount of back pressure that is applied to the material. Figure 11 shows pressure being decreased from 45psi to 15psi (left to right) while all other parameters are kept constant.

It is evident that increasing pressure will cause more material to flow out of the pen tip. The print speed, or the speed at which the dispensing pump moves while dispensing, was kept constant thus material flow rate is much

Figure 9: Dispensing pen tip with optimized print parameters.

Figure 10: Material study of only varying valve opening. Rightmost line is smallest opening.

## Panasonic

# PCB Materials The New Standards High Speed & Low loss High Reliability

**Contact us**

industrial.panasonic.com/em

Partnering to go beyond.

Electronic Materials Panasonic Corporation

Figure 11: Material study by only decreasing pressure.

greater than what was minimally necessary for the material to adhere to a given substrate. Closely matching the print speed to the material's flow rate optimizes the line dimension, thus controlling the material dispensed. This becomes paramount when trying to build 3D objects with DPAM because it prevents excess or unwanted material from interfering with adjacent lines. Lines that overlap in a patterned layer while building a 3D object will lead to a greater surface roughness and cause subsequent layers to also be uneven.

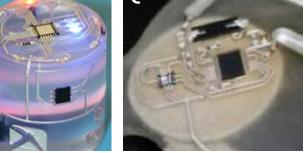

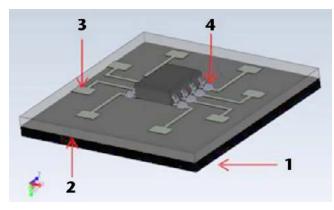

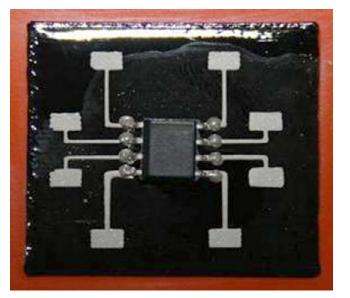

#### **Printed Circuit Structure Demonstration**

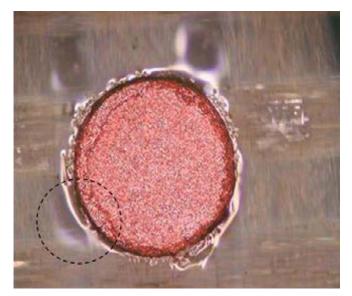

The DPAM tool is equipped with a pick-andplace system consisting of an actuating head, components rack, multi-vacuum head changer, and fiducial camera. The TL555 integrated circuit timer's (IC) pins are 1.27 mm long and 0.5 mm wide and the traces are designed to be just as wide (pen tip with an OD of 400  $\mu$ m) to better facilitate the placement of component. The substrate is a carbon composite of nanotubes (CNT) with a superstrate layer of SLA material. Silver conductive traces are DPAM printed on top before components are placed on top. The IC is adhered to the printed traces with a silver adhesive.

The entire part is built in one process with no need for fiducial points to be taken. However, the component rack's individual slots were designed to be slightly larger than the component in order for components to be manually

Figure 12: IC test circuit. CNT composite (1); SLA material (2); silver conductive paste (3); silver adhesive (4).

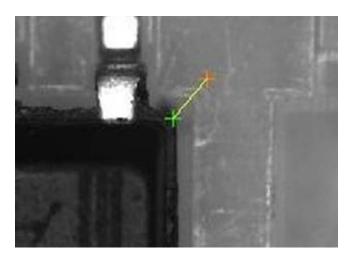

inserted into the slot. This creates a situation where the component is not guaranteed to be sitting straight in the rack. It was corrected by the image recognition camera fiducially. From the center of the slot where the component sits, the camera goes over to the two points specified and shows the location of where they are meant to be. The user is then prompted with an image of a where the system recognizes the fiducial points. If incorrect, the user can indicate where the correct fiducial point is located. Figure 13 shows a picture of the proprietary fiducial image recognition interface and how

Figure 13: The orange marker indicates the coordinates of registered fiducial point; the green marker indicates the user correction.

Figures 14a and 14b: Completed test circuits built with DPAM process. Flat surface (a) and curved surface (b).

it allows for human intervention to correct for the component's position.

This system can correct for translation and rotation. These transformations ensure the vacuum head will grab the IC perfectly in the center. The angle computed is used to rotate the actuating vacuum head to the misplacement, enabling the component to be accurately placed.

The actuating vacuum arm has a threshold pressure sensor that sends an electronic signal to the tool when it has detected that the vacuum has been plugged. This allows the system to know whether it has created a sufficient amount of suction to lift the component. The suction head is brought down to a height in the Z direction until the suction threshold sensor is set off. The component is then lifted and the suction head, which was homed before it made its descent, is rotated by the angle calculated from the fiducial correction process.

The distance between the center of the traces and the IC's location on the component rack is computed for the IC to be placed. The laser displacement sensor is used to find the distance from the suction head to the surface where the component is to be place. The IC is 1.75 mm tall from where the leads touch the surface to the top of the packaging. This distance was subtracted to the reading from the laser displacement sensor to calculate the distance to travel to place the component. After the component has been successfully placed, the suction head is actuated and a dispensing pump pre-loaded with silver adhesive is brought over to the IC's pins. Material is dispensed for 500ms to ensure enough material is deposited for contact to be made between the conductive traces and the pins of the IC.

#### Conclusion

DPAM is able to combine 3D printing's structures with printed electronics' functionality at the resolution of DP. But it is still early, requiring labor intensive procedures that take time to produce the desired products and the desired automation that current 3D printers have achieved. While 3D printing has been around for more than three decades, DPAM has been around for less than one. The future of PCB will be heterogeneous printing thus enabling a new generation of electronic packaging. Future work for this will be in material research to functionally load materials for specific mechanical and electrical properties that promote 3D building. Additionally, new processes will be important to achieve proper features during printing; surface roughness or excess voids will need to be controlled. The DPAM process has not been fully studied nor optimized and this will be important.

#### Acknowledgments

The authors would like to thank Raymond Rumpf and Eric MacDonald of the University of Texas at El Paso for their technical contribution to this industry and their photos for this manuscript. In addition, the authors would also like to thank Xudong Chen of nScrypt, Inc. for his contribution to this industry and his photos for this article. Also, thank you to Alex Morgan from the University of Dayton for carbon loaded UV curable materials. **PCB**

This paper was originally published in the proceedings of the 2013 IPC APEX EXPO.

#### References

1. Sanny He, Zhang, E,Jeng-I Chen. <u>New Hal-ogen free & Low Loss Material for High Frequen-cy PCB Application</u>,

Microsystems, Packaging, Assembly & Circuits Technology Conference, 2008.

2. Miller, P. <u>A Tale of Four Substrates—EMI</u> and Thermal Comparisons of Different PCB Materials, 10th International Conference on Electromagnetic Compatibility, 1997.

3. Rivera-Ramos, A.R., Jimenez, M. <u>Analytical</u> <u>Models for Estimating Parasitic Components in</u> <u>Power Electronics PCBs</u>, 48th Midwest Symposium on Circuits and Systems, 2005. 4. Qiu Tang, Yaonan Wang, C. Christopoulos. Simulation and Research of the PCB Vias Effects, Third International Conference on Natural Computation, 2007.

5. J. Jainschigg. <u>Just Build It: 3D Fabrication</u> <u>for Every Budget</u>, Smarter Technology, 22 Nov. 2010.

6. Ian Gibson, David Rosen, Brent Stucker. "Additive Manufacturing Technologies: Rapid Prototyping to Direct Digital Manufacturing," Springer, New York, Chapter 4, pp 72 – 74.

7. Raymond C. Rumpf, Javier Pazos, Cesar R. Garcia, Luis Ocha and Ryan Wicker. "3D Printed Spatially Variant All-Dielectric Metamaterials," Submitted to Phys. Rev. Oct. 2012.

8. C. R. Garcia, J. Correa, D.Espalin, J. H. Barton, R. C. Rumpf, R. Wicker, and V. Gonzalez, <u>3D</u> <u>Printing of Anisotropic Metamaterials</u>, Progress In Electromagnetics Research Letters, Vol. 34, 75-82, 2012.

9. Diane Burgess, Eric Duffy, Frank Etzler, Anthony Hickey, "Particle Size Analysis: AAPS Workshop Report," The AAPS Journal, Vol. 6, No.3, Article 20, September 2004.

10. ISO 9276-2:2001: Representation of Results of Particle Size Analysis—Part 2: Calculation of Average Particle Sizes/ Diameters and Moments from Particle Size Distributions.

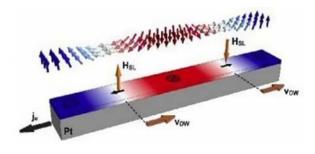

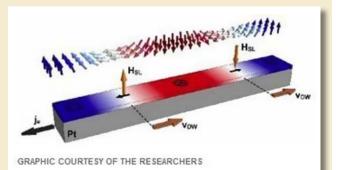

### New Magnetic Phenomenon Leads to Better Data Storage

A magnetic phenomenon newly discovered by MIT researchers could lead to much faster, denser and more energy-efficient chips for memory and computation.

The findings, reported in the journal Nature Materials, could reduce the energy needed to store and retrieve one bit of data by a factor of 10,000, says the paper's senior author, Geoffrey Beach, an assistant professor of materials science and engineering at MIT. The paper's co-authors are graduate students Satoru Emori and Uwe Bauer, post-doc Sung-Min Ahn, and Eduardo Martinez of the University of Salamanca, Spain. Beach says that hints of the new phenomenon have been reported for several years, but these had remained unexplained until now. "The new results could overcome a lot of what had seemed like fundamental limitations," in the control and use of magnetic materials. "It's a whole new approach to the design of magnetic materials."

## The Very Best in PCB Manufacturing Supplies

| Panasonic                                                                                                                     | Multilayer Laminates & Flex          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| Laminate R-5775 Prepres R4500                                                                                                 | Dk = 3.6 (1GHz) Df = 0.002 (1 GHz)   |  |  |

| Laminate R-5725 Prepreg R-5620                                                                                                | Dk = 3.8 (1GHz) Df = 0.005 (1 GHz)   |  |  |

| Halogen-free<br>MEGTRON2                                                                                                      | Dk = 4.1 (1GHz) Df = 0.010 (1 GHz)   |  |  |

| High Reliability Glass Epoxy Multi-layer Materials                                                                            | Tg (DSC) 173 C Td = 350 C            |  |  |

| Flexible Printed Circuit Board Materials<br><b>FECTORS</b><br>R-F775 (Polymide base film type)<br>R-F705 (ICP base film type) | Thk: 12-100μ Cu: 2-18μ ED, 18-70μ RA |  |  |

| Drills and Routers                                                                                                            |                                      |  |  |

| Standard & Undercut<br>Anti-fracture Routers<br>Diamond Cut Routers<br>Chipbreakers                                           |                                      |  |  |

| <b>USA</b> : 301 West Dyer Road, Suite "E", Santa Ana, CA, 92707 Tel: 714-825-0404 Fax: 714-825-0406                          |                                      |  |  |

Canada: 1124 Midway Blvd., Mississauga, Ontario, L5T 2C1 Tel: 800-668-5447 Fax: 905-670-8420

www.matrixusa.us

## **Pricing and the Technology Life Cycle**

#### **by Bill Burr and Nick Pearne** BPA CONSULTING

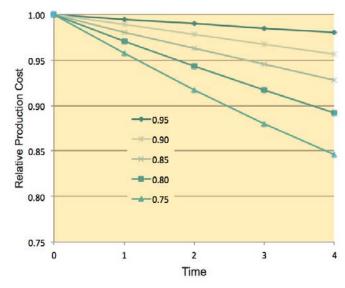

SUMMARY: Even without the distortions caused by greatly differing cost structures around the world, the economic impact of yield and efficiency improvements during the life of manufactured products and systems predicted by learning curve theory is an inevitable part of the technology life cycle.

How much is a product going to sell for next year if you've never made one before? Even without the distortions caused by greatly differing cost structures around the world, the economic impact of yield and efficiency improvements during the life of manufactured products and systems predicted by learning curve theory is an inevitable part of the technology life cycle. It can therefore be useful when developing a business/marketing strategy around an innovative product or technology to understand where pricing (and margins) may end up, particularly if the innovation has the potential to catalyze new applications and markets, implying that some sort of pricing history is nonexistent.

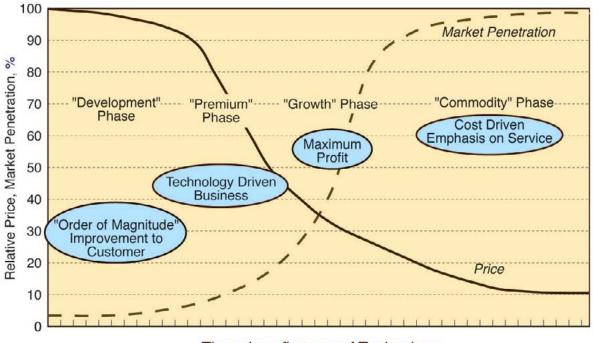

One of the problems with new technologies is the conflict that develops between proprietorship and standardization. If a technology is proprietary, single sourcing becomes an issue due to the need for supply-chain redundancy. If a technology is easily passed into the public domain, then commoditization becomes an issue with the inevitable erosion of margins and progress up the so-called "S" curve shown (Figure 1).

#### The Makings of a Winner: the 10X Factor

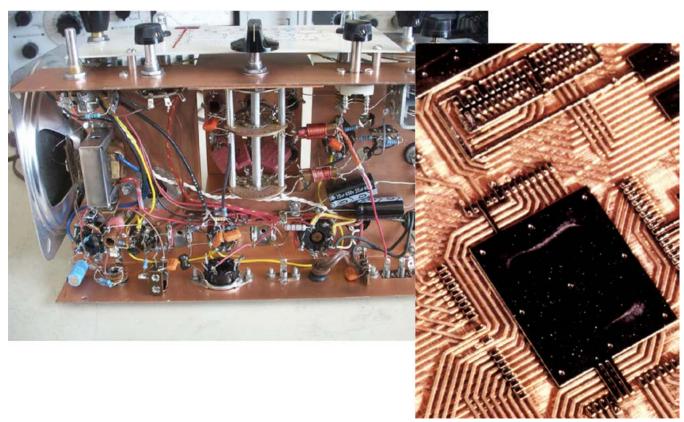

To have an impact, a completely new technology should offer an order of magnitude improvement over existing techniques—whether in cost, improved yields, manufacturing characteristics, or reliability. Something new has to be 10 times better to overturn the established order, as can be seen with, for example, the reductions in assembly time and improvements in assembly reliability and quality which occurred with the introduction of printed circuits as an alternative to hand wiring or wire-wrap (Figure 2).

### WHEREVER THE NEXT DESIGN CHALLENGE TAKES YOU, OUR LIGHT CURE TECHNOLOGY IS ALREADY THERE.

The Electronics Market continues to evolve at a faster rate than ever before. Today's complex designs, innovative materials, and increased focus on the environment can present challenges to manufacturers. Whatever demands you face, Dymax has you covered. From conformal coatings to encapsulants to edge bonding materials, we provide solvent-free, light curing technology that's truly game changing. Cost-reducing solutions that turn problems like shadowed areas, cure confirmation, and production throughput into non-issues. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. **Visit dymax.com/electronics**.

#### PRICING AND THE TECHNOLOGY LIFE CYCLE continues

Time since first use of Technology

Figure 1: The technology S curve.

Figure 2: Printed circuits—a 10X improvement.

This level of improvement generally represents a significant margin opportunity. However, as a technology progresses up the S curve and demand grows, with very few exceptions, the early adopters and developers are generally unable to keep up: A developmental business model does not scale easily and experimentation is not compatible with on-time delivery performance. The technology is licensed or otherwise transferred to the public domain, and, as in the case with printed circuits, the transfer of the technology content inherent in materials, chemistry, and processes to specialised companies means the role of the printed circuit manufacturer becomes that of a transformer-of the customer's designs into printed circuit boards, and of a translator-of the customer's interconnection needs into specifications guiding the development of materials and processes to meet those needs. The result of this process is an inevitable erosion of margins.

#### Recombinational Opportunities: Regaining the High Ground

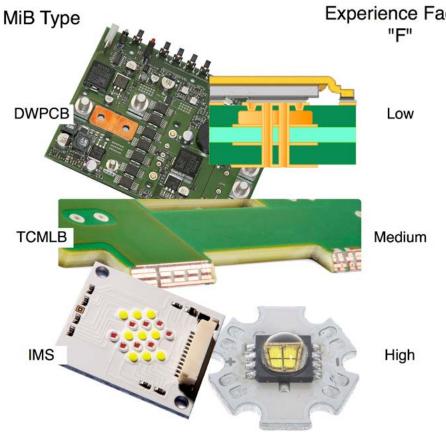

Despite the commodity aspects of the business, the position of the printed circuit manufacturer offers several advantages when the evolution of semiconductor technology or package types offer "recombinational" opportunitiesinterconnection and/or power management challenges can be met by recombining standard building blocks within the board. Such a situation is occurring now in the field of digital power. BPA's just-released report "Metal in the Board—Opportunities for Substrates Providing Enhanced Thermal and Power Management," details the dynamic markets and new applications becoming possible by the shift to surface mounted power devices and the rapid improvements in LED efficacies according to Haitz' Law. These opportunities are being met by a range

of solutions, many of which are coming from the printed circuit manufacturers themselves as existing building blocks are recombined to provide low resistance thermal and electrical pathways in the board, such as those shown in Figure 3.

These recombinational solutions represent either specialized materials, advanced process know-how, or some degree of proprietorship. Depending on the width of the "moat" (the barrier to entry made up of know-how, engineering, and proprietorship) and the value recaptured by the technology (external functions it replaces, such as heatsinks, busbars, cabling, connectors, daughterboards, etc.), there is a window where development overheads can be recovered thanks to improved margins. But sooner or later, the transformation process and associated margins will fall under the iron fist of learning curve theory, even for what appear to be highly complex technologies.

#### **Knowledge is Power**

Most manufacturing people don't care for learning curve theory because it looks like a systematic approach to leaving money on the table. The learning curve pricing practices adopted in the '50s and '60s by major players in the budding U.S. semiconductor industry were more responsible than any other single factor for the financial erosion of the world semiconductor and consumer electronics industries. Billions of dollars in potential profits were sacrificed by pricing from learning curve forecasts to obtain market share, instilling along the way an expectation of dramatic reductions in cost per function. This "buy your way in" approach is consistent with the essentially infinite market demand for digital information processing. However one of the findings of BPA's MiB research is that certain applications, most notably

Figure 3: Innovation at work: MiB "DWPCB" type. (source: Häusermann GmbH)

solid state lighting, don't necessarily represent endless opportunity.

Yet, there are many applications in which the learning curve approach has real use because, like it or not, in a competitive market environment and for a wide range of processes, there is always at least a tendency for costs to follow its laws. An understanding of this process can provide a competitive edge in bringing new technologies to market.

The learning curve applies in some degree to any process or class of processes in which costs are susceptible to reduction by manufacturing experience, for example:

- Better tooling methods are developed and used

- Productivity is increased as equipment, processes, and, where needed, materials are evolved

- Design flaws are detected and corrected

- Engineering changes decrease over time

- Yields improve, reducing rework/recut and associated scheduling/setup issues

The degree of fit tends to be excellent for long-running processes with low material content and high added value such as making widgets, turbine blades or spark plugs. It is probably the worst for processes with extreme and uncontrolled variability. Printed circuit and particularly multilayer processes are certainly somewhere in the spectrum: The steady erosion of prices that has occurred over time suggests that both experience and market growth are, in fact, having an effect on cost and therefore on pricing. If such a trend is now in effect, there is no reason to expect that it will not continue into the future, therefore learning curve and market growth relationships might be used for MiB and other new technologies to look ahead at least in a qualitative way.

#### **Learning Curve Analysis**

#### The Cost vs. Quantity Relationship

As mentioned earlier, the learning curve depends on the fact that experience gained from increased production of any commodity causes a decline in manufacturing costs, and therefore inevitably in prices in a competitive market environment. More exactly, the theory states that every time the quantity of units (or lots) produced is doubled, the corresponding unit (or lot) costs decline by an experience factor F, also known as the learning or improvement ratio. This is determined by the relationship between resources (typically process cost) required to produce double the reference quantity,  $Q_0$ :

$$\mathbf{F} = \mathbf{C}_2 / \mathbf{C}_1 \tag{1}$$

where  $C_1$  is the initial average unit cost and  $C_2$  is the average unit cost for double the reference quantity. From (1) it is evident that the higher the value of F, the less change in cost is to be expected due either to process maturity or highly customized content as might be expected from build-to-order machine tools. It is also important to note that the term "experience factor" does not refer to the actual experience a given vendor may have in the manufacturing of the product. The term relates to the degree of maturity of the process (i.e., the headroom that still exists for cost reduction through automation, enhanced material sets, tooling modifications, and so forth).

For an initial quantity  $Q_o$  and a final quantity Q, the number of "doublings" or fractions thereof for the total quantity produced is given by  $\log(Q/Q_o)/\log(2)$ . Therefore the unit cost behavior as a function of quantity can be written as:

$$C = C_1^{*}(F/100)^{(\log(Q/Q_0)/\log(2))}$$

(2a)

where C is the unit cost after quantity Q units or lots,  $C_1$  is the first unit cost, and F is the experience factor in percent: a value of 75 for F would be typical of very steep (fast) learning curves, in which process consolidation proceeds rapidly with corresponding reductions in changeover time, improvements in yields, etc.

Equation (2a) is awkward to handle since the principal variable, Q, appears in the exponent. It can be rearranged (and simplified) by noting that in general  $a^{\log(b)}$  is equivalent to  $b^{\log(a)}$  since either expression can be writ-

#### PCB Quality Assurance Solutions, tailored to your individual needs

At Gardien, we understand the importance of ensuring the PCBs at the heart of today's electrical products meet the highest standards of quality assurance, giving businesses and consumers peace of mind.

Gardien flexible solutions are trusted by leading high-tech manufacturers worldwide, serving the aerospace, medical, defence, computer, automotive, telecommunications and industrial markets.

From independent small batch testing to fully integrated quality assurance facilities, we have a solution for you.

Find out how we can help you today

<u>Gardien</u> Group

www.gardien.com · info.group@gardien.com

CANADA • CHINA • GERMANY • JAPAN • SINGAPORE • TAIWAN • USA

ten as e^[log(a)\*log(b)]. An alternate and better form for (2a) is therefore

$$C = C_1 * q^k$$

(2b)

where  $q = Q/Q_0$  and  $k = \log(F/100)/\log(2)$ .

The total cost, T, to produce a quantity Q units or lots can be obtained by integrating eq. (2b) over the limits q = 0 to q = Q:

$$T = C_1^* \int q^k dq = C_1^* Q^k (k+1)/(k+1)$$

(3)

The average cost, A, per unit or lot quantity is the total cost divided by the quantity:

$$A = T/Q \tag{4}$$

For processes where the experience factor is accurately known, the average cost is often used to quote a lot or piece price to be effective over the entire production.

Suppose, for example, that a first lot of 10 pieces is produced at a cost of \$20.00 by a process with a known experience factor of 80%. What would be the predicted piece cost for 1000 units?

For F = 80%, k is found to be log(.80)/log(2)= -.3219, and for this case the experience quantity Q = 1000/10 = 100. Therefore,

$C = 20.00*100^{(-.3219)} = 4.5412$

so that at the end of the run the production cost has declined to \$4.54 per lot. The total cost, from eq. (3) becomes:

$T = 20*100^{(.6781)}/.6781 = 669.7274.$

The average production cost per unit quantity (1 lot) is therefore T/Q =\$6.70 and the piece cost is about \$0.67.

This approach can be used to create loglog plots for various experience factors, giving unit costs as a function of quantities and initial costs. For example, a process with 80% experience factor and an initial cost of 1.00 per unit can expect unit costs to decline to about 0.11 by the time 1024 (2^10) units have been produced. This not atypical of the semiconductor industry, where F may be 75% or even less. At the other end of the scale a complex, low volume product may be 90 or even 95%.

#### New Technologies: The Experience Factor

To use this analysis for new technologies, it is necessary to determine the experience factor. This can done using a broader experience base than the simple doubling shown in equation (1) by flipping equation (2a) around, provided the data are available. Specifically:

$$F = 10^{(\log(2))} \log(C/C_1) / \log(Q))$$

(5)

If the production cost of an MiB type IMS LED multichip substrate was 2.00 when 10,000 pieces had been produced ( $C_1$ ) and the cost (C) is now 0.65 when 4,000,000 have been produced (Q=400), what is the experience factor F?

$$F = 10^{(\log(2)*\log(0.65/2.00)/\log(400))}$$

or

$$F = 0.878$$

What will be the cost for the 20,000,000th piece when Q will be effectively 2000 (20,000,000/10,000)?

This example assumes a limited degree of process innovation is necessary in the introduction of a new layout for the same function/ substrate. As is often the case in printed circuit manufacturing, where the emphasis is less on products and more on capabilities built on standardized processes, the experience factor may be even higher than 88%. It is important to remember that the experience factor "F" does not imply any particular degree of expertise or mastery of the technology. It is simply an index of the expected stability of processing costs over the lifetime of the design. Innovative technologies such as the DWPCB (discrete wire) and HCPCB (embedded bus) types, where "recombinational" techniques are used that vary greatly from design to design can expect to have factors in the mid to low '80s, depending on complexity (Figure 4). This suggests that first movers will de-

## TECHNICA, U.S.A.

Supplying a Full Line of Thermal Systems in Partnership with Rehm Corporation

### Simply. More. Ideas.

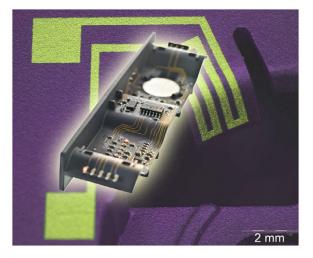

# MID and 3D - the path to growth is clear!

MID is the abbreviation for "Molded Interconnect Device." The goal of MID technology is to unite electrical and mechanical functions in a single construction unit. The circuit tracks are integrated into the housing, enabling the reduction of weight and space, and are more eco-friendly than conventional PCBs.

The technology is currently most popular in vehicle electronics and telecommunications, and the number of these components available on the market is growing markedly. As a result, MIDs are increasingly being integrated into computers, household appliances and even into medical technology.

Vapor Phase Soldering offers an exciting alternative to the intricate processes

commonly employed to create the connections between assembled components and the substrate.

The **CondensoX** condensation soldering system from Rehm offers a significant technology advantage for this process.

Click to watch the CondensoX technology video

CONTACT US FOR MORE INFORMATION

Download Condenso

Brochure

Condenso

#### www.technica.com

#### PRICING AND THE TECHNOLOGY LIFE CYCLE continues

Figure 4: Relative experience factors for MiB types. (source: Häusermann GmbH, Schweizer Electronic AG, Lumitech, BPA/commercial)

rive maximum benefits from innovation, as subsequent price movements will be steep unless offset by functional integration or other "must have" characteristics of the new technology.

#### **Integration with Market Growth**

The basic insight that can be derived through the learning curve technique is an attempt to relate expected developments in competitive pricing directly to growth in the market, since growth in the market implies increased volumes and therefore declining unit prices. This can be done by integrating what is known about the learning curve relationships into the market forecast.

Generally speaking the volume in the electronics market follows an exponential growth law. Although there is lots of noise in the fine structure of the data, as for example the effects of the dotcom implosion, the recent recession,

Experience Factor

etc., some useful trend forecasting can be done on smooth averages. An exponential growth relation is

$$S = S_0^* 10^{^{^{^{^{^{^{^{^{^{^{}}}}}}}}}} S_0^* (1+R/100)) \quad (6)$$

where S = sales volume at any time,  $S_0 =$ sales at time T = 0 (beginning of the period), and R = annualized percentage rate of growth.

BPA's forecast for the MLBTV (thermal via type) through the end of this decade gives an annualized percentage growth rate, R, of about 11%. and, if T = 0 at 2013,  $S_0$  is \$0.60 billion. By 2020 (T=7) we have S =  $.60*10^{(7*\log(1.11))}$ \$1.24 billion.

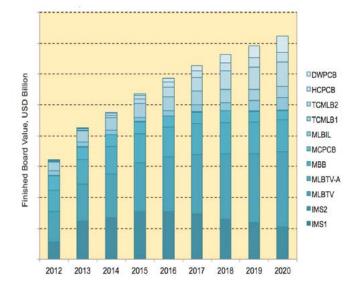

Forecast MiB type growth trajectories are shown in Figure 5. As we look out into the future with these projections it

would be useful to know what might happen to pricing for the various types as a function of time.

In a competitive market based on standardized processes with limited proprietorship prices are probably related to costs in some rational manner so that we can also think of C and  $C_1$ in equations (1) and (2) above as PRICE. This relationship can be fine-tuned considering those components within the build (such as laminates, copper, resists, etc.) which are externally sourced and therefore responsive to different cost dynamics. With this in mind we can say that for any sales volume S the corresponding quantity q must be S/C. From equation (2b) we can get

$$C = C_{1}^{*}(S/C)^{k} \text{ or}$$

$$C = (C_{1}^{*}S^{k})^{(1/(1+k))}$$

(7)

### **PRICING AND THE TECHNOLOGY LIFE CYCLE** continues

Figure 5: Forecast growth trajectories for MiB Types. (source: "Metal in the Board"; BPA Consulting)

Then we can substitute the market movement from (6) and get C as typical price (cost) behaviour as a function of time in a growing market:

$$C = (C_1^{*}(S_0^{*}10^{(T*log(1+R/100))})^{k})^{(1/(1+k))} (8)$$

This relationship is not as bad as it looks, and is easy to explore on a spreadsheet. Some results for the overall MiB market CAGR of 11% per annum are shown in Figure 6.

#### Conclusion

The measurable impact of the learning curve will be different depending on which sector of the MiB universe we're in: The trajectory of an MiB type with a high materials content such as IMS will be quite different from that of those types with higher process complexity and added value. As a consequence, the experience factor is likely to vary widely—from the high 90s for standardized IMS substrates and thermal via/MLBTV multilayers using consolidated, well characterized processes, to mid–low 80s for complex recombinational solutions such as DWPCB, HCPCB, and inlay board types. With typical 2–5-year lifetimes in a competitive marketplace, prices can be expected to drop from

Figure 6: Relative production cost as a function of time in a growing market.

7% to almost 50% of the value-added component of the board.

There is no escape from continuing and inexorable downward price pressure from entrenched expectations and trends. A clear understanding of how these work will confer a competitive advantage to the strategist concerned with bringing innovative technologies to the marketplace. **PCB**

Owner and principal of LPC Ltd, William (Bill) Burr collaborates with BPA as senior consultant, and is a past president of the EIPC and vice chairman of EFIP. He may be contacted at w.burr@bpaconsulting.com.

Nick Pearne is co-founder of BPA and the director of several companies primarily involved in technology marketing and business development. Pearne may be contacted at <u>npearne@</u> <u>bpaconsulting.com</u>.

## Building HDI Structures Using Thin Films and Low Temperature Sintering Paste

### by Catherine Shearer and James Haley, ORMET CIRCUITS INC.

Chris Hunrath, INTEGRAL TECHNOLOGY

*This paper was originally published in the proceedings of the 2013 IPC APEX EXPO.*

### Abstract

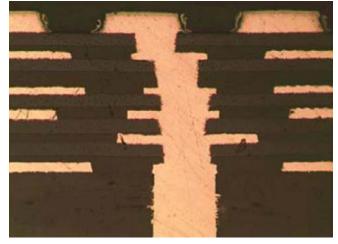

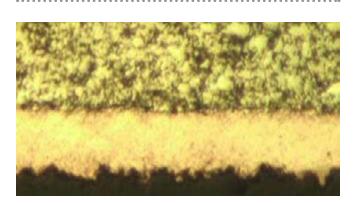

Circuit complexity and density requirements continue to push PCB fabrication capability limits. Component pitch and routing requirements are continually becoming more aggressive and difficult to achieve in good yield with current fabrication strategies. The trend is to bring the PCB closer to the density requirements required for semiconductor packaging. The ability to place interconnecting vias in any location on any layer is crucial to PCB fabricators in meeting this high density interconnect (HDI) trend.

The two fundamental elements in any type of PCB, conductors and dielectrics, both have to be considered when building "any layer" HDI. These PCBs have specific challenges for processing while maintaining thermal and electrical performance. Careful consideration of the interplay of the fundamental elements is critical to fulfilling all of these requirements.

New methods and materials designed specifically with these challenges in mind are becoming available for building HDI.

Using materials specifically designed for HDI PCBs can significantly reduce the challenges faced when producing these boards. However, along with easing the challenges of fabrication, these materials must also demonstrate the right combination of properties to meet electrical and thermal requirements while also being reliable. Validation of these new technologies is currently underway.

### Background

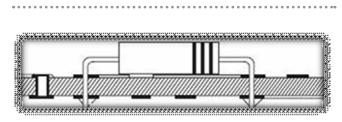

Back in the day, just taking advantage of double-sided-clad increased density. Being able to route traces in the same location on each side of the PCB, interconnected with plated through holes, added significant density compared to a single-sided PCB (Figure 1). Logically, as chips became more powerful with more I/Os, adding layers became the natural progression.

However, HDI is not just about layer count. Adding layers has a diminishing return as the through holes and vias grab valuable real estate.

Figure 1.

www.pasteDONTplate.com 949.587.3232

### Imagine all the boards you could make if process time was cut in half.

The offspring of Zeta<sup>®</sup> Bond and our wildly successful Ormet<sup>®</sup> Sintering Paste, **Zeta<sup>®</sup> Lock** produces plating-like performance as it locks in its **unique metallurgical bond** providing high electrical, thermal conductivity and adhesion to the PCB substrates *in half the process time*.

### Speed to market? Paste.

Figure 2: Sequential build-up.

Buried vias and "subs" provide an intermediate solution to higher density requirements, but these techniques greatly increase the process complexity and time in the PCB fabrication facility.

As the high density trend marched onward, build-up or sequential lamination became popular as laser drilling and better plating technology enabled blind microvias. Sequential buildup has the big density advantage of placing vias anywhere on any layer, but each layer has the process steps of an individual PCB. Lamination and plating capacity must be greatly increased to accommodate this solution (Figure 2).

There is a growing gap between cost-effective PCB manufacturing and HDI PCB requirements. New technologies—materials and methods—are needed for the industry to meet current and future demands.

#### Introduction

What if vias could be formed without plating? More importantly, what if the vias could be formed before lamination? If vias could be made this way, trips through plating and lamination can be greatly reduced. Making this possible would require the insertion of a conductor into vias in the dielectric layers between the individual circuit layers. This may be done several ways.

Some methods do this to C-stage (cured) dielectrics and some to B-stage (uncured) dielectrics. Ideally, the conductive material would be in liquid or paste form so it may be inserted into the vias after drilling, but before lamination. In applying the ink or paste, measures must be taken to ensure that the surface of the dielectric is not contaminated with conductive residue that can lead to electrical leakage, migration, etc.

Creating the interconnecting vias before lamination can greatly simplify the PCB manufacturing while still enabling via placement anywhere on any layer. In addition, formation of conductive vias prior to lamination may be combined with traditional processes for circuit formation and lamination, thus allowing the most efficient and cost-effective use of the PCB shop.

### First Element: The Conductor

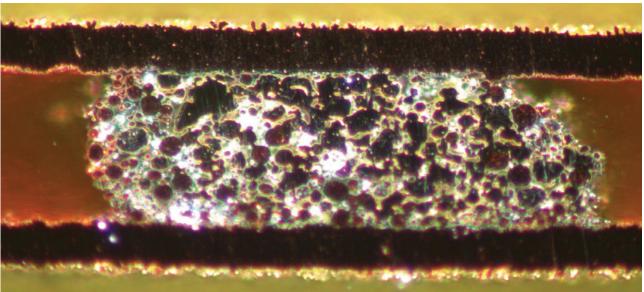

### Sintered vs. Non-Sintered

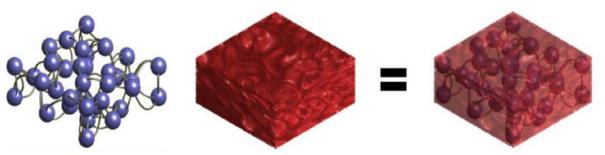

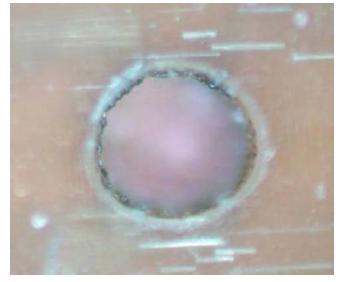

Sintering refers to a process where a mixture of particles are fused together, usually thermally. Sintering mixtures can be used for structures and dielectrics, as well as conductors.