### PCB007 PRESENTS

**RF Capacitor Material for Use in PCBs** by John Andresakis, et al.

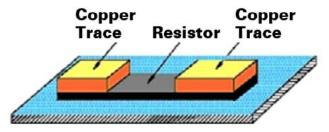

Embedded Resistors in Low Ohmic Applications

by Daniel Brandler and Manuel Herrera

**Electrical Testing of Passive Components** by Todd L. Kolmodin, et al.

# EMBEDDED COMPONENTS

**Device Embedding in PCBs: Evolution or Revolution?** by Michael Weinhold, page 16

www.mutract.com

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

Combining three events into one, IPC TechSummit focuses on innovation, reliability and leadership — three cornerstones of successful business in today's electronics marketplace.

Running parallel conferences, this world-class event will provide critical knowledge that you need to solve today's challenges and prepare for the future. Select from sessions in one conference or from all three.

Mark your calendar now to join your colleagues for this one-of-a-kind learning and networking event.

www.ipc.org/TechSummit

PCB007 PRESENTS

### **Embedded Components**

Embedded components are leading the charge this month in *The PCB Magazine,* and we've got them covered, thanks to Michael Weinhold, Oak-Mitsui, Ohmega and Secure Components.

**16 Device Embedding in PCBs: Evolution or Revolution?** *by Michael Weinhold*

### 32 RF Capacitor Material for Use in PCBs

by Jin-Hyun Hwang, John Andresakis, Ethan Feinberg, Bob Carter, Yuji Kageyama, and Fujio Kuwako

**40 Embedded Resistors in Low Ohmic Applications** by Daniel Brandler and Manuel Herrera

46 Electrical Testing of Passive Components

by Todd L. Kolmodin, Manfred Ludwig, Howard Carpenter and Rick Meraw

### "No great thing is created suddenly." -Epictetus

### No tricks: Lunaris makes current lithography virtually disappear.

Lunaris plays by a whole new set of rules. By digitizing the inner layer manufacturing processs, Lunaris eliminates 11 of 15 steps needed. Besides dramatically reducing cost and complexity, Lunaris goes from CAM to etch in just 5 minutes and 100% yield is guaranteed. It's time for a new set of rules. **It's time for Lunaris.**

www.mutracx.com

JULY 2014 VOLUME 4 NUMBER 7

THE DEFINITIVE INTERACTIVE MAGAZINE DEDICATED TO THE GLOBAL PCB INDUSTRY

PCB007 PRESENTS

thepcbmagazine.com

### ARTICLE

72 Isolation Testing and Adjacency by Rick Kaim

#### **READER RESPONSE**

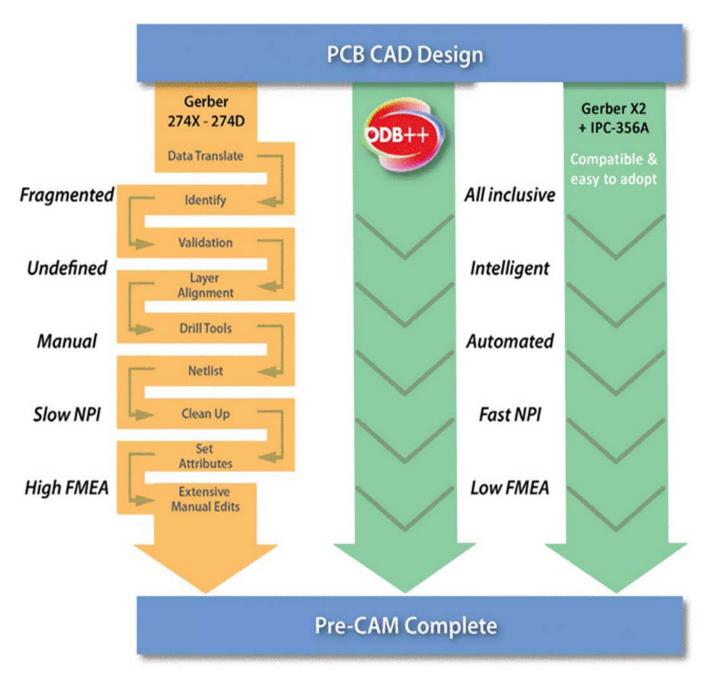

- **56 Gerber—the Smartest Way Forward** by Karel Tavernier

- 60 Julian Coates' Rebuttal

### COLUMNS

- 8 Electronic Assembly with Solder: an Unblinking Look at "The Devil We Know" by Joe Fjelstad

- 64 IMPACT 2014: IPC on Capitol Hill "Leadership in Promoting a Strong Manufacturing Economy" by John Vaughan

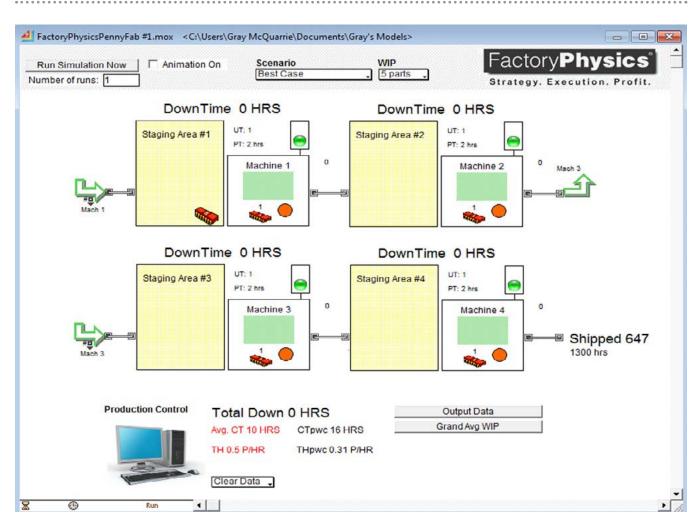

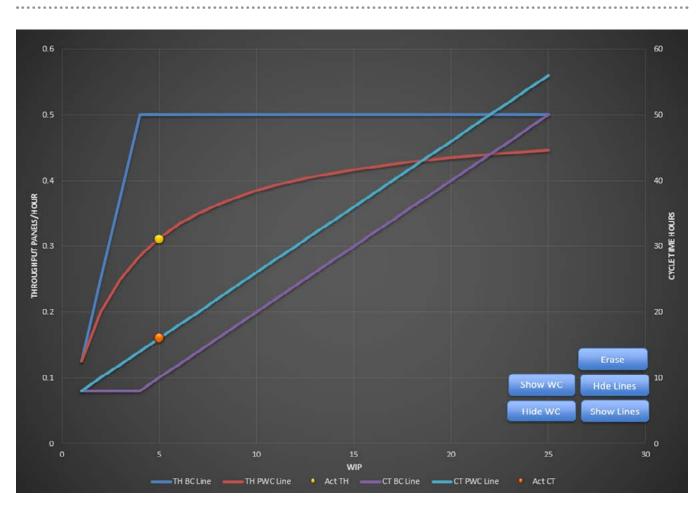

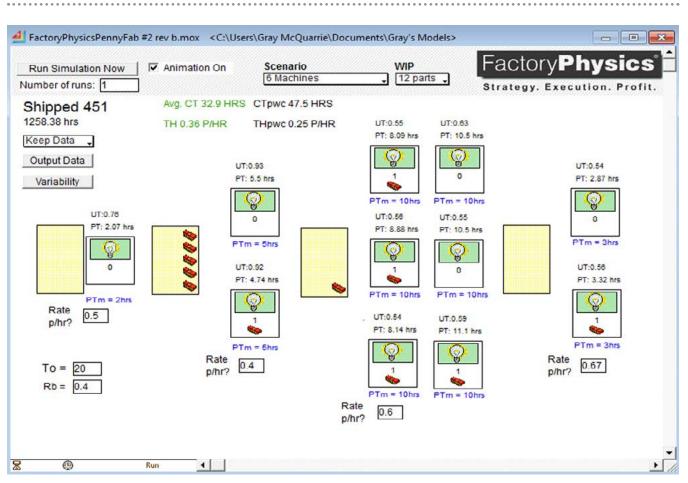

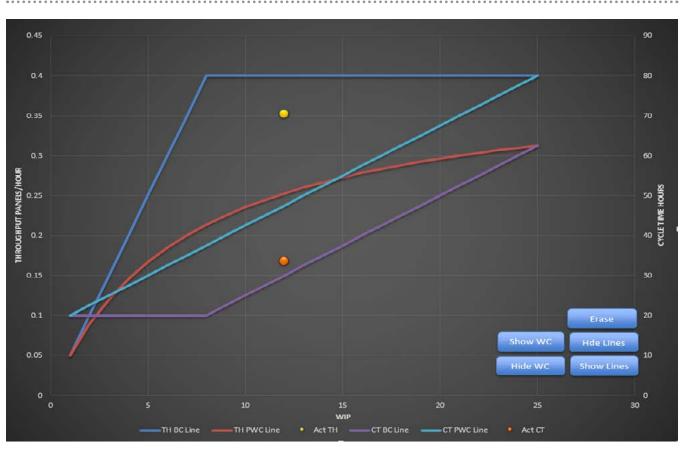

76 Why Removing Your Bottleneck is a Bad Idea by Gray McQuarrie

86 Oxide Alternative Processes: Performance Characteristics by Michael Carano

### PANEL DISCUSSION VIDEO

15 The Great File Format Transfer Debate

### VIDEO INTERVIEWS

61 IPC-7092: Embedded Standard Update

83 ETI/NEA: Combining Expertise through Merger

### SHORT

89 New Hybrid Circuit Could Take the Place of Silicon

### NEWS HIGHLIGHTS

- 62 Markets

- **70** Supplier/New Product

- 84 Mil/Aero007

- 90 Top Ten PCB007 News Highlights

### EXTRAS

92 Events Calendar

93 Advertisers Index & Masthead

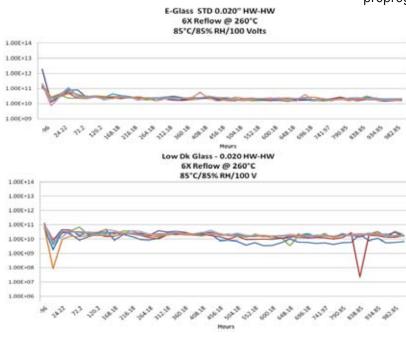

## Discover the Best-in-Class Laminate for High Voltage, Tight-pitch PCB Designs

### **I-Speed® High Speed Digital Materials**

I-Speed laminate and prepreg products are manufactured with Isola's patented high-performance multifunctional resin system, reinforced with electrical grade (E-glass) glass fabric. This system delivers a 15% improvement in Z-axis expansion and offers 25% more electrical bandwidth (lower loss) than competitive products in this space. These properties coupled with superior moisture resistance at reflow, result in a product that bridges the gap from both a thermal and electrical perspective.

### **I-Speed CAF Test Vehicle Results**

- Passed: 85°C/85% RH/100V after 1,000 hours at 0.65 and 0.75 mm pitch

- Passed: 35°C/85% RH/10V after 500 hours at 1.0 mm pitch

### **I-Speed Features**

- Global constructions available in all regions

- Optimized constructions to improve lead-free performance

- Improved Z-axis CTE 2.70%

- IPC 4101 Rev. C /21 /24 /121 /124 /129

- A low Df product with a low cost of ownership

- VLP-2 (2 micron Rz copper) standard offering

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

### www.isola-group.com/i-speed

### Electronic Assembly with Solder: an Unblinking Look at "The Devil We Know"

**by Joe Fjelstad** VERDANT ELECTRONICS

Solder is unquestionably highly practical technology for joining metals, and carries with it a long history. Its roots go back more than 2,000 years. Somewhere in the distant past, one of our more clever and observant ancestors chanced to create an alloy of tin and lead that melted at a low temperature. They or someone who learned of their discovery found that this unique combination of elements could be used to join pieces of metal together. This combina-

tion of chance observation and applied imagination has proven a key development in the technological history of mankind. Those in the electronics industry of today are very familiar with this ancient technology and today it is still the method of choice for making electronic assemblies of every sort. The only fly in the ointment is that the EU parliament, in a mad rush to try to look "green," took the emotional and scientifically ill-advised position that lead needed to be banned from electronic solders.

Sadly, there was never presented a credible piece of scientific evidence that any user had ever been harmed by tin-lead solder in electronic equipment. Nor could they prove their assertion that it would be a risk to ground water. That said, it is true that greed and

complete mismanagement of electronic waste boarding on criminal behavior, has resulted in physical illness and environmental harm in areas of the world where uncontrolled recycling was being carried out by uneducated individuals. While all

prototron.com

# We Take the Time to do it Right because you don't have the time to do it over.

is not yet well in that regard, that "hole" in the system is being addressed by businesses, NGOs and governments around the world.

Not to be forgotten is the fact that the impact of the EU's decision has been significant and far-reaching and it has caused the industry to spend needlessly many tens of billions of dollars diverting the considerable talents of countless talented engineers and scientists around the world to make products that are unfortunately proving less reliable and arguably less environmentally friendly electronics than those built with tin lead solders.

#### The Devil We Know, Disrobed

While soldering (especially tin-lead soldering) holds many benefits in terms of offering a means of mass assembly of electronic components to printed circuit boards and is fundamentally simple, its application in the assembly and manufacture of electronic products of the present age is much more complex and fraught with opportunity for defects to be generated, but it is also the a demon we have elected to live with, for as the old saying suggests that "Better is the devil we know." The devil we know is at least familiar and the simple truth is that humans are creatures of habit and most of us abhor change. There is a lingering question in the current situation? Is dealing with the devil we know on a daily basis really worth the price we are paying?

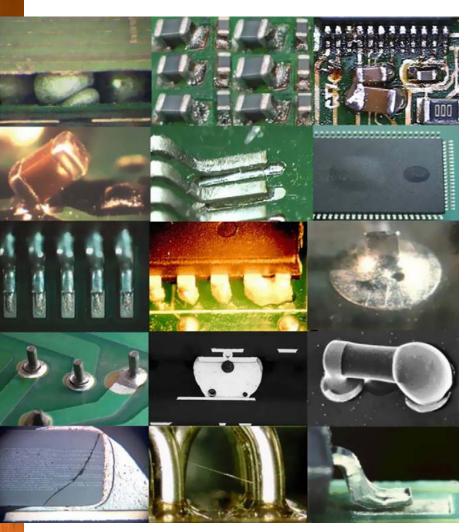

Following is a recitation of some of the many types of solder and solder-related defects that test and inspection is tasked with finding before a product reaches market. Bear in mind as these defects are recounted and reviewed that the cost of defects rises as a product moves further from the manufacturing line.

**a) Opens:** Opens are discontinuities generated in the soldering process that can be manifest in assembly in a number of ways. For example, a bent or lifted lead on a QFP component, missing solder ball on a BGA, insufficient solder on an LGA or the warpage of the component during the high-temperature, lead-free reflow process can all result in an open circuit.

**b)** Shorts: Solder shorts are bridges of solder between one or more component leads on

an assembly. As component lead pitch continues to drop, the incidence of short circuits increases. Presently, the threshold of pain for most assembly is experienced when the lead pitch drops below 0.5 mm.

c) **Insufficient Solder:** Insufficient solder is a condition where the amount of solder in a solder joint is less than desired or specified contractually through industry specifications or customer requirements.

**d)** Excessive Solder: Excessive solder is obviously the opposite of the condition of insufficiency and is again measured against agreements. It also introduces a wild card because it is not what reliability testing is based on.

e) Solder Cracking: Solder cracking is an obvious concern as it could result in a latent open circuit condition. Good during product test before shipping but then failing in the field.

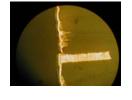

**f) Tin Whiskers:** Tin whiskers are small metal projections emanating from a solder joint. They can grow up to 15 mm long and given the fine pitch of today's components, they are a significant concern. There are also challenging because they are typically a latent defect that shows up unpredictably. Past research indicated that the addition of lead to tin solder alloys would mitigate the formation of whiskers; however, with the ban on lead in electronic solders the incidence of whiskers is on the rise.

**g) Poor Wetting/Dewetting:** Good wetting is manifest by the presence of uniform coat of solder on both the leads of the component and terminations of the printed circuit to which they are joined. In areas of poor wetting or dewetting the solder thins appreciably in areas leaving only a thin silvery sheen.

**h) Voids:** Voids are defect which are often difficult to detect without use of special equipment such as an X-ray apparatus. The challenge with voids is that they represent potential weakness in the solder joint owing to their inconsistent nature. Voids can be found both in through-hole and surface mount components. In the case of surface mount components the voids are often extremely small and are sometimes referred to as champagne voids.

**i) Blowholes:** A term applied to a phenomenon where a small hole is observed in a

#### **ELECTRONIC ASSEMBLY WITH SOLDER** continues

solder joint. Typically, the defect is found to be the result of discontinuities in the plated through-hole wall, which may absorb flux and then explosively out gas during the soldering process.

**j) Cold Solder Joints:** Solder joints that did not form completely a good metallurgical bond. They are often the result of the joint receiving sufficient heat to cause complete melting and joining of the solder. Cold solder joints are often seen in cases where the component lead is connected to a large thermally conductive feature or element and insufficient heat is retained near the lead to assure a

good solder joint. With lead-free solders, the phenomenon provides a greater challenge as the amount of heat which must be supplied is much greater than it might have been with a tin lead solder, thus potentially degrading device and assembly reliability.

**k)** Brittle Solder Joints: Solder joints wherein the alloy formed in the soldering process due to dissolution of elements within the finish or on the circuit board (e.g., gold), results in a solder joint that is less ductile than the solder used in the assembly process.

**I) Head-on-Pillow:** A new type of defect which was identified only with the introduction of lead-free soldering. It is an unsettling type of defect in that it is not easily detected but could result in an intermittent open in the operation of the assembly. The term was chosen because the phenomenon is reminiscent of an individual's head forming a depression on a pillow.

**m) Graping:** Another lead-free related defect wherein the small, often ball-like particles of solder in a solder paste do not reflow completely, leaving a surface that looks like the surface of a bunch of grapes. Like head-in-pillow, it is a defect that may not be easily detected.

**n) Tombstoning:** Tombstoning is a term that has been applied to the appearance of a defect related to discrete devices such as resistors

and capacitors, wherein solder connections are not made simultaneously; the slight lag causes the first side to reflow to pull back and rotate up, resembling a grave marker (which is somewhat apropos given that the assembly will likely be dead if tombstones are present).

**o) Component Cracking:** Component cracking can have multiple causes, one being a situation where there is a significant mismatch in terms of coefficient of thermal expansion between the component and the printed circuit to which it is attached. It can also occur if the assembly is flexed in the area of the component,

causing the device to crack.

**p) Popcorning:** Popcorning is a phenomenon manifest when moisture entrapped within a component outgases during assembly, causing a blister to form in the encapsulation material. With the advent of lead-free soldering and its higher temperatures, the incidence of popcorning rises and in fact moisture sensitivity levels of components are degraded to reflect the new reality.

q) Solder Balling: Solder

balling is a condition which happens during the reflow of a solder paste on a surface mount assembly. It is a result of the high

temperature of reflow causing rapid volatility station of the flux and spatter of the solder particles that are part of the flux. While a viable solder joint may be created even as solder balls are being formed, they represent a risk to the long term reliability of the assembly as potential shorting elements.

**r) Misregistration:** Components with fine pitch leads, if jostled before or during the assembly, may be misregistered relative to the land pattern, resulting in a nonfunctional product.

s) Insufficient Cleaning Under Devices: As mentioned previously, insufficient cleaning under surface mount devices can result in latent failure through the formation of high resistance shorts or the growth of dendrites.

Component cracking can have multiple causes, one being a situation where there is a significant mismatch in terms of coefficient of thermal expansion between the component and the printed circuit to which it is attached.

### **ELECTRONIC ASSEMBLY WITH SOLDER** continues

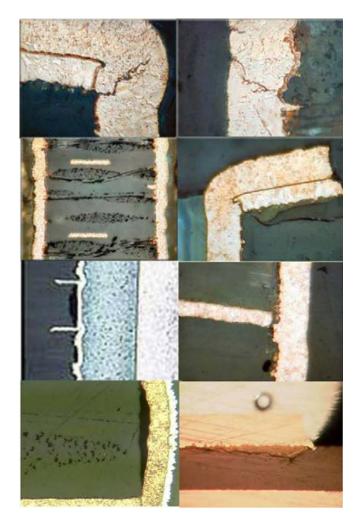

Figure 1: Representative images of some of the solder related defect found on printed circuit assemblies. Top row – left to right: head in pillow, graping, misregistration short and overheated flux. Second row, left to right: tombstoning, insufficient solder with open, popcorning. Third row, left to right: dewetting, blowhole, shorting between adjacent leads. Fourth row, left to right: cracked solder joints, voids, excessive solder. Bottom row, left to right: cracked component, tin whisker, open (lifted lead).

Clearly there is a great deal of nuance in the detection and identification of solder related defects; numerous books have been written over the last few decades that both characterize and suggest methods for eliminating or mitigating them (the devil is also "in the details" as another aphorism attests). It is not within the scope of this brief commentary to provide detail on all of the various types of solder related defects which can extend from the macro to the micro but for the benefit of the reader the following figure is offered providing representative examples of a number of the defects described above.

### The "Devil's" Impact on the PCB

The importance of managing the soldering process is clear, but making a good solder joint is also just part of the story and there are a number of defects that can be generated within a printed circuit assembly because of the soldering process, including:

**a) Corner Cracking:** A crack that forms at the interface between the whole and the land that surrounds. It is normally the result of the Z-axis expansion of the PCB during the thermal excursions such as soldering.

**b) Barrel Cracking:** Another phenomenon associated with the soldering process; it is similar in some ways to a corner crack except that it is manifest near the center of the hole.

**c) Post Separation:** A separation of the plating in the through hole from an innerlayer connection

**d)** Hole-Wall Pull Away: Hole-wall pull away is manifest as a bulge in a plated through hole, which reduces its diameter.

e) **Resin Recession:** Roughly, the opposite of hole-wall pull away wherein a small gap is formed be-

tween the plated hole wall and a resin rich area of a plated through-hole

**f) Delamination:** A separation of the layers of a multilayer circuit. It is normally seen in cases where the glass transition temperature of the resins used in the multilayer structure is exceeded.

**g) Pad Cratering:** Another phenomenon unseen before the introduction of lead-free sol-

### INTRODUCING COOLSPAN® TECA thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

### CONTACT YOUR SUPPORT TEAM TODAY

Leading the way in... • Support • Service • Knowledge • Reputation

### SCAN THE CODE TO GET OUR CONTACT INFO.

Greg Bull Applications Development Applications Development Manager Northern Territory (U.S.) & Canada

Dale Doyle Applications Developmen Manager Western Territory (U.S.)

Applications Development Manager Southern Territory (U.S.) & South America

Applications Applications Development Manager Eastern Territory (U.S.)

Kent Yeung Regional Sales Director *Asia*

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

www.rogerscorp.com

#### **ELECTRONIC ASSEMBLY WITH SOLDER** continues

dering. It is manifest as a circumferential tear of the copper land to which a component, normally a BGA, is assembled.

**h) Decomposition:** Decomposition of a PCB is a relatively new phenomenon associated with higher temperatures used with lead-free soldering. In fact, a new term was added to the industry lexicon,  $T_{d'}$ , which is the temperature of decomposition representing a loss of a specified percentage of the weight of the printed circuit.

Clearly, printed circuit technology, like soldering technology, is fraught with its own vulnerabilities due to the complexities of processing. The demands on PCB technology foisted upon the industry by the imposition of lead-free soldering requirements have placed a heavy burden on the printed circuit manufacturing industry. The need for higher glass transition temperatures to assure a measure of survival through the elevated temperatures of lead-free soldering has required the printed circuit industry to qualify new materials. Simultaneously, there has been a demand placed upon the industry to remove halogenated flame retardants from its materials. This double-barreled challenge is one that the industry had not faced before. Moreover, the industry has been challenged to provide circuits with ever-finer features which operate at everincreasing frequencies.

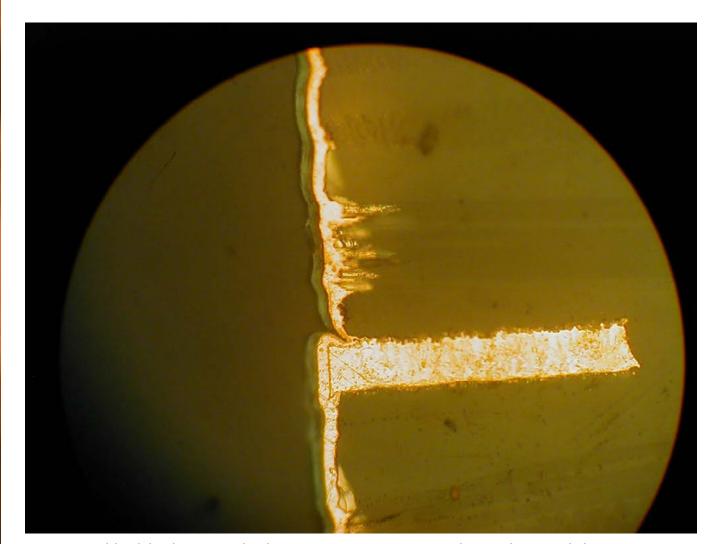

To their credit, printed circuit industry technologist, engineers and scientists have struggled admirably to address these challenges, including the challenge of finding solutions to defect modalities that were unknown to the industry just a few years ago. Unfortunately, a number of the defects described are related to soldering and its effects. The earlier problems have been exacerbated by the increased temperature required for lead-free soldering. Figure 2 offers cross-sections of representative printed circuit defects resulting from thermal excursions.

### Solderless Assembly for Electronics (SAFE) Technology: A Simpler Approach?

Given all the challenges and risks associated with soldering, every thoughtful and prudent manufacturing engineer must constantly be seeking a way or ways to make assembly processing more robust. If one looks for inspiration

Figure 2: Cross-sectional micrographs of printed circuit defects caused by soldering are provided above. Clockwise from the upper left-hand corner: corner crack, barrel crack, pad lifting, post separation, pad cratering ,hole wall pull away, resin recession and delamination.

on how they might end their dealing with the devil, they can find it in the Bible, where it is written: "If thine eye offend thee, pluck it out, and cast it from thee." Perhaps this is a bit extreme, but this seems to be where the industry is stuck today in dealing with the devil. Solder is by analogy an offending element of manufacturing and source of many if not most manufacturing problems. The industry will continue to have to deal with that devil as long as we persist in its use.

One can do their own research to test this assertion if they choose. They need look no fur-

ther than the titles of papers in publications. Presently, this and other industry/academic journals and proceedings on electronic manufacturing are rife with articles, papers, commentaries and advertisements offering new materials, processes and equipment both for manufacture and inspection to try and beat lead-free solder into submission. Unfortunately, solder appears a wily and crafty adversary that always seems to offer another challenge to each new solution proposed. This situation begs the question: "Is there any alternative?" The answer, in the opinion of this author, is "Yes." The answer is to assemble electronics without solder.

The potential benefits of eliminating solder is significant in many areas of current concern or high interest in electronic manufacturing, including: cost, reliability, performance, environmental impact, design security, a means of addressing some elements of counterfeiting, sustainability, a means of sidestepping conflict metals concerns and others.

So how can it be done? It is really quite simple:

Build assemblies in reverse and instead of placing and joining components on circuit boards with solder, build up circuits on "component boards" using copper plating, thereby bypassing the soldering process completely along with all of its many extra processing steps, ongoing challenges, and problems. The potential economic, environmental and reliability benefits are substantial as will be shown. The concept of SAFE assembly and its practicality will be examined in more detail in a future paper. **PCB**

Verdant Electronics Founder and President Joseph (Joe) Fjelstad is a four-decade veteran of the electronics industry and an international authority and innovator in the field of electronic interconnection and packaging tech-

nologies. Fjelstad has more than 250 U.S. and international patents issued or pending and is the author of Flexible Circuit Technology.

### I-CONNECTO07 PANEL DISCUSSION VIDEO

### **The Great File Format Transfer Debate**

Sponsored by Gardien Group

Altium's Ben Jordan moderates a multi-perspective look into file format transfer options with panelists Karel Tavernier (Ucamco), Dave Wiens (Mentor Graphics) and Hemant Shah (Cadence).

# Device Embedding in PCBs: Evolution or Revolution?

#### by Michael Weinhold

EIPC TECHNICAL DIRECTOR

### Abstract

EATURE

The embedding of components in electronic interconnection structures has been carried out for more than 30 years, and while different technologies have developed and were technically successful, history has shown that these embedding developments did not result in a sustainable success over a longer period of time. Replacement technologies have been developed after a short period of time by the so-called "Not in Kind" (NiK) technologies (e.g., inorganic = not in kind, organic = in kind).

This article will explain what is needed to avoid technology pitfalls that lead to future business failures.

In addition, opportunities are discussed that enable development managers, design engineers and specialists to use the full benefits of embedding devices in automotive, medical and industrial applications. These enabling manufacturing technologies will offer the opportunity to develop innovative product solutions in critical technical, environmental and business situations.

### Introduction

The number of PCB fabricators in Europe has declined over the last 20 years to less than 25% of what it was at the end of the 1980s. Today, Europe has little more than 250 PCB fabricators with a turnover of about US\$2.7 billion<sup>[1]</sup>. Large companies like Siemens, Philips, Alcatel and IBM closed their in-house PCB manufacturing plants long ago. For the remaining PCB companies in Europe the strategy is more focused on survival, with growth as a near-goal objective. Under these circumstances, innovation is a major part of the survival strategy. To stay in business today, it is important to understand what field of business the company is operating in and what are the means necessary to differentiate your company from other suppliers, wher-

**Electronic Chemicals, LLC**

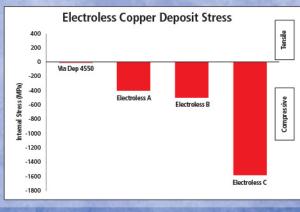

### Via Dep 4550 Electroless Copper

Electroless Copper for Difficult to Plate Substrates

Ready to Handle... The Most Challenging Surfaces On the Planet.

### Advantages:

Blister and Stress Free Copper Deposit

- No Harsh Pre-treatment Chemicals

- Low Temp, No Accelerator

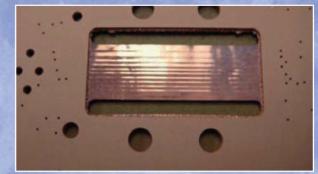

SUITABLE FOR FLEX, RIGID-FLEX, AND RIGID PWBS; COMPATIBLE WITH CONVENTIONAL EQUIPMENT.

**Making Holes**

CONDUCTIVE

#### DIFFICULT SURFACES CAN BE PROCESSED WITHOUT THE USE OF HARSH CHEMICALS SUCH AS HYDRAZINE.

POLYIMIDE FLEX WINDOW IN RIGID FLEX CIRCUIT BOARD.

#### VIA DEP 4550 HAS SIGNIFICANTLY LESS INTERNAL STRESS THAN CONVENTIONAL ELECTROLESS COPPER PRODUCTS.

### We've Got the Whole Process Covered

OMG Electronic Chemicals LLC

5630 Pioneer Creek Drive Maple Plain, MN 55359 P: 800-321-9050 • F: 763-479-3344 400 Corporate Court, Suite A South Plainfield, NJ 07080 P: 800-536-1959 • F: 908-222-3344

### **DEVICE EMBEDDING IN PCBS: EVOLUTION OR REVOLUTION?** continues

ever they may be. The PCB fabrication market was a suppliers market in the '80s. The supplier (i.e., the PCB fabricator) could set the prices for his products and the customer had to agree on it to get the products. Today, the PCB market is a buyer or purchasing agent market. The prices for PCBs are, in many instances, defined by the product buyer. Often, the PCB fabricator has no option but to agree to the offered price or he will not get the order. Furthermore, in longer-term contracts, price reductions are included-often between 5-10% p.a. Purchasing agents are using the well written IPC standards to define the workmanship and the quality of the finished PCBs. On many occasions these requirements are over-specified and do not reflect the required manufacturing technology and tolerances needed for a given application. PCB fabricators have to learn again that they are in the business to make money and that the PCBs are the tools to achieve this task. In addition, the PCB purchasing agents or buyers have to learn that only a PCB fabricator that makes money will be able to stay in business and will have the financial resources to invest in future technology, innovation, manpower and equipment.

#### **Embedded Technology in Europe**

#### Why use device embedding in PCBs?

Device embedding technology in Europe is used to add electronic, mechanical, thermal management and environmental function to PCBs as well as increasing the value to the basic PCB. For PCB fabricators, component embedding means leading integration in the supply chain. It will also shift the focus away from the PCB assembler to the bare board PCB fabricator who embeds the devices in the PCB.

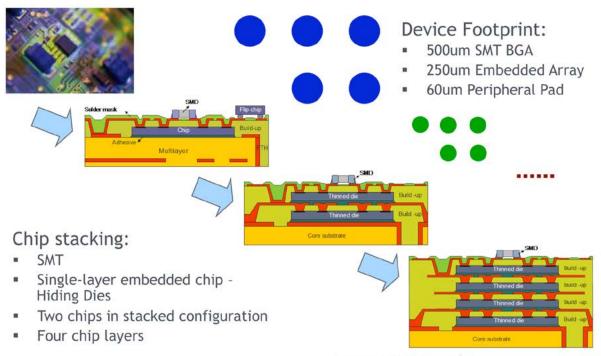

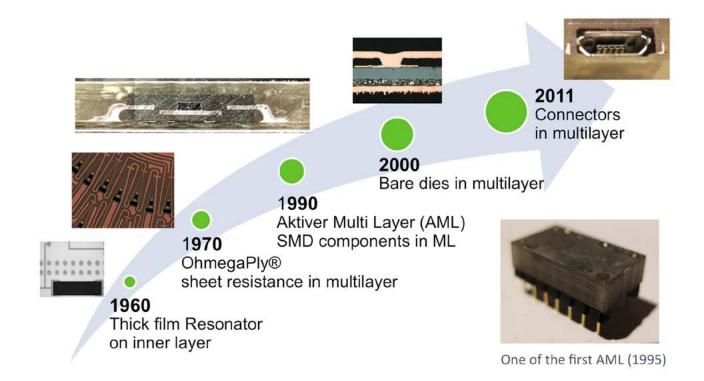

### Historical development of device embedding in PCBs

Embedded passive components have been used in large quantities in ceramic hybrid circuit fabrication since the '70s. Active components have been wire bonded, soldered or glued to such modules. In the late '90s, component embedded technologies using organic PCB materials were patented by Hofmann Leiterplatten GmbH for the AML technology<sup>[2]</sup> and by SIE-MENS AG in Germany for SIMOVE<sup>®</sup> technology.

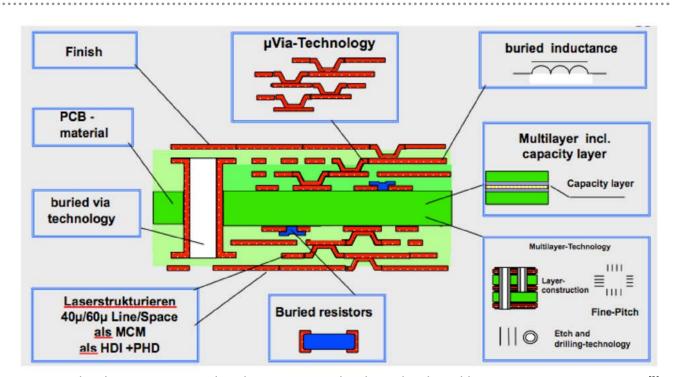

The SIMOVE (Figure 1) technology was very successful for a period of 2–3 years<sup>[3]</sup>. Licenses

Figure 1: Technology options used in the SIMOVE technology developed by SIEMENS AG in Germany<sup>[3]</sup>.

have been given to the PCB fabricator industry in Europe, necessary to overcome the issue of a single source supply chain. At the end of the '90s, the PCB industry was anticipating a growing business from this newly-developed SIMOVE<sup>[3]</sup> technology. So it was a big surprise that this investment did not result in additional business; indeed it was quite the opposite. At the moment the SIMOVE technology was ready for industrialisation, it was no longer needed. The reason was that the integration on silicon was so much advanced in functionality and cost-reduction that the embedding design—using PCB technology did not offer any packaging or cost benefits.

The questions that need to be answered are:

- Is there a market for embedded devices in PCBs in Europe or in the market worldwide?

- Under what circumstances could the PCB fabricator benefit from these markets or market niches?

To answer these questions we must look at the changes in the market and in the demand by key OEMs and industry segments.

#### **Semiconductors Drive Electronic Design**

In the electronics business it is important to understand that the semiconductor suppliers are much larger than PCB suppliers. The top 25 semiconductor fabricators (Figure 2) have a turnover of about 4 times the total global PCB market with more than 1500 fabricators worldwide.

As can be seen, the semiconductor market is no longer a fast growing market. The semiconductor industry is looking into opportunities in forward integration in packaging, like SiP (system in package) or even in SiPCB (system in printed circuit boards). When the quantities are large, the design on silicon is one option to expand the business.

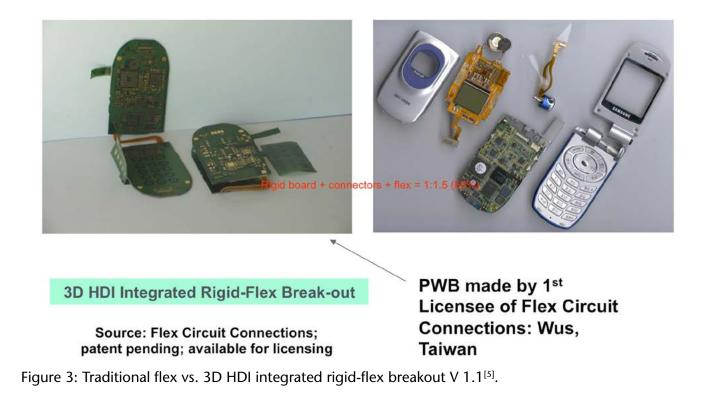

An additional example was experienced at the beginning of the smartphone era. Flip phones with many PCBs and flex rigid board combinations with integrated key boards were acclaimed as the solution for the future. Optimisation technologies with special rigid-flex PCB designs offered an excellent technical solution and generated more business for the PCB industry.

At this point, the semiconductor fabricators recognised the quantities needed in future for

| Rank Maker 2012 (2 | 2012 vs. 2011) |

|--------------------|----------------|

|--------------------|----------------|

Total Top 25 represent 234,232 -1%

| Rank | Maker                  | 2012   | 2012/2011 |

|------|------------------------|--------|-----------|

| 1    | Intel                  | 49,114 | -1%       |

| 2    | Samsung<br>Electronics | 32,251 | -4%       |

| 3    | TSMC                   | 17,167 | 18%       |

| 4    | Qualcomm               | 13,177 | 34%       |

| 5    | Texas Instruments      | 12,147 | -6%       |

| 6    | Toshiba                | 11,217 | -12%      |

| 7    | Renesas                | 9,314  | -13%      |

| 8    | SK Hynix               | 9,057  | -4%       |

| 9    | STMicroelectronics     | 8,364  | -13%      |

| 10   | Micron                 | 8,002  | -7%       |

| 11   | Broadcom               | 7,793  | 9%        |

| 12   | Sony                   | 5,709  | -6%       |

| 13   | AMD                    | 5,422  | -17%      |

| Rank | Maker           | 2012  | 2012/2011 |

|------|-----------------|-------|-----------|

| 14   | Infineon        | 4,993 | -11%      |

| 15   | GlobalFoundries | 4,560 | 31%       |

| 16   | Nvidia          | 4,229 | 7%        |

| 17   | Fujitsu         | 4,162 | -6%       |

| 18   | NXP             | 4,157 | 0%        |

| 19   | Freescale       | 3,735 | -15%      |

| 20   | UMC             | 3,730 | -1%       |

| 21   | MediaTek        | 3,366 | 13%       |

| 22   | Sharp           | 3,304 | 14%       |

| 23   | Marvell         | 3,157 | -8%       |

| 24   | Elpida          | 3,075 | -21%      |

| 25   | Rohm            | 3,030 | -8%       |

Figure 2: The top global 25 semiconductor leaders represent 4x the total global production of PCBs<sup>[4]</sup>.

Figure 4: Smartphone technology evolution. No keypad, no flip screen. Three keys, but a high definition touch screen that offers many more benefits compared to a conventional keyboard<sup>[6]</sup>.

these advanced mobile communication tools. In addition, smartphones become even smarter and more electronic functions were essential to meet the growing consumer hunger for new features. Video phoning, video games and television became standard requirements, besides making phone calls and sending e-mail, SMS and MMS messages. Today, smartphones without keyboards fulfill the function of communication tool, television, video player and videophone as well as a radio and music centre and, in some cases, they even replace computers.

When manufacturing such electronic devices, intelligent component packaging is the solution. Semiconductor fabricators can integrate these functions into a semiconductor package or even design it direct onto silicon. For the mobile phone, where the quantities are in the tens of millions, the required investment for these electronic devices can be easily justified. In the field of automotive applications, where quantities are smaller (< 10 million) the design on silicon may not be the solution. Here, the fixed costs of designing a customized chip, including the interfaces and the related software, are very high in relation to the quantities needed. However, when system-in-package and system-in-PCBs are more widely designed and accepted, this situation is more cost-effective and this will change how car electronics are designed and manufactured in future. New opportunities for interfaces between devices may apply in near field communication (NFC) protocols, may re-

Learn how your CNC machines can keep you informed of their status with SmartParts Monitoring.

+1 (949) 551-4135 www.fastec.com

### **DEVICE EMBEDDING IN PCBS: EVOLUTION OR REVOLUTION?** continues

place connectors and flexible PCBs, and may even change the automotive assembly technology. In addition, RFID components have become cost-effective alternatives to store important information about the assembly processes and environmental requirements and other unique device information. This technology will offer even more options for the software developers and system designers of the future.

#### **Advanced Projects in Europe**

Europe is strong in automotive, industrial, medical, photovoltaic, avionics and space electronics. In addition, power electronic devices are needed in many of the new electronic automotive application. As indicated in the beginning of the report, the PCB market is at present a buyers' market and the purchasing managers and/or agents define where the order is placed. For them, cost reduction is one of the key objectives, but will, in many cases, not go in line with innovation, reliability, traceability and environmental requirements.

The European industry depends on leadership through innovation in electronics. Compromises between cost-reduction and innovation are key drivers for the PCB fabricators and OEM/EMS industry in Europe. Today, PCB costs are calculated on a square meter or square decimeter level. The smaller the PC board, the lower the selling price for it will be.

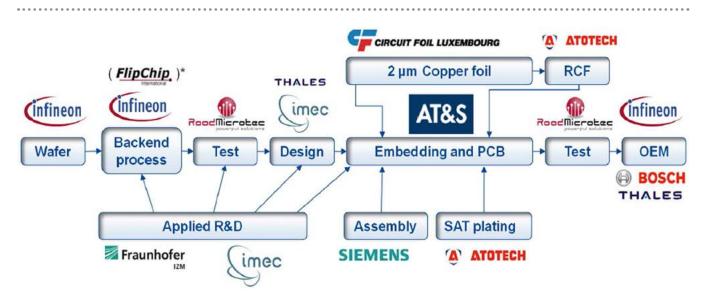

One example is the EU-sponsored consortium project "HERMES" (High density integration by Embedding chips for Reduced size Modules and Electronic Systems). The following companies have cooperated as partners: AT&S Austria Technologie & Systemtechnik AG, Atotech, Bosch, Circuit Foil, Fraunhofer IMZ, IMec, Infineon, Rood Microtec, Siemens A&D, Thales Communications France (Thales

Courtesy of AT&S Johannes Stahr

Figure 5: Project supported by the European Commission under the name HERMES. Industrialisation was carried out at AT&S in Austria together with Fraunhofer IZM in Berlin. The project partners came from the fields of acadæmia, OEMs, silicon fabricators, and the chemical, electro-plating and packaging industries<sup>[7]</sup>.

TCF) and Thales Corporate Services. This project resulted in a successful product development for a new technology, which is now used in Europe to manufacture several million units per month. In this project, the benefits of PCB technology have been modified in a way that it is fully functional in the area of cost-effective chip packaging fabrication.

In this project, the chip-in-polymer process has been developed and industrialised, which offers a reliable and cost-effective embedding technology for the realisation of modules and SiP development. This technology is applied in several projects with industry and R&D centers.

The industrialization of the technology within the "HERMES" project was a great achievement for the electronics industry in Europe. Without funding from the EU the partners would not have seen sufficient benefits and incentives to develop these new packaging technologies. The package realisation resulted in single and multi-die packages and provided a reliable and cost-effective solution compared in compared to conventional IC packages.

The HERMES project was direct applicationrelated and resulted in multiple levels of embedded chips, multiple lamination cycles, embedding of ultra-thin chips in flex, power modules and radar applications of 77 GHz.

The products that have been developed under this project are not easy to copy. Special investments are needed to perform the required technologies and co-operation between PCB fabricator, assemblers and chip fabricators are needed to get the required unpackaged components. At present, most of these products are manufactured in Europe.

Experience has proved that the European electronics industry very much depends on innovation. Based on such by the electronics industry, the Active Multi Layer (AML®) technology was developed by Hofmann Leiterplatten GmbH in Germany. The goal was to combine the benefits of the standard copper clad laminate, prepregs and epoxy resin as well as standard placement and soldering technology into one embedded device with an advanced thermal conductivity of these materials in one package. The key to success is based on using standard materials (Figure 9), assembly attachment and soldering processes in conjunction with some modified standard manufacturing PCB processes. Key in the success of this technology is the control of the design, the PCB fabrication and assembly processes. Today, standard PCB fabricators do not have these capabilities. However,

Figure 6: The success of the HERMES project was based on the involvement of the total supply chain for electronic devices. Representatives from silicon wafer fabrication, materials and process suppliers, to packaging to end-users with specific applications proved the need for this form of package and product<sup>[8]</sup>.

### **DEVICE EMBEDDING IN PCBS: EVOLUTION OR REVOLUTION?** continues

Figure 7: Device embedded technology in PCBs using standard packaged components. Active multilayer (AML<sup>®</sup>) technology developed by Hofmann Leiterplatten in Germany can use standard components including connectors inside the PCB. Miniaturisation, reliability and improved thermal management are achieved simultaneously<sup>[2]</sup>.

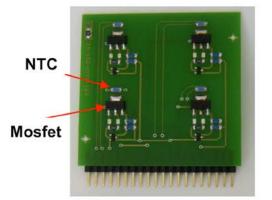

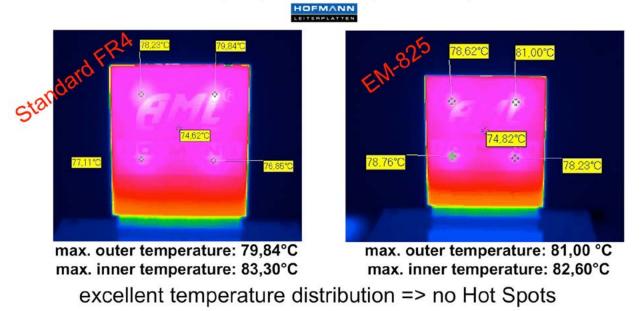

Experimental setup I: Standard FR4 PCB, 1.5 mm, 2s PTH, without additional Thermal via PCB Dimension: 54 x 62 mm 4 x Mosfet with each 1,5 W power operated = overall performance 6 Watt

DEMANN

Temperature am NTC: 110°C

max. temperature: 188.5 °C Poor temperature distribution => Hot Spots

Figure 8: Mosfet components on standard assembled PCBs can generate high temperature, as cooling is only by ambient air which has low thermal conductivity<sup>[2]</sup>.

# ELITE MATERIAL CO., LTD

### Mid & High Tg Halogen-Free Material

Halogen-Free Mid Loss

Halogen-Free Low Loss

### **Bridging the gap between OEMs and PCBs**

- Innovation

- Globalization

- Diversification

www.technica.com

for future high-added-value PCB products and innovative solutions, forward integration will be important for PCB fabricators.

In the experiment, standard PCBs where assembled with four Mosfet components powered

| Material | Thermal Conductivity in W(m/K |  |  |

|----------|-------------------------------|--|--|

| Acrylic  | 0.2                           |  |  |

| Air      | 0.024                         |  |  |

| Aluminum | 250                           |  |  |

| Copper   | 400                           |  |  |

| Ероху    | 0.35                          |  |  |

| Glass    | 1.05                          |  |  |

| PTFE     | 0.25                          |  |  |

| Silicon  | 149                           |  |  |

| Water    | 0.58                          |  |  |

Figure 9: The thermal conductivity of different materials used in PCBs indicate that air is not the prefered media when thermal disipation is required. Epoxy resin has a 0.35 W(m/K) thermal conductivity and glass has 1.05 W(m/K)<sup>[9]</sup>.

with 1.5 W. The PCBAs were operated for some time and then the surface temperature was measured. Using thermography measurement methods, the temperature showed hot spots of >188°C at the components. Even the thermosensor still showed a temperature of 110°C. Life expectation of electronic devices depends on the operating temperature of the components and the co-efficient of thermal expansion in X-Y and Z direction. Operating an electronic device at a lower temperature will increase the life expectancy or the mean time between failures (MTBF).

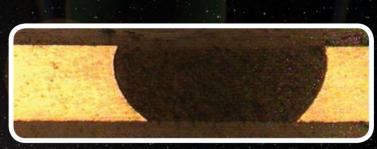

Repeating this experiment with the same layout, the same type of components and same manufacturing technology was used to embed the components inside the PCBs. In this process, the components are completely surrounded by epoxy resin and glass fibres used in copper clad laminate and prepregs. A dramatic temperature drop at the component was achieved. As shown in Figure 10, the thermal conductivity of the base material indicated no hot spots on the

Experimental setup IV:Experimental setup. Without additional Thermal Vias, with Heatsink 2,0 mm (mounted on PCBs back). PCB dimension : 54 x 62 mm

4 x Mosfet with 1,5 W power consumption = total power 6 Watt

Figure 10: Components embedded inside the PCB assembly have shown much lower temperatures based on better thermal conductivity of CCL compaired to air<sup>[2]</sup>.

## When you need fast, reliable and cost-efficient bare board modifications, we are your **BEST** choice!

Learn More 🕞

Pad & Trace Repair

Learn More 🕞

BEST-

Business Electronic Soldering Technologies

See for yourself! Get a free sample evaluation board!

www.<mark>solder.n</mark>et <mark>| 8</mark>47.<mark>79</mark>7.9250

FREE SAMPLE

FAST • RELIABLE • COST-EFFICIENT PCB MODIFICATIONS

PCB. The total PCB temperature is lower, not only at the components.

It is expected that the PCBs with embedded components are operated at a lower temperature. This will result in an extended operating life of the electronic device. An OEM and or EMS company can use this benefit to show a larger number of hours for the MTBF. This will be a reliability argument when it comes to product life expectation and will be, in many cases, a strong sales argument and it indicates a commitment to quality.

The component embedding technology offers an additional benefit in protection against environmental contamination, dust, humidity, gases and various chemicals. Encapsulating in epoxy resin can, under certain circumstances, replace housing, improve EMC shielding, help in miniaturisation and improve the thermal properties of the electronic devices.

#### Impact of European Commission on Embedded Innovation

To understand the opportunity for technical innovation, it is important to consider the markets the European industry in operating in. As countries operating under EU legal administration, it is important to adapt to the legal changes in Europe since the European Union was, in its present form, implemented in 1992<sup>[11]</sup>.

The 24 official languages in the EU can make communication difficult, but although about 20% of the population in Europe speak German, it is widely recognised that English is the language of business<sup>[12]</sup>.

In Europe, the German-speaking counties represent a large section of the industrial production and it is recommended to communicate in the local languages. This is very important at the new electronics development stage when new products are being designed. In addition it

### Embedding of Components is not NEW in Germany

Embedding components and LEDs by Hofmann Leiterplatten GmbH, Germany

Figure 11: LEDs embedded in CCL survive exposure to chemicals and water/humidity very well. In this sample, the illuminated LED strips are partially in water for more than five years, without damage<sup>[2]</sup>.

### **DEVICE EMBEDDING IN PCBS: EVOLUTION OR REVOLUTION?** continues

is important to understand that electronic designers in many cases are not the PCB designers. Printed circuit board designers do not know all the details required to design for manufacturing (DFM) and design for the end-use application where the final electronic device is used. To design for the best technical and most cost-effective solution, close cooperation in the supply chain is a major key for success. Here, a strong impact on cost is given by the fact that PCB solution can be manufactured locally during the development phase.

It is a common practice that prototype and small series of PCBs are sourced usually at local PCB fabricators (Figure 13). Here, good communications and technical know-how of the PCB fabricators are needed to manage an effective development cycle and to ensure that the electronic devices are working as specified. These development cycles have sometimes been seen as difficult, when language barriers and technological standards as well as different manufacturing standards are used. In the areas of industrial electronics, medical and avionics and space application, the quantities of PCBs that are required are small to medium. These run lengths can be cost-effectively manufactured in Europe. But when it comes to consumer electronics and automotive, the situation is different.

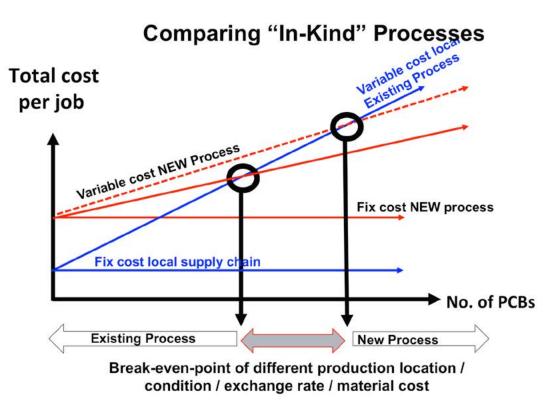

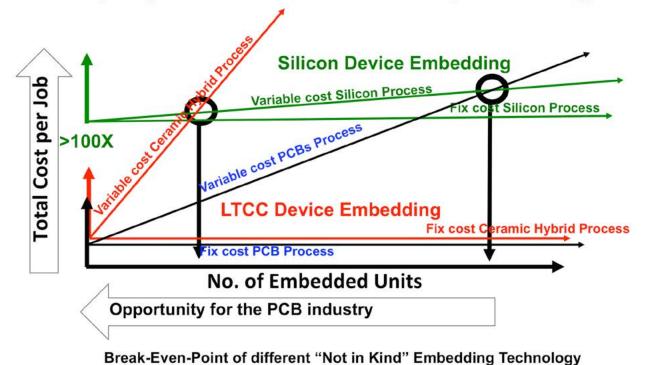

In the automotive field, much product development takes place in Europe, and therefore the prototype PCBs and the start-up production originates in Europe. When larger quantities of products are needed, and the PCB technical requirements are well covered by standards, lowcost manufacturing countries are chosen. However, when the demand for the required units gets larger, the in-kind PCB fabrication process may be changed against a not-in-kind (Figure 14). Therefore it is important to understand that different technical solutions can adopt different manufacturing technologies. These are the following options:

- Organic material solution (PCB)

- Ceramic material solution (LTCC)

- Silicon technology solution (SiS)

Standard processes for production SiPC-Boards

- Standard SMD assembly process

- Standard PCB production process

- Standard and tested PCB materials

- Improved thermal management of components

- Better thermal connection of the components

- Lower component temperatures

- Longer lifetime of components

- Benefits of embedded components

- Longer lifetime of electronics

- Better thermal management of electronics

- No special device housing (case) needed

Figure 12: Proximity sensor with two assembled inner layers and 90 integrated SMDs. All of the parts were made using PCB manufacturing technology and materials and the applied process (AML) was developed by Hofmann Leiterplatten in Germany<sup>[2]</sup>.

Figure 13: Small series of PCBs using an in-kind PCB technology are manufactured locally while large series are often sourced globally<sup>[10]</sup>.

#### **Summary and Outlook**

New product developments require new ways to improve quality, miniaturisation, and efficiency, including energy efficiency, and in many cases improved thermal management. Device embedding technology in PCBs has a large potential to meet these future requirements. However, PCB fabricators have to learn how to absorb and master the technology challenges not only of fabrication, but also of assembly of device testing, and end use application.

In addition, PCB fabricators have to understand that the actual quantities of manufactured boards will determine the market opportunity for the printed circuit board technology. When quantities are large, as in the mobile phone or computer tablet business, the chip and the chip packaging industry will sooner or later work out a solution that takes this market segment away from the PCB technology (Figure 14).

Based on historical information from the hybrid circuits industry in the '80s and from organic embedded device technology (e.g., SIMOV) in the '90s, the PCB industry has to encourage electronic designers to focus on many new developments in technology. This will stimulate demand in the area of small to medium PCB quantities, and, based on the cost structure of the PCB fabrication process, the production of small batch sizes should offer a good return for the PCB For the semiconductor indusfabricators. try the start-up fixed costs are too high to focus on a small number of products, and therefore these market segments are of little interest to the chip and the chip packaging industry. In addition, many new designs require good engineering at the PCB fabricator and a good communication between the development engineers. Both must exist to ensure success. PCB

### Comparing "Not-In-Kind" Processes or Disruptive technology

Figure 14: For large quantities, a not-in-kind technologies may offer technical as well as cost benefits. In addition dimensional changes and miniaturisation are also key drivers for alternative technologies<sup>[10]</sup>.

References

1. WECC for Market data, 2013 and Michael Gasch, of Data4PCB publication.

2. Thomas Hofmann of Hofmann Leiterplatten GmbH, Regensburg, Germany. Presentation on ECWC12 in Taiwan Paper No: EU173 and paper at the ECWC13 in Nuremberg, May 2014. Presentations on congresses 2006–2012. Publications in any professional journals (e.g., PLUS, PCB007); DE-Patent: DE19627543; DE-Patent: DE102005017838; EP-Patent: EP12007766; Trademark: DE30201301845; Trademark: DE39607556.

3. Siemens AG, Karlsruhe, Germany.

4. IC Insights 3/2013.

5. PWB flex Circuit Connection USA/WuS, Taiwan 2002.

6. iPhone 5, Apple Computer, 2013.

7. Johannes Stahr of AT&S, Leoben, Austria 2012.

8. ACB, Belgium April 2012.

9. Alun Morgan of ISOLA.

10. "Value in Use" to define optimum technology / Cost option. Michael Wienhold.

12. ISBN: 92-826-3445-0, Reference No.: RX-72-91-568-EN-C, Publication year: 1992.

13. The European Union (EU) has more than 500 million inhabitants, who represent a large industrial and consumer market. The EU today has the third largest population after China and India.

Michael Weinhold is the technical director of the European Institute of Printed Circuits. He may be reached at <u>mkweinhold@t-online.de</u>.

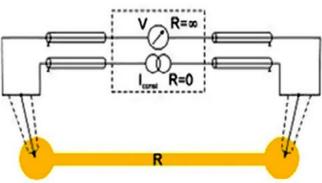

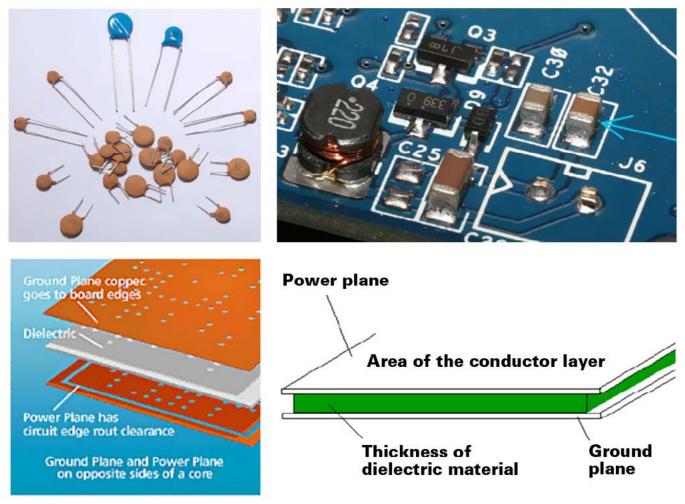

# RF Capacitor Material for Use in PCBs

by Jin-Hyun Hwang, John Andresakis, Ethan Feinberg, Bob Carter, Yuji Kageyama, and Fujio Kuwako OAK-MITSUI TECHNOLOGIES

### Abstract

A novel ceramic-functional-particle-filled polymer composite material has been developed for the use either in discrete elements on the PCB or in being embedded within the packaging substrate for high-frequency circuit applications. This material provides the desired properties such as low loss at high frequencies (about 0.002 or less up to 10GHz) and high dielectric strength, among other improved properties. The electrical properties were influenced significantly by the ceramic-functional-particle (type and particle size/distribution in the polymer matrix). Their contributions to the electric strength and temperature stability of capacitance (which is an important material issue for practical device application) will be discussed. In

addition, capacitance tolerance for manufacturing an embedded RF capacitor will be presented in terms of etching uniformity to minimize the variation of the capacitor electrode areas.

### I. Introduction

Organic-based dielectric materials has been explored for the use either in discrete passive components on the PCB or in being embedded within the packaging substrate as part of RF/microwave circuits<sup>[1-4]</sup>. Using ceramic-functionalparticles (fillers), filled polymer composite material is merely a convenient and inexpensive way (to compete with ceramic chip capacitors) achieving low ESR (equivalent series resistance), high SRF (self-resonant frequency) for RF capacitor application that can support frequencies well above 1GHz. Besides, embedding fillers into the polymer enhances properties of dielectric materials (by optimizing filler chemistry and its distribution in the polymer matrix) such as temperature stability of capacitance for high precision RF circuit and dielectric strength (the

# The latest in gap filling at Taiyo

## THP®-100DX1 (GF)

### Thermal Curable Gap Filling Dielectric

- Used to make High Copper Inner Layers Planar

- Screen Print Application with Flame Resistant Properties

- High Tg (160°C) and Low CTE (32/115 ppm)

- Very Low Shrinkage and Ease of Planarization

- No Chemical Attack through Desmear

- Excellent Adhesion Between Layers

- Compatible with Lead-Free Processing

- Halogen Free and RoHS Compliant

Courtesy of Micro PCB

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

### **RF CAPACITOR MATERIAL FOR USE IN PCBS** continues

maximum DC electric field strength applied across the dielectrics in RF capacitor) for a high voltage rating which is essential especially for servers, pico cell and femto cell in base station market space. Generally, fillers are widely accepted in various applications because of their advantage in addressing several limitations of polymers, making its way onto benefits such as better dimensional stability for polymer composite membrane, lower coefficient of thermal expansion (CTE) for build-up layer, increasing thermal conductivity for thermal interface materials (TIM), and improved stiffness for underfill materials. As for the fillers in RF capacitor application, it is presently based almost entirely on the simple perovskite BaTiO<sub>3</sub> (barium titanate), but there is strong demand on the class of materials known as paraelectrics, mainly due to the fact that their dielectric properties are much more stable with regard to most operating conditions such as frequency, temperature and DC bias<sup>[5]</sup>.

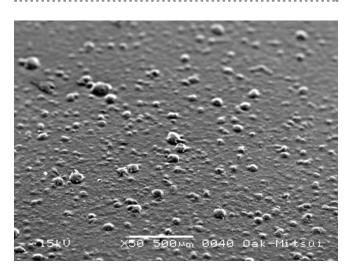

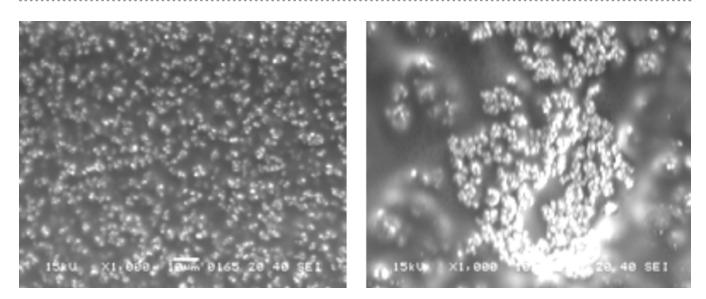

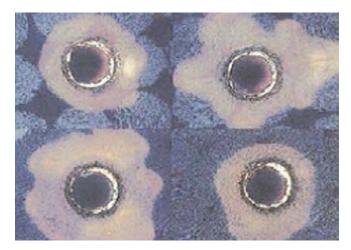

Well-dispersed fillers in polymer composite matrix play a crucial role in achieving RF capacitor requirements as described above and thus factors that determine fillers distribution should be controlled and optimized. Any existence in the particle agglomerates is accompanied by the formation of possible defects such as trapped porosity that make the dielectrics

Figure 1: SEM image (at tilt angle) of the typical filler agglomerates of ceramic filled polymer composites (on the coating surface).

vulnerable under practical operating conditions. Figure 1 shows typical example of severe filler agglomerates clearly visible, concentrated on the coating surface as discrete protuberances and appearing to be in greater numbers. Filler agglomeration is easy to observe by improper usage of dispersion agents and their mismatching to a solvent composition in formulation. It could degrade electrical properties, in particular dielectric strength and temperature stability of capacitance (both will be described in next section). Various types of coupling agents can be added to the polymer compositing to take advantage of the absorption of a functional polymer to the particle surface to modify the filler/polymer interface chemistry, giving rise to complete de-agglomeration of the fillers and subsequent elimination of the air void<sup>[6]</sup>. It is also necessary to adjust the solvent composition combined with the coupling agents, which is associated with coupling, adhesion and dispersion. In this study, a titanium-based coupling agent and a typical solvent mixture were selected and formulated with a paraelectic filler and a phenylene-based polymer. The optimum amount of the coupling agent was determined by the viscosity response for various levels of the application of the coupling agent. The deagglomeration effect was pronounced when significant reduction in suspension viscosity was observed. Optimal combination was formulated to make RF capacitor laminate that used thin dielectrics having thickness range of 12–25 µm.

### II. Results and Discussion

### A. Effect of Ceramic Functional Particles (Fillers)

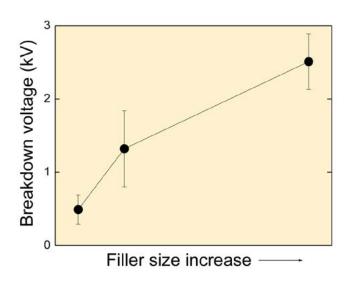

For practical device application, the contribution of the filler to the dielectric strength and the temperature stability of the capacitance are of greatest interest. The dielectric strength was examined by measuring dielectrics breakdown voltage (BDV) of the samples having fillers with different size (Figure 2). A circular pattern with 0.5 inch diameter was placed on a bottom electrode grounded to the DC tester. A probe was placed on the center of a circle and subjected to the voltage. The electrode material was made on one side of the copper of a RF capacitor lami-

## WorkCell<sup>2</sup> Vacuum Lamination System ... A Modular Design That GROWS With You

With the ability to expand as production needs dictate, Bürkle's modular WorkCell<sup>2</sup> provides a precision Vacuum Lamination System for every phase of business – from start-ups to high-volume production houses – we have the right system for you.

The Bürkle WorkCell<sup>2</sup> is part of Bürkle's wide range of laminating and coating systems. Bürkle is a member of the Bürkle North America alliance with Schmoll-Maschinen, Bürkle GmbH, IMPEX, LHMT and Bacher Systems. For more information contact Bürkle North America via e-mail: sales@burkleusa.com.

Alliance partner web sites:

- www.schmoll-maschinen.de

- www.buerkle-gmbh.de

- www.bacher-systems.com

- www.impex.co.at

- www.lhmt.de

Bürkle North America, Inc. 12802 Valley View St., Ste. 12/13 Garden Grove, CA 92845 TEL: 714-379-5090 FAX: 714-379-5092

#### **RF CAPACITOR MATERIAL FOR USE IN PCBS** continues

Figure 2: BDV variation of polymer compositing with the filler size.

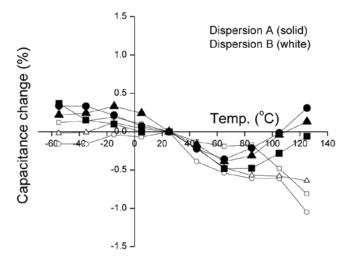

Figure 3: Temperature stability of capacitance of two samples prepared by different suspension preparation routes.

Figure 4: SEM images (on the coating surface) of samples with (a) dispersion condition A and (b) dispersion condition B.

nate. The dielectric thickness was set to 25µm for all samples. As shown in Figure 2, the effect of the filler size on the BDV was clearly detectable, and the BDV of the dielectrics composed of the larger size filler revealed a considerable improvement in BDV compared to the case of formulating with the smaller size filler. Lower BDV may result from non-uniform dispersion of the filler and it may induce the charging of the weak interface chemistry, probably repre-

senting the filler agglomerates. We continue to work on improving the material to achieve relatively high BDV even with small size filler by controlling the suspension chemistry.

Indirect evidence for the improvement of the filler distribution was sought by measuring capacitance change with temperature for samples fabricated with different suspension preparation routes. Temperature coefficient of capacitance (TCC) is an important material parameter to meet the tighter RF/microwave design tolerances. (Details on TCC were described previously<sup>[7]</sup>) Figure 3 shows that the TCC was rotating counterclockwise (direction to the positive TCC) toward the end of each curve at high temperature region. We mixed fillers with the polymer in an arbitrary way. Thus, in this physical construction of the polymer compositing, the dielectric is comprised of filler and polymer with the filler occupying the majority of the dielectric. The filler selected ended up slight positive TCC and the plain polymer (without filler) showed negative TCC. The filler contribution to the net composite TCC is dependent on its volume fraction and distribution. Therefore, it is assumed that the filler can control complete TCC by compensating for negative TCC of the polymer and positive TCC at higher temperature could be regarded as being responsible for the uniform filler distribution in the polymer matrix. SEM photos in Figure 4 supports this with different level of dispersion of the filler in polymer between two samples.

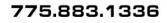

## **B.** Characteristics of **RF** Capacitor Laminate

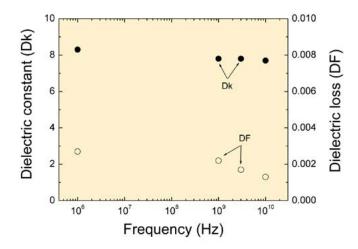

Figure 5 shows frequency stability of Dk (dielectric constant) and DF (dielectric loss) of our developed RF capacitor laminate product using the ceramic-particle-filled polymer composite. As for the method for checking Dk and DF, the first point in Figure 5 used the lower frequency method (LCR meter) and the remaining three used the split post resonator cells which is useful to measure Dk for isotropic mixtures (when fillers are randomly oriented)<sup>[8,9]</sup>. The product is the copper clad laminate (CCL) with a standard panel, 18 x 24 inches. It was composed of two sheets of copper foils on both ends with organic based composite dielectrics having fillers dispersed into polymer in between. Copper foils are available in various thicknesses, 0.5 ounce and 1 ounce being the dominant thickness, but thinner copper foil would help to minimize the variation in capacitance during etching process in PCB manufacturing. The typical Dk and DF of the RF capacitor laminate at 1GHz were measured, 7.8 and 0.0022, respectively. We are expanding the product's capacitance density range up to 670 pF/cm<sup>2</sup> thinning dielectrics and

Figure 5: Frequency dependence of Dk and DF of the developed RF capacitor laminate.

process optimization. The standard reliability tests including solder shock, solder float, time to delamination and THB (temperature, humidity and bias) testing were performed and all these tests passed.

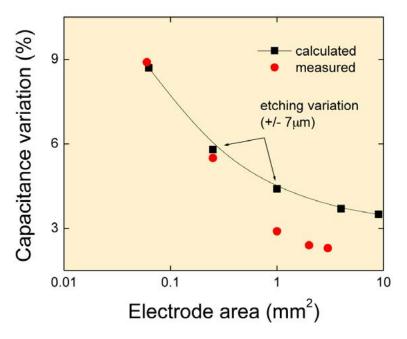

#### C. Uniformity of Capacitance

Capacitance tolerance for the organic-based RF capacitor laminate is critical for the application of forming discrete type embedded capacitors inside the organic packaging substrate. In this case, capacitance tolerance can be expressed as 3 sigma in the form of (mean of capacitance)  $\pm$  (3 sigma) for the foot print size of the capacitor. Smaller tolerance in capacitance is desirable to achieve better yield performance of the RF device in manufacturing<sup>[2]</sup>. However, when forming discrete embedded capacitors inside the organic substrate for RF module, the materials and processes don't currently allow for the tight tolerances due to the material and the process variation. The dispersion techniques for the ceramic fillers in polymer and the right coating method for putting the ceramic-filled polymer composite material on the copper can minimize the material variation. In addition to the material variation, the process variation (mainly etching variation) in formation of the electrodes by the etching process in PCB manufacturing will add to the tolerance. In order to understand the capacitance tolerance of the

capacitor laminate, uniformity of capacitance was investigated as a function of various capacitor electrode areas (0.25 mm square ~ 3 mm square) which were prepared by the standard etching on the test board. Figure 6 shows a typical result, showing the measured capacitance tolerance and calculated tolerance (expected) of capacitance. Actual measured uniformity of capacitance in smaller foot print of the capacitor showed a good correlation with an assumption that the etching variation is around  $\pm 7\mu m$ . Small footprint capacitors with tight tolerance is still being challenged, but the result in Figure 5 indicate that we can still achieve fairly uniform capacitance values with proper process optimization and control that will result in functional RF circuits.

#### **III.** Conclusion

The ceramic filled organic-based composite material has been used to make RF capacitor laminates (to compete with ceramic chip capacitors). Using this material, we successfully achieved low DF of ~0.002 at GHz frequencies (up to 10GHz), higher dielectric strength and better TCC by optimizing size of the filler and controlling its distribution in the polymer matrix. This material can be applicable for the use either in discrete RF components or in being embedded within the packaging substrate as an embedded RF capacitor material. **PCB**

#### References

1. New 500 & 250V Multilayer Organic Capacitors (MLOCs), AVX Co., 2012.

2. P. N. Lee et al., "Design and modeling methodology of embedded passives substrate in a compact wireless connectivity module," 61<sup>st</sup> ECTC, May 31–June 3, 2011, FL USA, pp. 144–149.

3. Features and Applications of Polymer Thin Film Multi-Layer Capacitor PML CAP, Rubycon Co., 2011.

4. J. Andresakis et al., "Use of high

Dk, low loss composite material as used for embedded capacitors in high frequency applications," 41<sup>st</sup> IMAPS, USA, 2008.

5. R. Ulrich, L. Schaper, D. Nelms, and M. Leftwich, "Comparison of paraelectric and ferroelectric materials for applications as dielectrics in thin film integrated capacitors," Inter. J. Microcircuits Electron Packag., Vol. 23, 2000, pp. 172–180.

6. S. J. Monte, "Titanate Coupling Agents," in Functional Fillers for Plastics, 2<sup>nd</sup> ed., M. Xanthos, Ed. Germany: Wiley-Vch, 2010, pp. 91–114.

7. J. H. Hwang et al., "High Dk embedded capacitor materials in organic packaging substrate," 12<sup>th</sup> Electronic Circuits World Convention (ECWC12), US100, Taiwan, 2011.

8. J. Krupka et al., "Uncertainty of complex permittivity measurements by split post dielectric resonator technique," J. Europ. Ceram. Soc., Vol. 21, 2001, pp. 2673–2676.

9. S. George et al., "Dielectric mechanical, and thermal properties of low-permittivity polymer-ceramic composites for microelectronic applications," Int. J. Appl. Ceram. Technol., Vol. 7, 2010, pp. 461–474.

## **Unrivaled Speed.**

## Introducing the atg A8-16 with 16 test probes, 8 XGA color cameras, and an unrivaled test speed of up to 275 measurements per second.

| Basic specification       | 16 test probes, 8 XGA color cameras    |

|---------------------------|----------------------------------------|

| Test area                 | 610 mm x 620 mm                        |

| Smallest test point       | 25 $\mu$ m (*with micro needle probes) |

| Repeatable accuracy       | +/- 4 μm                               |

| Test voltage              | up to 1000 Volts                       |

| 4-wire Kelvin measurement | 0,25 mΩΩ - 1 kΩ (± 0,1 mΩΩ ± 2         |

A8-16 Video

Get more info

atg Luther & Maelzer GmbH Zum Schlag 3 • 97877 Wertheim • Germany Phone +49-9342-291-0 • Fax +49-9342-395 10 sales@atg-Im.com • www.atg-Im.com

## Embedded Resistors in Low Ohmic Application

#### by Daniel Brandler and Manuel Herrera

OHMEGA TECHNOLOGIES INC.

#### Summary

Industry trends of smaller, faster, more modular "plug'n play" type devices are challenging designers to find alternative interconnection methods and related technologies. Increasing I/O densities in smaller form factor devices result in the need for embedding passives within PCBs. Embedded resistors are one such technology with a long pedigree of high reliability and proven performance.

#### Introduction

The reasons for using embedded resistors are simple: size, performance, and reliability. The electronics industry continues to push the envelope of how much can be packaged into smaller and smaller areas while the speed and I/O densities of integrated circuits continues to increase. The PCB designer is faced with the daunting task of trying to route circuitry in less area while still preserving space to accommodate both active and passive devices necessary for proper system operation. This has led to a growing use of HDI boards with ultra-fine lines and buried/blind via technologies. Embedded resistors are complementary to HDI technology, with removal of passive devices from the board surface enabling more real estate for active devices and allowing shorter interconnects between the I/O and the resistive element. Other benefits of embedded resistors are reduced EMI. lower inductive reactance and greater reliability with the elimination of the surface resistor assembly and solder joint.

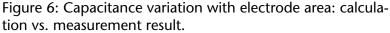

### Surface Treatment Technology CupraEtch DE – Differential Etch for SAP/MSAP

| Sheet<br>Resistivity<br>(Ω/□) | Material<br>Tolerance<br>(%) | Typical Applications                                                                                                                                                 |

|-------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                            | 3                            | Developed for series termination resistors as ORBIT <sup>®</sup> (Ohmega<br>Resistors Built In Trace) and also used for other applications, like<br>flexible heaters |

| 25                            | 5                            | Used primarily for series/parallel termination resistors and power                                                                                                   |

| 50                            | 5                            | dividers                                                                                                                                                             |

| 100                           | 5                            | Used primarily as pull-up/pull-down resistors for electronic logic circuits                                                                                          |

Table 1: Available Sheet Resistivity and Typical Applications.

Embedded resistor technology, primarily used in performance demanding military, aerospace and high density computing applications, has been increasingly used in the high-volume consumer electronics market. This migration into the consumer segment is happening because designers can use embedded resistors as a solution to tight space constraints. Embedding can free up PCB real estate, reduce via and layer counts, eliminate the need for components on the bottom side of the PCB, and eliminate common quality issues found in passive component SMT processes.

The performance benefits of embedded planar resistors can also be seen in high-frequency switching applications where the parasitic inductance of SMT components has an impact on performance. Reducing the parasitic effects improves signal quality. For this article, we are defining low-ohm values as greater than 10 ohms and less than 100 ohms. The advantage of embedded resistors in this range of resistance is realized in high-frequency data communication and front-end RF circuits.

#### **Embedded Resistor Applications**

A variety of resistor values can be achieved using embedded resistor material. The table below shows available OhmegaPly<sup>®</sup> resistor values based on type of application.

Termination resistors in high-speed digital communications are a prime application of embedded low ohm value resistors.

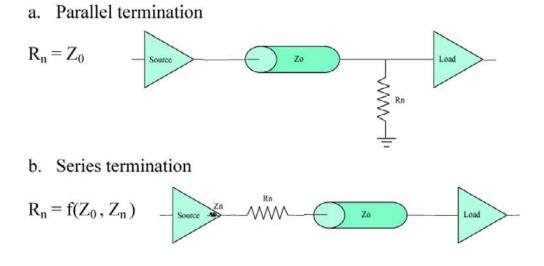

The ohmic value of any resistor  $(R_n)$  used to terminate a high-speed digital signal is a function of the device impedance  $(Z_n)$  and/or the characteristic impedance of the circuit  $(Z_0)$  as shown:

### CP 6080 LOW COST DIGITAL INK JET PRINTER

CCD CAMERA ALIGNMENT

# Girca Print

CircaPrint

- Print size up to 600 x 800mm

- Up to 2 Inkjet-Heads 8 (32) channels each

- Up to 4 Colours depending on type of ink

- Vacuum-Table for hold down of flexible materials

Grapht

- In line UV Curing

- CCD camera for accurate alignment

- Tooling pin registration

- 180 1440dpi

### LEGEND INKS • ETCH RESIST • UV BLOCK

www.circaprint.net sales@circaprint.net

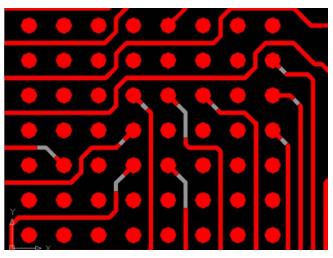

Figure 1: Example of ORBIT layout.

Terminating resistors are used to reduce signal reflection and maintain proper signal integrity. OhmegaPly embedded resistors can be placed very close to the end of the driveline, improving impedance matching and reducing line delay.

For fine-pitch BGA packages where the channel widths between the pads surrounding the interconnecting vias are insufficient for standard resistor footprint designs, resistors can be formed as part of the internal logic trace. A 10-ohm per square sheet resistivity product specifically designed for low value series termination has been used for more than 10 years in this manner.

Built-in-trace resistors simplify designs by eliminating the resistor footprints under the SMT components. The resistor width equals the trace width, but the resistor length is not limited (because the resistor can always follow the trace). Typical trace widths, and hence resistor widths, are greater than 125 µm.

With the introduction of micro-ball grid arrays (µBGAs) with pad pitches of less than 500 microns, the channel width is reduced to the point where there is insufficient space for standard built-in-trace resistor elements. Resistors with line widths less than 100 microns are required<sup>[1]</sup>.

The necessity for smaller line width resistors with good tolerances and power lead to the development of an optimized OhmegaPly alloy with improved chemical and physical stability. This improved material has the ability to create built-in-trace resistors less than 50  $\mu$ m wide. Embedded resistors within 0.3 mm pitch  $\mu$ BGA or PBGA packages are therefore achievable where line and space widths are about 40  $\mu$ m<sup>[2]</sup>.

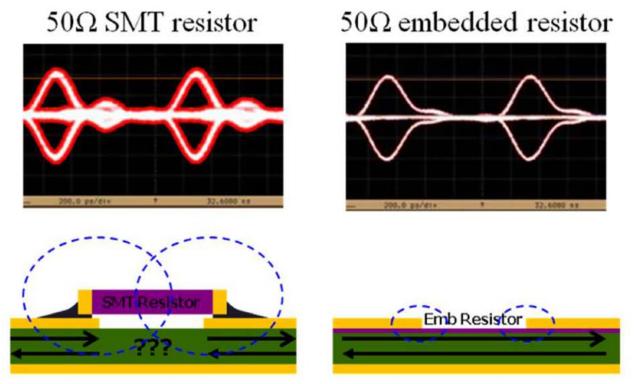

#### Embedded Resistors in Dual In-Line Memory Modules

Higher memory speeds in DIMM modules requires termination of the bus to manage ringing and reflections. Typically these termination values will be 15-55 ohms. For example, approximately 100 resistors can be embedded on a DDR3 RDIMM module and roughly 90% of those resistors are below 40 ohms<sup>[3]</sup>. The use of embedded resistors allows designers to place resistors where traditional SMT components cannot be placed. This improves signal integrity by placing the series termination or buffer resistors closer to the source and removes the restriction of placing along the board edges. A prime example of performance improvement is seen when making a qualitative comparison of noise levels on signals when using an embedded resistor and an equivalent SMT component<sup>[3]</sup>.

Embedding low-ohm resistors frees valuable board area which can result in larger memory modules by using larger DRAM chip footprints or production of a simpler board by removing the resistors from the assembly process.

Earlier this year, JEDEC released a standard for design of DDR3 204-pin unbuffered SO-DIMMS using embedded resistors<sup>[5]</sup>.

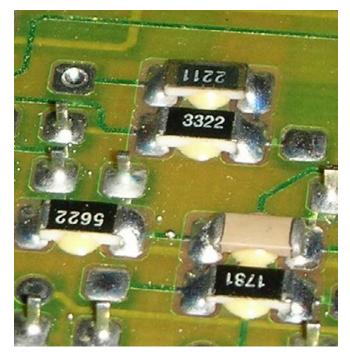

#### **Multi-Chip Modules**

Multi-chip modules commonly referred to as MCMs or SiPs are devices that combine multiple integrated circuits, semiconductor dies or other discrete components on a unifying substrate. Layout routing in such small footprints need to minimize vias and interconnections between layers. Some of the challenges of designing an MCM have been solved by using embedded resistors. Embedded termination resistors built-intraces have the benefits of improving signal integrity and eliminating the extra space for SMT resistors. Again, typical resistor values needed for impedance matching are in the range of 15–51 ohms<sup>[4]</sup>. High-speed digital and RF SiPs such

Figure 2: Signal integrity improvement with embedded resistor.

as wireless cellular and connectivity devices like Bluetooth are becoming smaller. Embedding resistors has and will continue to be an option to help designers shrink their products.

#### Conclusion

Industry trends of smaller and faster devices are challenging designers to find alternative interconnection methods and related technologies. Low-ohm embedded resistors built-in-trace are one such technology that should be added to any designer's arsenal of tools. **PCB**

#### References

1. Brandler, Daniel "The Performance of Embedded Resistors by Alloy Type and Film Thickness," The PCB Magazine, November 2011.