# THE PC August 2015 CLSSECON MAGAZINE

an ICOnnect007 publication

Failure Mode: Hole Wall Pullaway p.24

Mentor Graphics Helps Bridge Gap Between PCB and RF p.30

Failure May not be an Option, but Sometimes it's a Reality p.42

base for innovation

# THE WAR ON PROCESS FAILURE

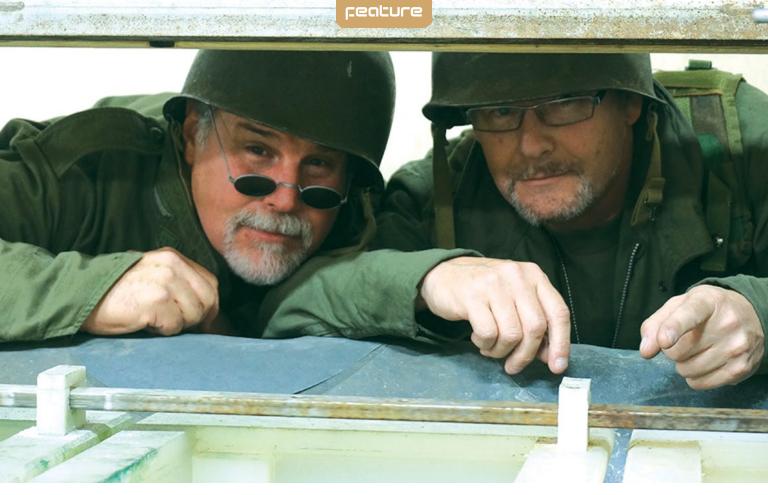

# Kelly Dack and Mark Thompson Unite in the War on Failure

by Andy Shaughnessy, page 10

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

## www.thepcblist.com

# **BOARD LEVEL** SIMULATION SPECIALISTS

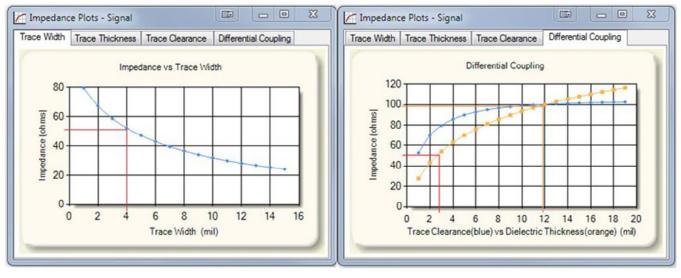

ICD Stackup Planner - offers engineers/PCB designers unprecedented simulation speed, ease of use and accuracy at an affordable price

- 2D (BEM) field solver precision

- Characteristic impedance, edge-coupled & broadside-coupled differential impedance

- Unique field solver computation of multiple differential technologies per stackup

- Heads-up impedance plots of signal and dielectric layers

- User defined dielectric materials library over 16,250 materials up to 100GHz

ICD PDN Planner - analyze multiple power supplies to maintain low impedance over entire frequency range dramatically improving product performance

- Fast AC impedance analysis with plane resonance

- Definition of plane size/shape, dielectric constant & plane separation for each on-board power supply

- Extraction of plane data from the integrated Stackup Planner

- Definition of voltage regulator, bypass/decoupling capacitors, mounting loop inductance

- Frequency range up to 100GHz

- Extensive Capacitor Library over 5,250 capacitors derived from SPICE models

## LEARN MORE

### www.icd.com.au

### **FEATURED CONTENT**

Attention! You may not realize it, but PCB designers are in a veritable war zone, day in and day out. This month, our cover story is an interview with two "soldiers" in this war on failure, Kelly Dack and Mark Thompson of Prototron. We also have feature columns by Paul Reid and Tim Haag, as well as an interview with Per Viklund and Alex Caravajal of Mentor Graphics.

### **10** Kelly Dack and Mark Thompson Unite in the War on Failure

by Andy Shaughnessy

**30** Mentor Graphics Helps Bridge Gap Between PCB and RF

by Barry Matties

### FEATURE COLUMNS

24 Failure Mode: Hole Wall Pullaway by Paul Reid

**42** Failure May not be an Option, but Sometimes it's a Reality

# **Sola** *RF/Microwave Materials & Resources*

- IS680 materials offers a complete laminate materials solution for single- and double-sided printed circuit designs and is a cost-effective alternative to PTFE and other commercial microwave materials.

- I-Tera® MT RF materials are available in 0.010", 0.020" and 0.030" in 3.38, 3.45 and 3.56 Dk.

- I-Tera® MT materials are suitable for both high-speed digital and RF/ microwave designs. A full compliment of cores and prepregs allowing flexibility in design is available in core thicknesses from 0.002" to 0.018".

- TerraGreen® halogen-free, very low-loss, thermoset materials are available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

- The revolutionary Astra® MT ultra low-loss thermoset laminates are a replacement for PTFE. These materials have been used for hybrid applications with Isola's 185HR and 370HR products.

|                                                         | RF/MICROWAVE MATERIALS                   |                                            |                        |                 |                 |  |

|---------------------------------------------------------|------------------------------------------|--------------------------------------------|------------------------|-----------------|-----------------|--|

|                                                         | <b>IS680</b>                             | I-Tera® MT RF                              | I-Tera <sup>®</sup> MT | TerraGreen®     | Astra® MT       |  |

| Tg                                                      | 200°C                                    | 200°C                                      | 200°C                  | 200°C           | 200°C           |  |

| Td                                                      | 360°C                                    | 360°C                                      | 360°C                  | 390°C           | 360°C           |  |

| Dk @ 10 GHz                                             | 2.80 - 3.45                              | 3.38, 3.45 & 3.56                          | 3.45*                  | 3.45*           | 3.00            |  |

| Df @ 10 GHz                                             | 0.0028 - 0.0036                          | 0.0028, 0.0031 & 0.0031*<br>0.0034 0.0031* |                        | 0.0030*         | 0.0017          |  |

| CTE Z-axis (50 to 260°C)                                | 2.90%                                    | 2.80%                                      | 2.80%                  | 2.90%           | 2.90%           |  |

| T-260 & T-288                                           | >60                                      | >60                                        | >60                    | >60             | >60             |  |

| Halogen free                                            | No                                       | No                                         | No                     | Yes             | No              |  |

| VLP-2 (2 micron Rz copper)                              | Available                                | Available                                  | Available              | Standard        | Standard        |  |

| Stable Dk & Df over the temperature range               | -55°C to +125°C                          | -55°C to +125°C                            | -55°C to +125°C        | -55°C to +125°C | -40°C to +140°C |  |

| Optimized global constructions for Pb-free assembly     | Yes                                      | Yes                                        | Yes                    | Yes             | Yes             |  |

| Compatible with other Isola products for hybrid designs | For use in double-<br>sided applications | Yes                                        | Yes                    | Yes             | Yes             |  |

| Low PIM < -155 dBc                                      | Yes                                      | Yes                                        | Yes                    | Yes             | Yes             |  |

\* Dk & Df are dependent on resin content NOTE: Dk/Df is at one resin %. Please refer to the lsola website for a complete list of Dk/Df values. The data, while believed to be accurate & based on analytical methods considered to be reliable, is for information purpos only. Any sales of these products will be governed by the terms & conditions of the agreement under which they are sold.

### **RF Conversion Service**

- Isola's Design Review Service can facilitate your conversion to Isola's RF/microwave products and get you to market faster with the newest, ultra-low-loss materials.

- As part of this new service, Isola's technical staff will provide turn-key calculations, testing, characterizations and material recommendations to assist PCB fabricators and OEMs in converting to Isola's RF-materials, which will help overcome the current material shortages of other vendors and accelerate time-to-market. The design review service will also address the perceived conversion issues when migrating from a currently used material to an Isola material.

#### http://www.isola-group.com/conversion-service

#### **FREE! Impedance and Power-Handling Calculator**

- Isola's free Impedance and Power-Handling Calculator predicts the design attributes for microstrips and striplines based on the design's target impedance and dielectric properties of the company's RF, microwave and millimeter-wave laminate materials.

- This software tool provides a design or an equivalent dielectric constant to facilitate modeling for PCB designers to predict impedance and other design attributes. The software computes changes in the effective dielectric constant due to dispersion at higher frequencies. The software then computes the total insertion loss a measure of power lost through heat for power handling calculations, including the dielectric loss, conductor loss, and the loss due to the surface roughness. The main factors affecting the typical power-handling capability of a material are its thermal conductivity, the maximum operating temperature, and the total insertion loss.

#### https://isodesign.isola-group.com/phi-calculator

# www.isola-group.com/RF

Isola, I-Tera, TerraGreen, Astra and IsoDesign and the Isola logo are registered trademarks of ISOLA USA Corp. in the U.S.A. and other countries. All othe trademarks mentioned herein are property of their respective companies. Copyright © 2015 Isola Group. All rights reserved. AUGUST 2015

VOLUME 4

NUMBER 8

thepcbdesignmagazine.com

an IConnect007 publication

THE OPTIMUM MAGAZINE DEDICATED TO

PCB DESIGN

### CONTENTS

58 Training the Next-Generation Engineer: When Does it Begin and End? by Tom O'Connor

### COLUMNS

8 Fighting the War on Failure by Andy Shaughnessy

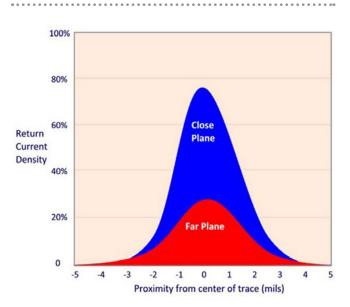

- 46 Stackup Planning, Part 3 by Barry Olney

- Corder

- 54 A Brief Overview of High-Frequency Laminates by John Coonrod

### SHORTS

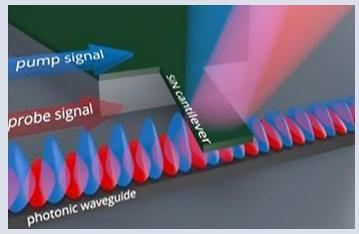

45 Physicists Develop Ultrasensitive Nanomechanical Biosensor

51 Protective Shells May Boost Silicon Lithium-ion Batteries

- HIGHLIGHTS

- 40 PCB007

- 52 MilAero007

- 64 PCBDesign007

### EXTRAS

- 66 Events Calendar

- 67 Advertiser Index & Masthead

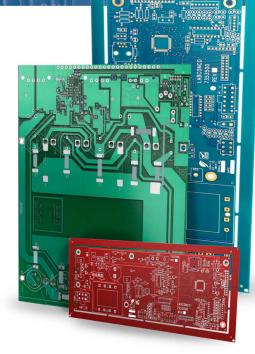

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits<sup>®</sup> is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

### Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

#### THE SHAUGHNESSY REPORT

# **Fighting the War on Failure**

by Andy Shaughnessy I-CONNECT007

In this issue, we focus on the "War on Failure," a war that your company is likely already prosecuting. The big question is this: Can we ever win this war?

No one in this industry sets out to fail, except failure analysis test engineers. But failure is a part of life for designers and manufacturers of electronics. Our reader surveys show that failure affects nearly everyone in the PCB industry: designers, fabricators, assembly providers, OEMs, and suppliers.

And failure itself is difficult to define; everyone has a different definition.

Even the meaning of "failure" seems to evolve over time. Think about this: The PCB design process of the past would be considered a failure today. Decades ago, many PCB designs went through multiple design iterations and board re-spins. No one labeled those actions as failures; it's just the way the process worked back then.

There was no hand-wringing about it, no post-mortem meetings full of downcast faces, wondering what went wrong. That was the accepted practice. I bet design managers included these multiple steps in their department's flow charts.

Multiple iterations and board re-spins weren't an issue until price and time-to-market made them an issue. Once high-speed PCBs became the norm, doing redesigns and building prototype after prototype was no longer financially feasible. Design teams began using simulation and analysis, the "right the first time" movement took off, and now we look at the old way as a failure.

#### the shoughnessy report

#### FIGHTING THE WAR ON FAILURE continues

The same holds true for PCB fabrication and assembly providers. The scrap rates of the past would run a company out of business today. Now, manufacturers are adopting processes like Lean and Six Sigma to help eliminate as much waste as humanly possible. Six Sigma's 99.997% rate of perfection is no longer considered an unattainable dream.

#### What Does Failure Mean to You?

That was one of the first questions I posed in our cover story interview, "Kelly Dack and Mark Thompson Unite in the War on Failure." Kelly and Mark come from design and CAM backgrounds, respectively, and they've teamed up in this ongoing battle. In this interview, they discuss their definition of failure, some of the more common failures they see from their perspectives, and a variety of ways to keep failures to a minimum. But as they point out, we'll probably never eliminate failure completely from the PCB industry.

Paul Reid's feature column, "Failure Mode: Hole Wall Pullaway," details how stress-relieving and stress-inducing HWPA can cause copper plating in a plated through-hole to be pulled away from the dielectric of the hole wall. As usual, Paul brought along a few of his super cool cross-section animations that show these defects as they happen.

In Tim Haag's feature column, "Failure May Not be an Option, But Sometimes it's a Reality," he discusses some of the mistakes, miscues, and missteps that are common among PCB designers. Working off the famous line by Ed Harris' character in Apollo 13, "Failure is not an option," Tim explores everything from not using all of your EDA tool's inherent capabilities to using far too much automation.

In "Mentor Graphics Helps Bridge Gap between PCB and RF," Barry Matties interviews Per Viklund, director of IC packaging and RF product lines for Mentor, and Business Development Manager Alex Caravajal. Per and Alex explain how Mentor is helping bring together the RF and PCB design worlds, and their plans to accelerate the RF design cycle.

We also bring you the latest in columnist Barry Olney's continuing series, "Stackup Planning, Part 3." This month, Barry looks into

stackup configurations for high layer-count, high-speed PCBs, with some stackup tricks for eight-layer designs.

Columnist John Coonrod offers a "Brief Overview of High-Frequency Laminates," explaining their moisture absorption challenges, thermal properties, and thickness control. He also addresses the use of special fillers to achieve good CTE values and greater stability.

DfR Solutions' Tom O'Connor offers an update on the ongoing shortage of engineers graduating in North America in "Training the Next-Generation Engineer: When Does it Begin and End?" Tom focuses on the efforts to attract more smart young students to the STEM disciplines, and the need to jump-start these efforts right now, before it's too late.

This month, our sister magazines <u>The PCB</u> <u>Magazine</u> and <u>SMT Magazine</u> also focus on the war on failure from their perspectives, so don't forget to check them out.

I'll see you next month, when we devote the September issue to automotive electronic design. Enjoy the last of your summer—show time is around the corner! **PCBDESIGN**

**Andy Shaughnessy** is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 16 years. He can be reached by clicking here.

# Kelly Dack and Mark Thompson Unite in the War on Failure

by Andy Shaughnessy PCBDESIGN007

There's been a lot of talk about fighting the war on failure in the PCB industry. But what strategies should our generals follow to prosecute this war? What exactly constitutes a failure in the first place? Is this war even winnable? I recently spoke with longtime designer Kelly Dack and CAM support veteran Mark Thompson of Prototron Circuits about the best battle plans for beating failure, and why designers and manufacturers must team up against this common enemy.

**Andy Shaughnessy:** Kelly, you recently said, "Failure wins when it leverages the guerrilla warfare tactic of divide and conquer to confuse and disorient the product development community. Designers and manufacturers must unite to fight this war." Why don't you start off by saying what failure means to each of you at the design stage and at the board shop stage?

**Kelly Dack:** Andy, failure is defined as not meeting the intended objective. But I think the concept is easily confused if coming from isolated design and manufacturing perspectives. Meeting the intended objective successfully can only come from allied efforts. Designers need to describe or define objectives for their projects in terms of concise orders in order to make successful products, but this will only come about if the folks giving orders are also able to follow orders.

*Mark Thompson:* Absolutely, I agree with Kelly entirely. I'd say from the fabrication side, following orders is easy if the orders are given from time-proven, industry standard speci-

# Ventec at your fingertips.

**K**Back

STANDARD FRA

Direct access to all the news and technical

updates from Ventec is now at your fingertips thanks to the user-friendly new Ventec app, which gives up-to-the-minute information on all developments, ongoing projects, appointments and technical data updates from Ventec International Group.

With this free app, you can:

- Get the latest news from all of Ventec's operations worldwide

- Access the latest datasheets and process guidelines

- Be notified when new datasheets are available for download

# **Download yours today!**

Download on the App Store

Wherever technology takes you, **we deliver.**

Ventec Europe www.ventec-europe.com

ventec

Ventec USA www.ventec-usa.com Ventec International Group www.venteclaminates.com

ATEST

fication. We open the door for failure when we have to question orders. But we manufacturers have to occasionally, when the orders are outside of the guidelines of conventional process or machine capability. Designer and manufacturer communication and respect is key here, and I think this is why Kelly mentions that it is important that those giving orders must be willing to take them if the order would put the part at risk of failure.

and the

#### **Shaughnessy:** Is failure always someone's fault or is it the fault of a bad process, or is it a combination of both?

Dack: I'm not comfortable pointing fingers at individuals. The causes for success and failure can be attributed to people, but it can also be caused by unforeseen conditions or even acts of God. A good strategy is to identify performance requirements and operating conditions. The "battle plan" needs to identify constraints: design constraints, manufacturing constraints, performance constraints, even cost constraints. Knowing the enemy and anticipating every possible way a design could possibly fail is crucial, but it can't happen in a vacuum. It must occur through open communication with the allies - stakeholders of the product who are connected through the process steps.

**Thompson:** If you're asking if every failure is someone's fault, I would say yes, at the most base level. It will always turn out to be someone's fault either due to negligence or lack of vigilance. But, as Kelly said, there are extenuating circumstances. There can be dynamic situations where environmental, human or mechanical conditions create a failure in the field. Or it could be a poor design type of situation, where something wasn't properly considered in the original design phase. It's a good time to draw in the metaphor of a combat unit here. No one person in a combat unit takes credit for the unit's success or failure. They are a team!

122

**Dack:** Oh, yes. I like that analogy! A combat unit trains and rehearses their craft to work with other units successfully on the battle-field. A big part of their success is adherence to standards. Standard equipment, weapons and communication is so important! Without standards, orders are non-effective SNAFU. Mentioning standards at this point at least helps to move the question from who failed to how it failed, which is much more important from a process perspective.

**Shaughnessy:** In your positions, you've both had the experience of seeing a lot of things fail over the years. I wonder if you guys can talk about some of the more prevalent types of failures that you've seen in design and fab. By the way, in our recent survey, we asked our design readers what they thought was the No. 1 cause of failure in the field. A good chunk of the readers said, "Solder joint failure," and an equal number said, "Bad design techniques."

**Thompson:** I think the survey results are telling. When you ask about what are some of the more common failures in design and fab, and you find that the results vary from bad design to solder failure with a good smattering of both, that really tells you something

# Will your idea be the next big thing?

We can help you bring your idea to life ...and deliver it 40-50% less expensively than other service providers!

We are a group of over 200 experienced independent engineers that see a need for a more cost effective solution for you. Whether you just need a PCB layout or full tunrkey product development, we can help you get it done ...FAST!

To learn more, click on one of the services below!

www.fastinterconnect.com | sales@fastinterconnect.com

about what's going on in the business. It shows that designers are more aware. This is good news because it is showing that designers are taking note of what the manufacturing industry is finding though the process of "failure analysis" utilizing cross-sections, X-rays, ionic contamination and a lot more. The results are not being ignored.

**Dack:** On the front-end, the cause of many common failures can easily be caught by checking. There are so many failures that can be attributed to poor design checking. Discontinuity between the schematic and netlist in the layout; failure to edit nodes properly; forgetting to change a solder mask color; forgetting to flood a power plane could cause a huge failure. But a lot of these common problems are easily prevented by a check process.

Thompson: I definitely agree. I see that people are making more progress in this respect. A lot of our customers, for instance, are now supplying an IPC netlist when they didn't in the past. This form of communication helps our war on failure by comparing the design connectivity orders with exported, graphical Gerber data orders prior to making any edits whatsoever. So, let's bring in another military metaphor: friendly fire. A lot of people, when they're brand new at generating netlists, will do silly things like assign fiducials as net points or non-plated holes as net points. Some do not realize that the design may have half-plated pads at the part edge that are creating a connection with a metal post at some point later in its life. Having to interpret and resolve design dicontinuities without a code talker, is like dodging friendly fire.

Not resolving a connectivity issue, even though it looks perfect can be like stepping on your own team's landmine.

**Shaughnessy:** We also see a lot of designers who are over-constraining their designs and making them too high-tech.

**Thompson:** Absolutely. Many people rope themselves in with these specifications. I've seen so many drawings that will call out very specific material types, very specific dielectric values and even very specific dielectric constants. This is really a problem. If you go to shop X, they may have a flavor of 4101/126 that has a different dielectric constant, a different environmental condition, and a different lamination process and parameter that's different from shop X, shop Y, and shop Z, all the way down the road. If you make a drawing and you roped yourself into a specific material type or a specific dielectric constant, you're really doing yourself a disservice.

**Dack:** What Mark is talking about is overspecifying. Overspecifying can cause failure at the front-end manufacturing process by limiting sources who can manufacture the part.

**Thompson:** Kelly and I did a tour yesterday and we brought up that very point. We were talking about how sometimes people go on a tangent because it's the new thing to do.

I hear customers saying, "We have to have ENEPIG because we have to have EN-EPIG. We don't really care about the surface finish. We don't have any constraints or ap-

# **IT'S FULLY CAPABLE AFFORDABLY PRICED TOTALLY SCALABLE AND TRUTH BE TOLD** THERE'S NOTHING **STANDARD ABOUT IT**

# **OrCAD PCB Designer Standard**

When your standards are incredibly high, even your standard software is exceptional. OrCAD<sup>®</sup> PCB Designer Standard combines cutting edge capabilities with tremendous user value making it an intelligent choice for startups and entreprenuers. Industry standard schematic capture, PCB editing, and mechanical collaboration all come standard for as little as \$1300. OrCAD PCB Designer Standard gets your project started on a solid foundation with the scalable design tools that can grow with your business.

See how affordable OrCAD can be: Learn More >

plication issues based on surface finish and we don't have any assembly issues based on surface finish, but, gee, it's the most popular thing, so I think we're going to jump on that bandwagon." This happens with surprising frequency.

100

19

14

Blind and buried vias can be of the same nature as well. Boy, there was a time in this industry where it seemed that was the vogue way of dealing with tight-pitch areas and breaking out of very fine-pitched land patterns. The "only" solutions were blinds and burieds. Now, people are realizing, "Well, that's not necessarily true." Now, we can have the best of all worlds on the same board and still be able to deal with fabrication constraints. They don't have to go down to the absolutely crazy 2x2 mil design pitch limiting them to only a very few manufacturers here in the United States.

# **Shaughnessy:** So, how do we prevent failure? Does it start with communication?

**Dack:** Yeah, most definitely. As design and manufacturing allies, we need to provide a united front against failure. This needs to be done through communication, with every-one speaking the same code. Our communication vehicles are design data, documentation along with manufacturing and inspection data. These are the only proven methods to check and verify our manufacturing result meets our design intent.

**Thompson:** I think, very simply, it comes down to due diligence and continuous quality improvement. As you evolve in your continuous quality improvement plan, one would hope that any violations or consistent things that you're tracking, if you're finding something that's continuously an issue or if you have three weeks of low copper or three weeks of low gold, obviously, the intent of the system is that, at that point, you can issue a corrective action, permanently correct that and then move forward.

Hell Color

(PP)

Ultimately, what we're looking for when we're talking about charting and tracking these things is, if I could look at a year's worth of data and everything was very sporadic and few and far between, I'd say we're probably doing pretty well with our quality system. If I have three weeks of the same type of anomaly, clearly we have some issues.

**Dack:** Mark comes from a manufacturing background. I'm always very impressed by manufacturers and the data that they keep regarding their processes. If a failure occurs, a manufacturer is expected to be able to point to their travelers and inspection reports and tell a customer exactly where and how the failure occurred. I think we as designers need to take note the next time we request that corrective action report. Do designers have design processes in place where we check and verify that our design and layout meets the intended design constraints and design specifications? Do we check for those before we ever send design data to the manufacturer? If we don't, isn't that a lot like being really good at giving orders without being able to take them?

I'd like to give a nod to a wonderful group manager I worked for over the past couple

# Solutions to Ensure PCB Manufacturing Success!

# CAM350

Verify and Optimize PCB Designs for Successful Manufacturing.

# BluePrint PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

# For more information please visit downstreamtech.com or call 800-535-3226.

State of the state

A A A

of years at IGT in Reno, Mark Taylor. He's a four-star general in the war on failure. He introduced our PCB design workgroup to a book by Franklin Covey called "The 4 Disciplines of Execution," or the 4DX Methodology. Our group had a really extensive checklist that was so long and time-consuming it was rarely being used. Needless to say, design problems found their way onto our manufacturing assembly line. For a good year, our assembly folks tracked these errors and many more. But without an ally, the data was useless. Mark suggested we solve our ineffective checklist problem by formulating a new one based on the data collected by the assembly group. His leadership and 4DX skills helped us to win this battle. As the designers and assemblers allied together to eliminate designer induced failure, they found only five major show-stoppers that were slipping through the design process. The designers revamped their checklist to check for only those five things, kept score with the assembly team, and met each week to report on progress. Victory against failure was won in this case, by great leadership and team alliance.

No.

34

## **Shaughnessy:** Is it all about process control? Is that the key?

**Thompson:** Yes, at all levels. Process control at the design and engineering phases all the way through to fabrication and assembly. As a designer or a company going to fabrication, are you sometimes giving them too much? Is there too much for them to deal with? Are there too many caveats? Is everything 3x3, and does it need to be? Were you just ingressing and egressing out of a fine pitch part and then, all of a sudden, you decided to run the remainder of the board at 3x3?

That's where the proof is in the pudding. That's when, ultimately, your design goes into the product and they do the initial product testing and you have to go through your first set of revisions. That's when you're really starting to see what sorts of things you need to address through that process. Certainly, there are process issues on the fabrication level. They happen all the time, anything from, as you said, solder failures at an assembly due to low copper barrel cracking, heat considerations, etc. Any number of things can happen in a fabrication environment that could affect the actual physical board.

1 TY

One example that we talk about in our facility tours is how various fabricators could do the customer a disservice. Let's say you've got an impedance control job and you're at the initial testing phase and you're running high. You're running at 55 or 56 ohms for 50 ohms, so you're just out of tolerance. Now, your solder mask guy is going to say, "Give me those boards back. I can throw another coat on that and I can take it back down to 50 ohms." That is true. Now, the board comes through as another rev, it's the same impedance, and you build it right this time. You have no etching issues and you don't have to put a second coat on it.

The customer has two sets of boards in their hands. They both meet 50 ohms performance, but they have slightly different performance characteristics. Why? Because the shop played that little trick. Again, you need to be diligent about that kind of stuff. How do we do that? Mainly through site

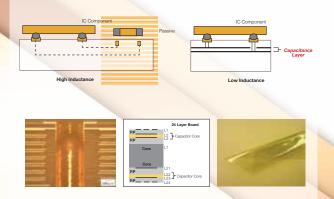

# THE SMART SOLUTION TO IMPROVE SYSTEM PERFORMANCE

# FARADFLEX ULTRA THIN MATERIALS FOR HIGHER PERFORMANCE PCBS

Faradflex is a high performance, ultra-thin laminate or resin coated copper material designed as an integral part of the PCB, module or chip package.

# FaradFlex<sup>®</sup> Improves System Performance, Price, Quality, and Reliability by:

- Reducing PCB size and/ or thickness

- Utilizing VSP Copper to provide the lowest loss signal for high speed designs

- Increasing functionality

- Improving power distribution (power integrity)

- Reducing the number of SMT Discrete Caps, Traces, Vias, Pads

- Eliminating hundreds (thousands) of SMT and etched and drilled features sites for possible failure on each PCB

For a free sample contact us at: sales@oakmitsui.com or call us at 503-313-1905

EMBEDDED CAPACITANCE

For more information, visit www.faradflex.com

inspections and better qualifications. As an end user, we always encourage you to come to the fabrication level and actually dig through their process and look at what they're doing as far as everything from the daily titrations in the wet process area to how they deal with certain aspects of design in the CAM stage.

**Shaughnessy:** It's funny you mentioned site visits. I ask designers all the time when they last visited a board shop. About half of them say, "20 years ago," and the rest say, "Never."

**Thompson:** It's been too long. The gentleman we had in yesterday for a tour is a great example. He's an old dog, an owner of four local companies that we've built boards for all these years. He came in and he'd never been on a tour. At the end of the tour, he said to me, "You know, things haven't really changed in the last 20 years. It's the way you deal with them." That was a very critical statement. That's absolutely true. How do we deal with defined geometries, 0.1 millimeter lines and spaces? Everything five years ago was 8x8 and dealing with 14 mil holes. There was a whole lot of tolerance involved. Now, you have so much less tolerance.

**Shaughnessy:** Right. Are you seeing that people seem to be a little more educated now because there are so many classes and webinars and seminars and all these things that are available in design and manufacturing? Are you seeing that people are a little more informed now than they used to be?

**Dack:** Education—or metaphorically, intelligence—is one of the defense strategies that we can employ in the war on failure. Historically, there has not been enough education, especially formal education, in the area of printed circuit board design. A sad result of this lack of formal education is designer failure due to intellectual inbreeding within a company culture. This happens in an engineering department when "good ol' boy knowledge" is passed on from designer to designer with a process methodology of "that's the way we've always done it." Well, the technology is changing fast and without outside knowledge about how everyone else is doing it, good ol' boys will not keep up! Designers are doomed to fail if they design in a vacuum.

In the war on failure, communication and education are critical. There are many sources for education that have evolved and have come about over the years. IPC has been key in educating and organizing designers in the ways of process, design and manufacturing specification through the Designers Council. There are training companies which exist like the widely known EPTAC organization, who is in the business of training and certification in the areas of these specifications, including designer certification or CID.

# **Shaughnessy:** It's also a good networking opportunity to go to any of these conferences like DesignCon, PCB West or the design forum at APEX.

**Thompson:** Absolutely, we've seen huge value in the things like Kelly was talking about, like IPC's Certified Interconnect Designer

### It's not what you DON'T know that is hurting your business... it's what you "know" that *ISN'T SO!*

# **ATTENTION LEADERS & MANAGERS**

Join us in Oceanside, CA for one of these amazing LIVE workshops.

The Four New Agreements for Leaders & Managers Wednesday – 8:30 AM to 5:00 PM (PDT)

The Four New Agreements for Leaders & Managers Wednesday – 8:30 AM to 5:00 PM (PDT)

*Early Bird Special pricing available until Sept. 7th. Bring a friend for half price!*

Are you curious about what things you are doing that may be hurting your business? Do you want proven effective solutions to the problems keeping you up at night? Join us for fast-paced, experiential learning that will have you buzzing with new ideas and systems-based possibilities—a leader's or manager's best friend. Take your business to the next level with amazing new tools based on Nobel Prize winning science...*Sign up today!*

### Creating High-Performance, Systems-Based, Conscious Business Cultures Fast - Simple - Sustainable - Proven Results

For 25 years we have been doing Four New Agreements consulting and training, significantly improving businesses. This stuff really works! —David Dibble

more info

more info

100

program, the boot camps that are set up by various end-users to educate their people, and physical classes at APEX where you can actually see people like Gary Ferrari or Rick Hartley and listen to them and understand what it is that they're talking about. Things like PCB West and DesignCon, where you have specific forums where people and classes at those shows deal with this kind of stuff.

and the

I would also add things like my blog "The Bare Board Truth" on LinkedIn, our very own LinkedIn forum that is used for networking, and also your local IPC Designers Council. We highly encourage anybody to get an IPC Designers Council started in their area because, at some point, it takes on a life of its own, and problem solving is within the group. It's very, very helpful and certainly mitigates failure.

**Shaughnessy:** I guess the war on failure, from our standpoint, is never really over, is it? I mean, you're not going to win the war, but you can manage it.

**Thompson:** The fact that we've got some new people in the industry and there are training issues at that level is certainly part of this. Let's not forget that right now, in our industry, we're looking at a lot of young fresh, recruits. Young EEs from the universities. Some of them are starting with large design bureaus and being mentored by old dogs who have methodologies from old times. I can't tell you how many times a new recruit will call and say, "I've got an 8-layer board. I want impedances on layers 1, 3, 6 and 8. They're 50 & 100 ohms. Send me your calculations and send me a stack up." Now, we are glad to send the stackup based on the orders given,

and we do. But we try not to get frustrated when it is apparent that the new recruit was just following orders when the job lands in CAM with the old dog's trick of flooding copper planes to within .005" of the traces, inducing coplanar coupling and messing up all of our given stackup calculations. So we manage the war first by showing respect to our veterans. If they will listen, we take every opportunity to give them the information they need to be able to continue with their board.

17

**Dack:** It's a great topic. The war on failure has so many metaphors relating to design and manufacturing. What we are about are our defense strategies. Like we said before, failure wins only if the allied strategies of communication and education obliterate the axis tactics of division and isolation in the design and manufacturing cultures.

**Shaughnessy:** At least if the designers communicate with fabricators and with the assembly guys, and if everybody communicates, you may not eliminate all the failures, but you'll certainly be able to manage it better.

**Dack:** The war on failure is inevitable because failure will not relent. Failure is a force.

**Thompson:** Losing the war on failure is not healthy for designers, manufacturers and other living things.

**Shaughnessy:** All right. Thanks so much for joining me today guys. **PCBDESIGN**

| ST      | AND | ARD | PRI | NTED                  | CIRCUITS |

|---------|-----|-----|-----|-----------------------|----------|

| 3.52.52 |     |     |     | and the second second |          |

Sherburne, New York, U.S.A.

| Overview Contact Specs About Videos Photos Bro | ochures News |

|------------------------------------------------|--------------|

|------------------------------------------------|--------------|

Standard specializes in delivering quick turn prototypes, pre-production and medium volume production orders, on time, and with the highest level of commitment to our customers. Our products include 1-14 layers utilizing standard FR4, High Temperature, and RF materials.

| Markets:        | Communication, Computers, Military/Aerospace        |  |  |

|-----------------|-----------------------------------------------------|--|--|

| Board Types:    | Single-sided, Double-sided, Multilayer              |  |  |

| Mfg Volumes:    | Prototype, Small                                    |  |  |

| Specialties:    | Other: Microwave, High Speed, High Temp             |  |  |

| Certifications: | IAS-9100, ISO 9001, ITAR registered, ROHS compliant |  |  |

Standard Printed Circuits, Inc.

### Click here to see a demo

### Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- News, web and contact links

## www.thepcblist.com

Click to see a partial list of registered OEMs!

#### **REID ON RELIABILITY**

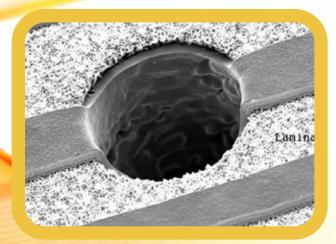

# **Failure Mode: Hole Wall Pullaway**

#### by Paul Reid

CONSULTANT

Hole wall pullaway (HWPA) is an insidious defect that is not usually a cause of electrical failure. What happens with HWPA is that the copper plating in a plated through-hole (PTH) is pulled away from the dielectric of the drilled hole wall. The hole must not be filled with any sort of a hole fill in order to see HWPA.

There are two distinct types of HWPA: stress-relieving and stress-inducing. In stressrelieving HWPA, the condition appears to distress the PTH, allowing it to survive hundreds or thousands of thermal cycles without failure. In stress-inducing HWPA, the stress appears to greatly increase, causing the PTH to fail in just a few thermal cycles. What we consider a failure is an increase greater than 10% in the overall resistance in the circuit. A crack that partially bridges the copper at the internal interface is enough to cause a failure.

This column is based on my experience in test reliability of interconnect stress test (IST) coupons. I am addressing HWPA that has moderate to severe outgassing. There may be HWPA due to thermal stressing of the board without any significant outgassing, but this type of HWPA is subtle, and it presents as a dark line between the plating and the dielectric of the hole wall. This type of HWPA is rarely detected.

#### **Stress-Relieving HWPA**

Stress-relieving is the most common type of HWPA. It appears that the adhesion of copper plating to the dielectric is reduced most likely due to problems with the application of electroless copper plating adhering to the dielectric of the hole wall. At the same time, the adhesion is strong at the copper's internal interconnection. In fact, experience suggests that the adhesion of the electroless copper is stronger than the copper plating. This process frequently produces strong interconnections to copper inner layers.

# Feel Free to Think **BIG.**..We'll Take it From There

Trust our experienced team of Electrical Engineers to take your ideas and specifications and efficiently create your product from concept to prototype assemblies. In fact, we love a good challenge, so *bring it on!*

- Complete Engineering & Project Management

- Circuit / Schematic Design & Analysis

- Power / Voltage Drop Analysis

- Component Analysis / Evaluation

- Mechanical Engineering

- PCB Layout Team Available 24/7

- Largest Privately Owned, Independent Service Provider in the USA

### **REQUEST A QUOTE**

Freedom CAD Services, Inc. HQ, Nashua, NH (603) 864-1300 Sales: • (714) 490-7600 Tustin, CA

- (408) 529-0563 San Jose, CA

- (603) 864-1342 Apopka, FL

PCB DESIGN • ELECTRICAL ENGINEERING • MECHANICAL DESIGN • SCHEMATIC CAPTURE • TURNKEY MFG.

www.freedomcad.com

#### reid on reliability

#### FAILURE MODE: HOLE WALL PULLAWAY continues

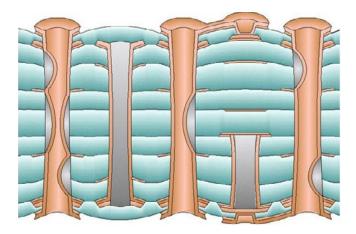

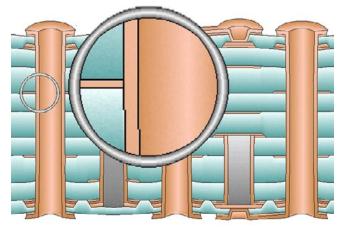

Figure 1: Graphic of stress-relieving HWPA.

This condition may result in a hole wall that looks like a stack of forward or backward "Ds" running the length of the hole where the top and the bottom of the "Ds" is at a internal interconnect (Figure 1).

I have tested holes with HWPA that have survived for thousands of thermal cycles tested from ambient to 150°C. It appears that 99% of the time this HWPA stress relieves the copper plating in the PTH, making the hole more robust to thermal cycling types of failures.

Now, when I say that HWPA stress relieves the copper plating in the PTH, thus making the hole more robust to thermal cycling types of failures, what I mean is this: When the samples are tested and the thermal cycles to failure are compared, coupons with HWPA typically outperform coupons without HWPA. This is with coupons that are from the same process that happen to have HWPA vs. those without HWPA. It appears that the coupons without HWPA have wear-out failures, while those with HWPA don't succumb to wear-out type of failures. What I think happens is that the majority of the wear-out failures propagate from a glass fiber. The crack forms slowly, starting from a glass fiber, and works its way across the copper of the barrel, with each successive thermal cycle. With HWPA we do not have the glass fibers constrained in the copper and the hole wall is free to expand and contract without encumbrances, and because of this no wear-out type of failures ensue.

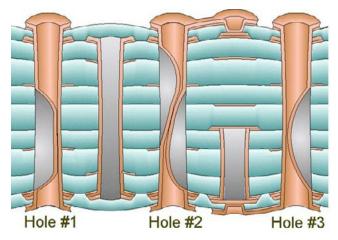

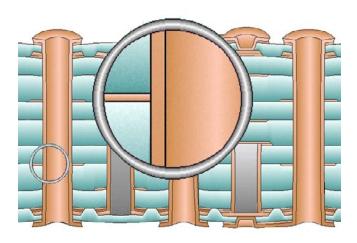

Figure 2: Graphic of stress-inducing HWPA.

#### **Stress-Inducing HWPA**

We rarely see HWPA cause an electrical failure, but on occasion this condition may cause a catastrophic failure. I call this condition stressinducing HWPA. If it is severe enough the HWPA may put enough stress on the interconnect to cause it to pull away from the copper plating in the hole. The result is a break between the internal interconnection and plating in the hole. A crack develops between the internal interconnection and the copper plating that widens in to an open. On this rare occasion, the bond is weak between the internal interconnection and the copper plating of the hole wall, or there is extreme out-gassing that causes the internal interface to crack. When HWPA is severe, it usually goes open within 100 thermal cycles.

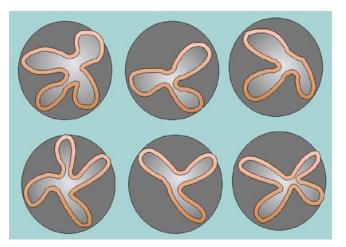

Note that in the graphic of stress-inducing HWPA the copper in the hole wall is not deformed uniformly. In hole No. 1, the pullaway is from the wall on the left side of the hole and bridges the gap so that it is pressed against the right side of the hole. In hole No. 2, the deformation is equal from both sides and in hole No. 3, the right side of the hole is deformed to touch the left side of the hole. The question becomes, what is going on in this section? To understand what was happening, we decided to do a horizontal cross-section.

What we found was surprising. The hole walls were deformed into three or four cusps. It appeared that the three or four cusps roughly aligned with the wrap or weft of the glass bun-

# Engineering And Providing Balanced Interconnect Solutions

### Flexible Printed Circuits • Rigid Flex • Wire Harnesses • Complete Assemblies

Our products and services are specifically designed to empower our customers to produce a product with superior performance and quality, as well as lower design, assembly, and system installation costs.

### Partnering With Your Engineering Team To Deliver The Best Solution

...connecting technology

Miraco, Inc. • 102 Maple Street, Manchester, NH 03103 • miracoinc.com 603-665-9449 • Fax: 603-665-9459

#### reid on reliability

#### FAILURE MODE: HOLE WALL PULLAWAY continues

Figure 3: Horizontal cross-section of stressinducing HWPA.

dles. The angle of the grind would determine what was presented in the cross-section.

I once experienced this type of out-gassing. When I worked for a board shop in New England (which will not be named), we had a special team that was supposed to move critical orders through the shop quickly. The team had a critical job, but they wanted to go to lunch when the boards were in the middle of the wet process line. They figured that it would be all right to hold the board in the sulfuric acid bath while they went to lunch. They were gone about an hour.

This worked well for the copper because a mixture of sulfuric acid can reduce copper oxide and will not attach metal copper, but it was not so good for the dielectric. The team returned and finished the process. The next day the boards were delivered to the customer. During assembly, they noticed that when the boards were soldered, a geyser of white smoke would push up through the solder and continue to smoke for as long as the soldering iron was applied to the hole. I'll never forget this condition because, under a microscope, these holes looked like little erupting volcanos.

The two animations in Figures 4 and 5 depict both types of HWPA. Figure 4 shows a stress-relieving HWPA forming. Please note that the outgassing is not as severe in this type of HWPA and the coupons survived for hundreds of thermal cycles.

Figure 4: Animation depicting stress-relieving HWPA. <u>Click to view animation</u>.

Figure 5: Animation showing out-gassing due to stress-inducing HWPA. <u>Click to view animation</u>.

The animation in Figure 5 shows the severe out-gassing of stress-inducing HWPA. The hole wall is deformed to the point that the copper is pushed all the way to the other side of the hole. The failure is an interconnect type of failure. These coupons failed in fewer than 100 thermal cycles. **PCBDESIGN**

**Paul Reid** is retired, but open to suggestions. To contact him, <u>click here</u>.

# PULSONIX

# The Price to Performance Leader for PCB Design Software

Scalable products to suit your design requirements

Import Designs and Libraries from all major tools

From stand alone PC to complete company integration

We estimate that Pulsonix has improved our efficiency in the Electronic Design department by approximately 50%. Pulsonix' price to performance ratio is unbelievable. The amount of features and options compared to other products is unbeatable.

**Engineering Director, Leading Medical Equipment Supplier**

info@pulsonix.com www.pulsonix.com

**Download Pulsonix for Free**

77

# Mentor Graphics Helps Bridge Gap

# Between PCB and RF

**by Barry Matties** I-CONNECT007

I recently attended IMS 2015, a show that focuses primarily on RF and microwave technology. During the show, I met with Per Viklund, the director of IC packaging and RF product lines at Mentor Graphics, and Alex Caravajal, business development manager with Mentor Graphics. We talked about the challenges facing PCB designers working with RF and microwave technology, and Mentor's efforts to help reduce the RF design cycle time.

# **Barry Matties:** Per, please begin by giving a quick overview of what Mentor Graphics is featuring here at IMS.

**Per Viklund:** Specifically for this show, we're focusing on the RF. Our customers have told us for a long time that it takes too long to devel-

op RF circuits, especially when RF is going to be a piece of a bigger system. It's not so often that RF engineers have told us that. It's the PC board integrators who receive the RF circuit for integration and the management who sees long engineering times, lots of re-spins, that clearly says it can't be real to have these long cycles, or it can't be correct to have to do five or six iterations. There's got to be a different way. Not often will the entire engineering organization admit that there is a better way.

## **Matties:** When we talk about cycles, what sort of cycle times are we talking about?

**Viklund:** It could be different depending on if you're doing a simple project or a larger one. But we have some cycle times that can be over two months long, say, if you are doing a board for a satellite communication link or something like that. They could have very long cycles.

# STRVING FOR EXCELLENCE IN EVERYTHING WE SAY AND DO.

- Prototype to Production

- Time Critical Production

- Commitment to Customer Service

- Best Quality & Delivery Performance

- Fair and Competitive Pricing/Costs

- Rapid Response to Quote Requests

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

**Tour our Facilities**

View our Capabilities

The Absolute Best Value in High Technology Circuit Boards 847.891.5800 • www.eagle-elec.com

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

## **Matties:** As you were saying, there are many iterations.

Viklund: There are many iterations, because first you try to simulate, and it doesn't work so you try again. And that intricate process takes a long time because every time you have to send data back and forth between RF design tools and board tools and integrate and simulate and so on. It just takes a long time. You might be surprised how many people still use the ASCII files that transfer RF circuits from, for example, ADS or National Instruments Microwave Office into board tools. And when they do it that way, it becomes a dumb metal blob that the tool cannot make anything smart out of. It's just a blob; you can place it and it comes out in your fabrication data. But the problem is, every time something changes, they have to do that entire process again because there is no intelligence.

So what we try to help these companies with is to say, "Well, if you have intelligent data in your ADS or Microwave Office tool, let's try to maintain that intelligent data in a round trip." So that you can send that data into our tools and implement it into a bigger system, bigger context, but still maintain all the parametric shapes and programmable shapes that you have. You're able to set up things like tuning expressions and then, by just a push button, send the data back into ADS or Microwave Office again to analyze and make adjustments, optimize and then just send the adjustments back into our tools again. But that loop has actually proven to shorten this design cycle by more than 50% in most cases. It's significant.

#### Matties: People must be pretty excited about that.

**Viklund:** They are very excited about it. But it's hard sometimes to adapt a new methodology. If you've been doing one thing for 20 years and now suddenly we tell you to do something different, and you won't see the benefit until the middle or end of your project rather than immediately, that's challenging to people. They say, "I know I have a pretty good project. You're telling me to use a little bit of time up front." Yes, I am, and you're going to gain it back. People are more and more adapting to this.

Figure 1: Per Viklund, director of IC packaging and RF product lines at Mentor Graphics.

#### Matties: Cycle time is still the focus.

**Viklund:** It is. Cycle times and more importantly number of cycles. If you can do one cycle and you're done, that's what everybody wants to do, but there could be various reasons why you can't. Sometimes there are legit reasons that you have to do multiple things. But you don't want it to happen because you didn't understand the design from the beginning and you don't realize it until the end. You want to make sure the tools talk the same language and the design keeps its intelligence so that you don't have to redesign because you lost something in translation.

# **Matties:** If you were looking at creating the most efficient process, what advice would you give your customer?

**Viklund:** It has to be an intelligent process where your data maintains design intent and intelligence of the circuit itself. You cannot translate it into dumb graphic and then go back again, because then you've lost all the intent. So that has to be maintained.

## **Matties:** That's what you were just talking about, maintaining the access into the data.

**Viklund:** Yes, it's actually access into the data and intelligence of the data at all points. It has to be done that way. That's very important, and the other thing is that we cannot just dump the file, give it to somebody and tell them to import it. Because what we would be seeing is that every time you have file-based interfaces, one time or another a user will import the wrong version of the file and there's no way to see on the file that it's the wrong version, unless somebody realizes that the part is missing or something. You typically discover it once you build the board, and that's really extensive.

#### Matties: Dammit.

**Viklund:** Exactly, dammit. We're done with that, we don't use files anymore. We open the tools and we have them talk on an Internet channel between them. The tools are basically communicating back and forth live without files. Then they can use all the data management tools you have on either side to make sure that what you have opened is the right version.

## **Matties:** Would this be considered a cloud-based situation?

**Viklund:** No, it's not really cloud-based. It works over the Internet but it's only the two tools involved in the communication, and it's kind of important because a lot of the times the users work with classified equipment and cannot use clouds. The cloud would have to be built inside their own organization like a mini cloud. But we don't see any advantage in this because it is two sides of the same design that need to talk for a limited period of time and then they don't need that communication anymore. So the cloud really is not that beneficial.

# **Matties:** So it's residing on multiple computers at whatever step in the process it's living in, but it goes back and forth immediately?

**Viklund:** It goes back and forth. Typically you have a data management solution that makes sure you have the right version of the assigned database. That manages the work-in-progress data.

# **Matties:** When a customer comes to you, what's the greatest challenge that they're placing on you?

*Viklund:* The greatest challenge is to really cut down the design time and get rid of iterations.

## **Matties:** Are they looking for more autorouting tools?

**Viklund:** Not for RF and microwave. For highspeed digital, definitely, because designs are getting so complex that even if you can route them by hand it takes too long. We have a new router that we call the sketch router, which basically allows the designer to sketch his intention on the board and the router will allow it to magically follow those guidelines so that the end-result looks hand-routed. That's very powerful.

**Matties:** In my mind, it's like when the calculator came out. We really didn't need to know math as much as we needed to learn how to input into the machine to get the result we wanted. When I look 10 years down the road, is that what circuit design is going to look like? Calculator operators. Not to take away from the experience and expertise of a designer in any way, but it seems to me that we put in parameters and there's a lot of intelligence compiled in the database.

**Viklund:** It's definitely similar, because you have the problem now with having enough designers who have broad enough skill sets to manage these designs, so the tools will help the designers not get spread too thin. But I think we're still going to need intelligent and well educated designers. We have to outman the designer more than replacing him.

Figure 2: Alex Caravajal, business development manager at Mentor Graphics.

**Matties:** I think there's a transition, because one of the things you mentioned is that designers have been doing it for 20 years. That's indicative of the age group of a lot of designers. We've done surveys and we see a lot of them are closer to retirement years, so is there a new group of designers coming in that's going to think differently?

*Viklund:* I hope so. We're starting to see it a little bit.

#### Matties: Alex, what are your thoughts on this?

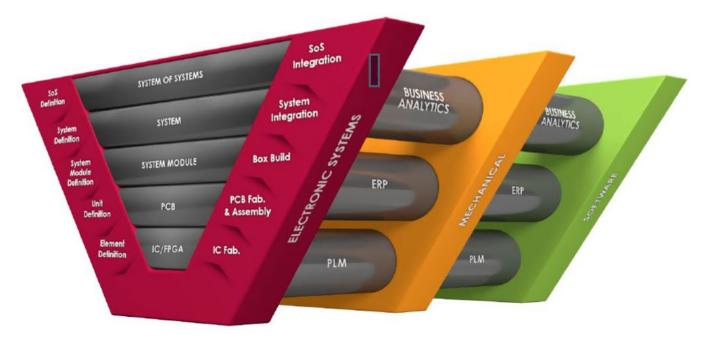

*Alex Caravajal:* Going back to that calculator discussion, I don't know if you've ever seen this kind of diagram. This is the system implementation diagram. Everything starts off with a concept and an application. The real issue is

that you go from a spec sheet, a back of napkin, and a brainstorming session, and know we have an idea. That idea needs to be implemented, so I called it the de-aggregation process. The deaggregation process takes the concept, the idea, and now implements it in terms of software/ hardware. Yes, you can build constraints, you can make specifications, and then the engineers and programmers have to interpret that. This process kind of walks you through that.

It's sort of like when you said it is kind of like a calculator, if you understand what needs to be implemented and how it needs to be tested. As we work our way in the de-aggregation from the concept through software, through the hardware, system modeling—does it meet the right cost? The right performance, the right size, and form factor? How do we define that? Then we start implementing that in PCBs, ICs, maybe some chips. When we work back, now I have chips, I have boards, and now I have to reassemble it to represent the original concept into a system. This is really what this process is. This is where the engineers live down in here.

## **Matties:** This is a process regardless of what tool you're using.

**Caravajal:** This is a process for engineering, and we layer it back to you. In the real world, it goes from the architectural implementation into the hardware implementation, and the whole supply chain that supports it. You buy chips, and you buy EDA tools from Mentor Graphics or any of our partners or our competitors for hardware implementation. This process, one way or another, has to be implemented to get from concept to a real working product, whether it's a large computer system, a smartphone or whatever.

**Matties:** Recently, we surveyed the PCB design community to ask what the greatest challenge is, and many designers said that data was their No. 1 problem. They say they don't get the data soon enough. Someone says what they need, but there's no concurrent engineering, and this looks like what you're talking about. You start at that level.

### DYMAX CONFORMAL COATINGS. BETTER PROTECTION AND HIGHER THROUGHPUT. BEYOND A SHADOW OF A DOUBT.

### LIGHT-CURE CONFORMAL COATINGS

Dymax Conformal Coatings cure in seconds with UV light – and with ambient moisture curing available for shadowed areas, you can be confident you're getting maximum protection – even underneath components. Add vivid blue fluorescing for easy inspection of coating coverage, and you'll see more throughput, in less time, using less floor space. All with unsurpassed protection against moisture, dust, chemicals, and temperature cycling. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. Visit **dymax.com/pcbcoating** to download the new *Guide to Light-Cure Conformal Coatings*.

DYMAX.COM 877-396-2988

Figure 3: Graphic showing integration of software, mechanical, and electronic systems.

**Caravajal:** Right, we start at that level, and part of what Per was talking about is a version of RF concurrent designs. Some of our most strategic partners in RF design, like Keysight Technologies, formerly Agilent and HP with the Ansys HFSS software, need these things for their engineers. They produce data, but it has to be implemented. So that connection is critical. Sometimes it's over the wall, and sometimes it's highly automated. What Per was talking about was highly automated co-design to support RF designers in a Mentor PCB flow. Then there are people who implement FPGAs, people who implement a whole system in a package. We need to be able to support concurrency across domains and different disciplines. That is a constant ongoing data and integration issue.

# **Matties:** Another big issue designers cited was not having enough real estate for the functionality requirement that's being placed on them.

**Caravajal:** You have the concept. But let's say if I wanted to use an SoC for more functionality, I could put the design functionality on a single large SoC, if possible, or a couple of SoCs, such as processor, memory, and IO, and assemble

this on a system-in-package for a targeted PCB form factor like a PC. You may also want to explore other form factors for automotive, tablets, phones and wearables. What you're really talking about is where we're going and being able to integrate the cost and performance domains from RFIC/package/board. That's kind of disruptive technology, because traditionally these design considerations are thrown over the wall.

PCB system design methodology is running into limitations going over the wall—time to market, being able to design it cost-effectively and achieve performance goals that you want. What is needed is a way to capture IC-packageboard that could have a processor, memory, RF, IO and other IP blocks. Then collect the electrical data for consideration, get it into a "design cockpit" where I can do my trade-offs and optimization. That's what we call our Mentor Xpedition Package Integrator.

Again, it's a form of concurrent design or co-design. You don't want to build something that no one can afford, so you have to think about the cost of the package. The other really burning issue that's impacting the semiconductor guys is that it's very costly to build higherdensity chips, meaning millions to hundreds of

### Heavy copper PCB – Microsection

Via in Pad Technology (Micro-via)

**10 Layers: 140µm** copper finished in each layer (4oz cu) with Buried via (L2- L9) and PTH (L1- L10)

2 Layers: 525µm copper finished in each layer (15oz cu)

With our strengths in R&D, we are capable of turning out PCBs that meet your specific requirements promptly at competitive prices. ANS is devoted to technological innovation and providing our customers with highly satisfactory and speedy service.

### www.anspcb.hk

Head office:

Factory:

ANS Industrial Co. Ltd. Kowloon, Hong Kong Tel: (852) 2757 1882

Remapp PCB (Foshan) Co.,Ltd. Guangdong Province, China Tel: (86) 757-8862 3888

Email: sales@anspcb.hk

Multi-layered aluminum board lead-free HAL

8 layer rigid-flex 30mm flexible finished thickness

### **MENTOR GRAPHICS HELPS BRIDGE GAP BETWEEN PCB AND RF** continues

millions of gates. Do we really need to do it that way? Can we possibly get the same results but kind of slice and dice it? I really could bring the memory in as a separate chip, the processor as a separate chip, and put it into a small package and accomplish the same goal at a price point, reliability point, and thermal point that we want. It's all spec-driven. If somebody comes

with a concept and says, "Here are my thermal constraints. I don't want it to burn my hip or my face, and I want it to last on a battery three days." All these things have to be gathered together, optimized, and affordable. Part of affordability is manufacturability. So we addressed that even from a manufacturing aspect. We went from concept to product going out the door and hitting the enterprise system for PLM systems.

### **Matties:** That's exactly what we're talking about, right?

**Caravajal:** Yes, and I'm using it right now for ICs, package, and boards. Per could be using this from the RF designers for the RF implementation, it's the same concept. Today we have a lot of great tools. They are domain-oriented, domain IC,

package, and board. This is about breaking down whether you want to do Internet of Things. You want more stuff in a little package and wearable and to hit all these constraints. We've got to break these walls down. Really it is exchanging data and not just pushing it one way and waiting.

## **Matties:** It's reciprocating. But you guys deal with these guys all the time. Why don't more people get this?

**Caravajal:** Very large companies that build processors and phone chips do get it. Right now, I would call it the early adopters stage. They know they have to do this because otherwise

the product they get out the door might cost too much, or may not work as well as possible.

**Matties:** If you're managing a supply chain of partners, that creates a whole different set of challenges. Are we seeing the landscape change where companies are bringing in more engineering and more manufacturing in a captive environment just to accomplish this sort of process?

Today we have a lot of great tools. They are domain-oriented, domain IC, package, and board. This is about breaking down whether you want to do Internet of Things. You want more stuff in a little package and wearable and to hit all these constraints. We've got to break these walls down. Really it is exchanging data and not just pushing it one way and waiting.

**Caravajal:** It's another form of that, right? It's concurrency and engineering data with your supply chain. Yes, all these things are trying to be optimized by what I would call world-class leaders in the semiconductor marketplace. When you think about world-class semiconductor companies, they just don't build a chip for the fact of building a chip. Intel doesn't build a processor and say, "Who wants to use this?" They build a whole ecosystem-how it fits on a board, how it thermally models, how it electrically models, and what performance level their customers need. People who build phone chips do the same thing. No more ordering it from a catalog of chips. They

have a co-design environment with their partners and their customers.

## **Matties:** How does Tier 2 fit into all of this? We understand Tier 1 has the resources, but Tier 2 may not.

**Caravajal:** Tier 2 probably will look for more oncall programmable fabric. I mentioned Altera and Xilinx, and those guys have the concept to make this for the masses—the Tier 2, Tier 3 players. What they can do is take a processor, an FPGA, and a memory and say, "I'm not going to tell you what software to put on this, and I'm not going to tell you what application to put on it. It has a processor, a DSP and some I/O for

#### MENTOR GRAPHICS HELPS BRIDGE GAP BETWEEN PCB AND RF continues

wireless." This is probably a good platform for a network. So let's make it flexible vs. fixed. You pay a little more money for that, for the Tier 2, but the volumes are not the same. Those particular guys that have programmable fabric are implementing new technology like processors, memory, and specialized communications like wireless and Bluetooth in one package. It's like, "Here, you have the concept, I'm giving you all the tools, and you build it."

### *Matties:* Now the RF market is a booming market, with automobiles really driving a lot of it.

**Viklund:** The interesting thing is that it's a new market, but RF used to be military, satellites, and space. Now RF is everywhere. Everything needs to be wireless, even if it's just data communication. You have automobiles now with tracking, cruise control, and radar that can scan objects, the perimeter of the road, stuff like that. And it's coming online more and more. We know that type of design needs to be really cheap; otherwise it's not in the range for normal people to buy them. That has been going on for some time. When we presented our RF product for the first time, we got some boards from a company who was doing back-up radars for SUVs. Their radar board, which was complete radar, was \$280 in fabrication costs. This is already happening. I bet there are going to be even more new markets coming into play just like automotive, and they will have the same drivers-faster designs, higher performance and cheaper products. That's what's driving it.

**Caravajal:** It's still an ecosystem that's worldwide, because if you think about the chips model I just told you about, the packaging is actually designed here, assembled overseas, sent back and tested here. The chips could be designed here and made there; the package could be designed here, tested here and then mass made overseas. You really don't see one hot spot. I'd say it's an ecosystem.

**Matties:** I see it globally, too. But it's interesting because we almost see this fervor for product made in USA or even made in China. They have a nationalistic approach now where they're really looking at the internal markets as much as they are the external markets. India has the same tone. I saw an ad in USA Today that said, "Walmart looking for US-made products to sell."

### Viklund: How interesting.

**Caravajal:** A long time ago, Walmart had a "Made in America" sign on the outside of the door. And then that dissolved over the last 25 years and now you see it pushed back. If you could do it cost-effectively, that's what it's all about. A very interesting thing you mentioned about radar. Early adopters who needed it were mainly mil/aero, and the really late adopters are automotive consumers.

**Viklund:** But it's also technology, because it was expensive to build a radar 20 years ago, and today, any student can build a simple radar on a circuit board and it will be \$100 or so in parts. Technology has driven the market.

**Caravajal:** Moore's law does drive more capability every year. And by the way, this is an extension of Moore's law. Moore's law used to say it could double your performance every 18 months. Well, they're running into cost issues and this extends it. What you're doing is integrating in a package and just thinking of the best cost performance and integrating it through a whole process. So we covered the RF integration, which is part of co-design, and then I covered the integration of the IC, the package, the boards. Then of course the next level integrates that package into a board, and then the board into a system. If you think about it, it's all co-design.

#### **Matties:** It's all co-design. You've got to start endto-end and work all the way through.

*Caravajal:* If you close your eyes and just throw it over the wall, poor planning will produce poor products.

Matties: Well, gentlemen, thank you so much.

**Caravajal:** Appreciate you dropping by. Glad to see you. **PCBDESIGN**

## PCB007 Highlights

### Kelly Dack Discusses His Recent Move

It's no secret that Prototron is one of the fabricators to watch in the US. I've known the Prototron staff for years, and worked with them for a number of years as well. So, when I heard they had hired Kelly Dack, a longtime PCB designer and guest editor for PCBDesign007, I wasted no time meeting with Kelly.

### Catching Up with Vector Fabrication's Quang Luong: Here Comes Vietnam!

I have known Quang Luong, the owner of Vector Fabrication, for many years now, and I have always been interested in his business and how it operates, especially since he is the only PCB shop owner I know of who has a company both in the U.S. and in Vietnam.

### TTM: Consult Fabricators Early for PCB Designs

Recently, I attended the Designers Council "Lunch and Learn" at Broadcom's office in Orange County, California. One of the speakers at this event was Julie Ellis, a field applications engineer with TTM Technologies. She sat down with me to discuss her presentation and some of the ways fabricators can assist PCB designers.

### Coated Ultra-Thin Copper on Printed Circuit Laminates

Nanocopper based copper foil has great promise for high-density microcircuits. Utilizing conventional coating capability, volume production is easily scalable and cost-effective.

### Institute of Circuit Technology 41st Annual Symposium

The Institute of Circuit Technology continues to grow its membership, and the Annual Symposium is a major occasion that attracts most of the leading names and faces of the UK PCB industry. This year's event was not only a platform for exchange of knowledge and ideas, but another great opportunity for building networks and collaborative relationships.

### **EIPC Summer Conference: Day 2**

Refreshed after an excellent conference dinner, and for most, a good night's sleep, delegates returned

### **EIPC Summer Conference, Berlin: Day 1**

Berlin, capital of Germany and a world city of culture, politics, media and science, was the venue for the 2015 EIPC Summer Conference, which attracted delegates from sixteen countries, including Russia, Hong Kong, Japan, Israel, USA and Canada, as well as the European Union, to experience a programme of 21 technical presentations over two days. Also included was a visit to the Berlin laboratories of Fraunhofer Institute, Europe's largest applicationoriented research organisation.

#### IPC Releases PCB Industry Results for May 2015

Total North American PCB shipments decreased 4.2% in May 2015 from May 2014, and year-todate shipment growth declined to -1.8%. Compared to the previous month, PCB shipments were down 3.5%.

### IPC Promotes Philip Carmichael to IPC President, Asia