Multi-Site Concurrent Design: Tips and Best Practices by Craig Armenti p.22

**Concurrent Design** by Barry Olney p.34

base for innovatio

The

# **CONCURRENT DESIGN**

# Optimizing Collaboration for PCB Systems Design

**Attack Big Problems with a Team**

by David Wiens, page 12

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

SAVE THE DATES! Upcoming IPC Events

#### July 10

**Conflict Minerals: Staying Current in a Changing Landscape** Santa Clara, CA, USA

August 20

#### Southeast Asia High Reliability Conference

Penang, Malaysia

#### September 23–25

**IPC India Conference & Workshops** *at electronica & productronica India 2014* Bangalore, India

#### September 28–October 2 IPC Fall Standards Development Committee Meetings co-located with SMTA International

Rosemont, IL, USA

October 14–15 IPC Europe High Reliability Forum Düsseldorf, Germany October 28–30 IPC TechSummit™ Raleigh, NC, USA

### November 18–20

High-Reliability Cleaning and Conformal Coating Conference sponsored by IPC and SMTA Schaumburg, IL, USA

November 19 Assembly & Reliability Conference Bangkok, Thailand

#### December 3-5

**International Printed Circuit and APEX South China Fair** (*HKPCA and IPC Show*) Shenzhen, China

More Information www.ipc.org/events

Questions? Contact IPC registration staff at +1 847-597-2861 or registration@ipc.org.

Strengthening & Advancing Electronics Manufacturing Globally

#### **FEATURED CONTENT**

Does it really take a village, or in this case, a design team? Each year, more PCB designers become part of concurrent design teams, groups that work "around the clock, around the globe." This month, we deconstruct concurrent design with articles from expert contributors David Wiens, Craig Armenti, and Barry Olney.

**12 Optimizing Collaboration for PCB Systems Design** by David Wiens

22 Multi-Site Concurrent Design: Tips and Best Practices

by Craig Armenti

FEATURE COLUMN34 Concurrent Design by Barry Olney

# Low-loss Laminate Materials for RF/Microwave/Millimeter-wave Designs

For over 100 years, Isola has been driving technology forward while improving end-product design with topperforming laminate and prepregs.

Our legacy continues with global R&D pushing our product line to the forefront in demanding RF/microwave designs.

With 10 manufacturing sites around the world, global quickturn capability, world-class technical service, measurement & modeling capabilities, and industry leading material development capabilities – Isola is well positioned to be your preferred RF/microwave partner. The newest members of Isola's growing RF/Microwave laminate family now includes Terra Green™,

a halogen-free, very low-loss, thermoset material that is available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

Astra®MT is a revolutionary ultra low-loss thermoset laminate replacement for PTFE, suitable for automotive radar, mm-wave and AESA applications.

I-Tera MT is available in core thicknesses from 0.002" to 0.018" and offers 18 different prepregs for optimal design flexibility.

I-Tera®MT RF is available in 20 and 30 mil cores and a 3.38 and 3.45 Dk.

|                                                                                                                                                                                                                                              | TerraGreen™     | Astra <sup>®</sup> MT | I-Tera® MT/<br>I-Tera MT RF | IS680                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------------|------------------------------------------|--|--|

| Tg                                                                                                                                                                                                                                           | 200°C           | 200°C                 | 200°C                       | 200°C                                    |  |  |

| Td                                                                                                                                                                                                                                           | 390°C           | 360°C                 | 360°C                       | 360°C                                    |  |  |

| DK @ 10 GHz                                                                                                                                                                                                                                  | 3.45            | 3.00                  | 3.45                        | 2.80 - 3.45                              |  |  |

| Df @ 10 GHz                                                                                                                                                                                                                                  | 0.0030          | 0.0017                | 0.0031                      | 0.0028 - 0.0036                          |  |  |

| CTE Z-axis (50 to 260°C)                                                                                                                                                                                                                     | 2.90%           | 2.90%                 | 2.80%                       | 2.90%                                    |  |  |

| T-260 & T-288                                                                                                                                                                                                                                | >60             | >60                   | >60                         | >60                                      |  |  |

| Halogen free                                                                                                                                                                                                                                 | Yes             | No                    | No                          | No                                       |  |  |

| VLP-2 (2 micron Rz copper)                                                                                                                                                                                                                   | Standard        | Standard              | Available                   | Available                                |  |  |

| Stable Dk and Df over the temperature range                                                                                                                                                                                                  | -55°C to +125°C | -40°C to +140°C       | -55°C to +125°C             | -55°C to +125°C                          |  |  |

| Optimized Global constructions for Pb-Free<br>Assembly                                                                                                                                                                                       | Yes             | Yes                   | Yes                         | Yes                                      |  |  |

| Compatible with other Isola products for<br>hybrid designs                                                                                                                                                                                   | Yes             | Yes                   | Yes                         | For use in double-<br>sided applications |  |  |

| Low PIM < -155 dBc                                                                                                                                                                                                                           | Yes             | Yes                   | Yes                         | Yes                                      |  |  |

| NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions |                 |                       |                             |                                          |  |  |

NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions of the agreement under which they are sold.

#### FREE WEBINAR

#### PCB Material Selection for RF/Microwave/Millimeter-wave Design

This webinar will educate you on how to select the appropriate PCB material for RF, microwave and millimeterwave applications through careful consideration of cost constraints and system-performance parameters, such as the frequency of operation and bandwidth, the electrical size of board and its critical features, loss and uniformity requirements, temperature range of system operation, and thermal and processing considerations.

# www.isola-group.com/RF

JULY 2014

**VOLUME 3**

NUMBER 7

thepcbdesignmagazine.com

THE OPTIMUM

MAGAZINE

DEDICATED TO

PCB DESIGN

#### CONTENTS

AN CONNECTOR PUBLICATION

MAGAZINE

тн≣ЮСр

#### ARTICLE

52 Choosing the Right PCBA Repair Shop by Ron Fukui

#### **VIDEO INTERVIEWS**

**40** Sunstone on New Initiatives, Website and More

ΤM

45 Printed Circuit Handbook, 7th Ed., **Coming Soon**

48 IPC Printed Electronics Standards Update

#### SHORT

30 "Tiled" 36-core Chip Unveiled

**EXTRAS 60** Events Calendar

61 Advertiser Index & Masthead

#### **COLUMNS**

**8** Help Wanted: PCB Design Needs an Icon by Andy Shaughnessy

42 Considering **Creepage and** Clearance by Amit Bahl

**46** Accelerating the

**SI Learning Curve:**

by Bert Simonovich

- **NEWS HIGHLIGHTS**

- **32 PCB007**

- 50 Mil/Aero007

- 58 PCBDesign007

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits<sup>®</sup> is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

### Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

# Help Wanted: PCB Design Needs an Icon

#### by Andy Shaughnessy

I-CONNECT007

For years, veteran designers like Gary Ferrari, Bill Brooks, and the late Glenn Wells, just to mention a few, have been spreading the word to young people about PCB design as a viable career. Now, there are actual PCB design classes available at a handful of colleges, and PCB design is becoming more visible to the general public.

But it's still an uphill battle. Designers are retiring, and they just aren't being replaced. When was the last time you met a designer who was under 30?

Imagine what it's like to be a smart high school or college student—the kind of kid who would make a great PCB designer. You'd be interested in math and science, and you'd be considering a career in electronics. You'd be a little bit off-grid, and able to harness that facet of your personality.

But you'd be getting deluged with information. You and your friends would most likely be interested in the "sexier" careers such as game developer or Web developer. Or you may have your sights set on being an electrical engineer. Not that there's anything wrong with that, of course.

After all, the EE is a known quantity; I imagine there will always be kids dreaming of being EEs. Why isn't it that way for PCB design?

If everyone knew how satisfying (and, often, profitable) a PCB design career can be, there would be waiting lists for every PCB design job. You know exactly what I mean: You may hate your boss, your company, and/or the EEs, but

# Solutions to Ensure PCB Manufacturing Success!

Verify and Optimize PCB Designs for Successful Manufacturing.

### **BluePrint**·PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

For more information please visit downstreamtech.com or call 800-535-3226.

#### HELP WANTED: PCB DESIGN NEEDS AN ICON continues

you love what you do. Not many people can say that.

We need to find a way into these kids' busy brains. What's our hook, our 10-second eleva-

tor spiel? PCB design suffers from an image problem. It has no image, and that's the problem.

PCB design needs an icon. Something that represents everything that design is about. Something we can show high school seniors and college students that would illustrate this career.

What idea encapsulates a designer's job? It doesn't have to be that complicated. We just need something to get kids thinking about PCB design.

Fabrication and assembly can be represented by the factory icon that we see in Skype and on the iPhone: a yellow building with a smokestack.

Assembly also has the robot. SMTA Atlanta has made the robot into a kind of icon. For the past couple of years, SMTA Atlanta has sponsored a robot competition to help get students interested in elec-

tronics and electronics assembly, and it seems to work. The students build remote-controlled robots and they compete for a prize. The robots have to pick up an object, move from point A to point B, etc. Then, while we're walking the aisles of the show, they're ramming their robots into each other and showing off for the adults. But it's clear that some of them want to be like us when they grow up.

They've built this robot, this cool thing that they can touch, something they can understand, and along the way they learn about high-tech manufacturing. It's not a stretch to see these kids becoming involved in robotics, capital equipment, or some other aspect of electronics assembly, especially when all these adult techies applaud for their favorite robots. The

They've built this robot, this cool thing that they can touch, something they can understand, and along the way they learn about high-tech manufacturing. It's not a stretch to see these kids becoming involved in robotics, capital equipment, or some other aspect of electronics assembly, especially when all these adult techies applaud for their favorite robots.

robot is a good path into a student's cluttered mind. It's a futuristic icon that kids can hang their sideways baseball caps on.

But what is PCB design's icon? It's just tough to illustrate PCB design—ask anyone who has ever tried for days to

> come up with a cover for a PCB design magazine. Having been involved in all types of

been involved in all types of PCB mags, I have to say that design is by far the hardest segment to illustrate.

Fabrication and assembly are much simpler. You have a variety of ideas to work with: a close-up of a PCB or PCBA, a panel of PCBs, capital equipment, drills, lasers, squeegees, dispensing nozzles, a thermometer reading 260°C for a lead-free assembly...the list goes on. Or you can just write something clever in green or coppercolored lettering.

But design is such an abstract idea. There are a few obvious cover ideas: a giant key with a tagline of "Unlocking the Door to Signal Integrity." Then there's the twisting path heading into the

horizon, labeled "The Long and

Winding Road to HDI." After that, it's a struggle. Design is the most important part of the whole equation, in my humble opinion, but it's hard to wrap your mind around it. PCB design needs an icon, and it needs one now.

What do you think it should be? What is our robot? What is our icon?

Contact me with your ideas! **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 13 years. He can be reached by clicking <u>here</u>.

prototron.com

# We Take the Time to do it Right because you don't have the time to do it over.

# Optimizing Collaboration for PCB Systems Design

**by David Wiens** MENTOR GRAPHICS CORP.

#### **Design Efficiency in the Fast Lane**

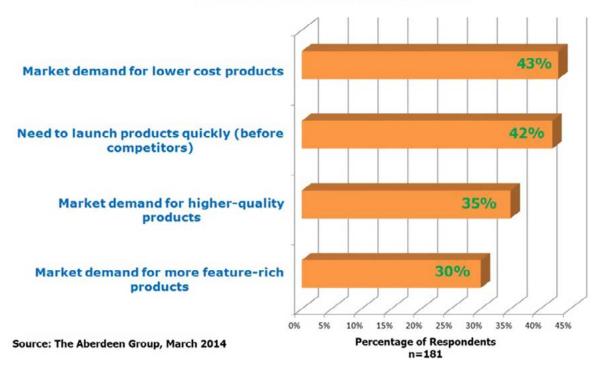

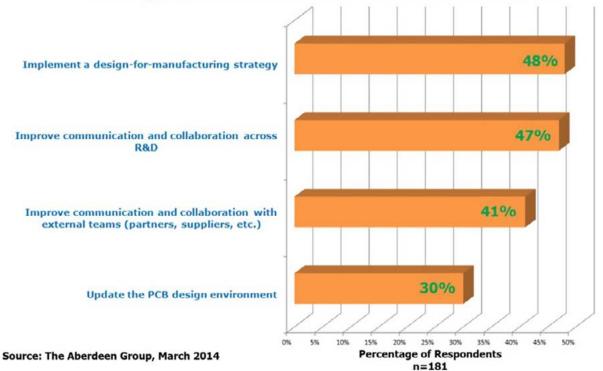

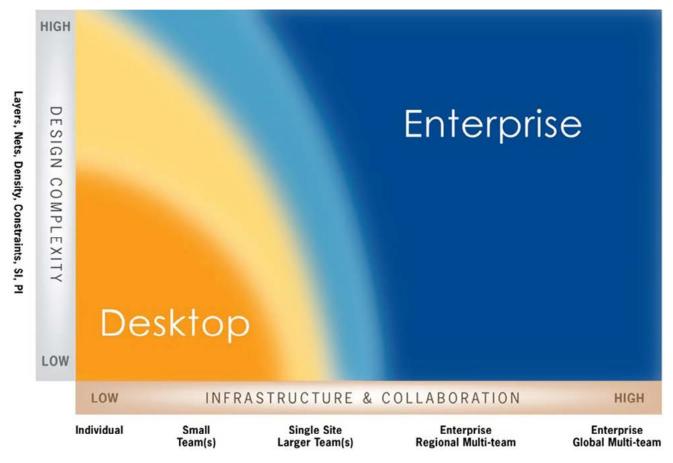

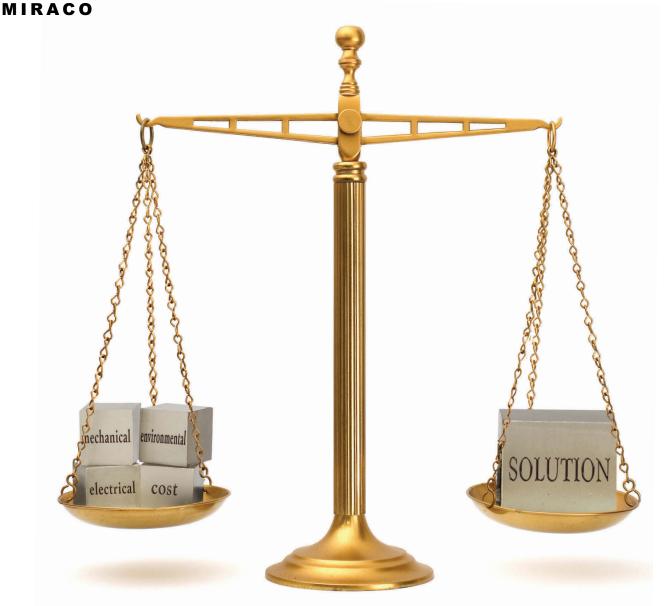

PCB systems design pressures can be broken down into the ubiquitous buckets of time, cost and quality. Efficient design is about balancing the three. Push too hard to shrink the design time, and watch your costs go up while quality diminishes. Spend too much time optimizing a design, and watch your market window wave goodbye. A recent survey by The Aberdeen Group <sup>[1]</sup> confirmed these critical pressures, and also identified some strategies to resolve them two of the top four involved optimizing collaboration across the design team. Figures 1 and 2 show the responses graphically. PCB design teams can range from the individual who does everything up to global enterprises with large, distributed teams. Large teams have a competitive advantage of resources and specialization, but they also bear the challenge of optimizing those resources to avoid the diminishing returns that can come with team inefficiency. The other dimension to the problem is design complexity, illustrated with Figure 3. An individual can design almost anything with the right tools; the challenge is to complete the design within a reasonable time, while optimizing quality and cost. Enterprises can tackle complexity with larger teams on a project, including specialists who can optimize design functions for quality.

Let's look at typical types of enterprise collaboration, and propose some best practices to optimize efficiency across the design team.

# Advancing the applications of conformal coatings

Our knowledge of the wider industry, combined with our ever advancing approaches to research and development, have created a range of Conformal Coatings with the necessary high performance and reliability required for the military, aerospace and commercial industries.

Although every electro-chemical solution is in our spectrum, our specialist approach to problems has established us as a key provider and developer to the technical electrical industry, both commercial and domestic.

Isn't it time you discovered out how Electrolube can serve you? Simply call, or visit our website.

Tel: 888-501-9203

Scan the code to discover our full spectrum of superior Conformal Coatings and electro-chemical solutions.

# ELECTROLUBE

Electronic & General Purpose Cleaning Conformal Coatings Encapsulation Resins Thermal Managem Solutions Contact Lubricants Maintenance & Service Aids

#### **Pressures on the PCB Process**

Figure 1: From the Aberdeen Group report, the top four responses to pressures on the PCB process.

### Strategies to Reduce Pressures in the PCB Process

Figure 2: Respondents were also asked to list strategies that would help reduce pressure.

Figure 3: Organizational and design complexities scale. The challenge is to complete the design within a reasonable time, while optimizing quality and cost.

#### **Collaboration is Everywhere**

Regardless of your team size, there are always plenty of opportunities for collaboration; this business isn't a good place for hermits. Because collaboration involves transfer of data from one person to the next, and often from one tool to another, multitudes of "neutral" files have sprung up over the years as hand-off mechanisms. Some formats have survived the ages to become de facto or formal standards, but even formal standards are subject to interpretation at the sender or receiver, leaving them as imperfect media for collaboration but still the best option in many cases. Within vendor tool flows, the most efficient collaboration is achieved by sharing the same database, leveraging a client/server architecture so that there are no errors in translation, and absolute concurrency is achieved.

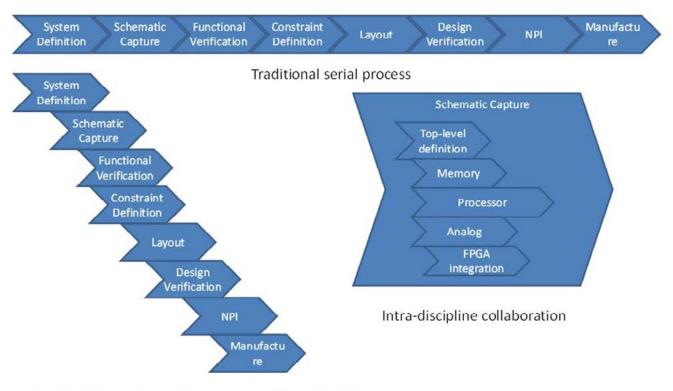

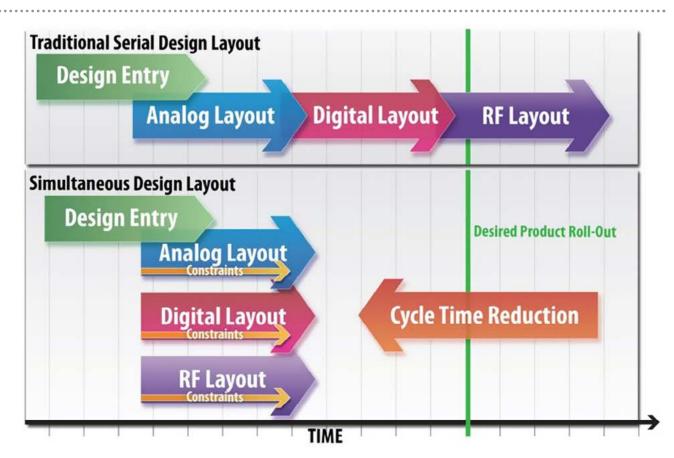

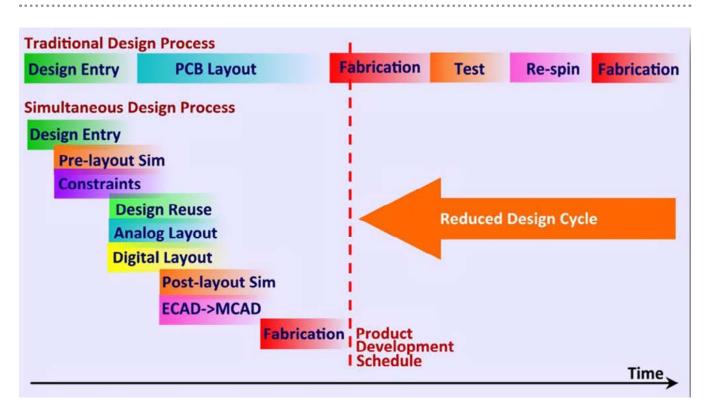

Due to inefficient collaboration environments, traditional design processes were very serial in progression—one stage would be completed before the next was started. ECOs were painful to execute, and thus discouraged. Improved flow integration and collaboration standards have enabled concurrent design processes that significantly reduce design cycles, and provide additional opportunities for design validation and optimization (virtual prototyping).

Collaboration opportunities can be broken down into those between engineering disciplines (e.g., ECAD/MCAD, FPGA/PCB, and design/manufacturing) referred to here as "interdiscipline collaboration, and those within an engineering discipline (e.g., multiple engineers working on a schematic, or multiple designers working on a layout) referred to as "intra-discipline collaboration."

Inter-discipline collaboration across multiple disciplines

Figure 4: Collaboration can significantly compress the traditional serial design process.

#### **Inter-Discipline Collaboration**

The most common example occurs between design engineers and layout designers. Originally, it was a very serial process, with an engineer defining the logic on paper, then handing to the designer to draw the schematic and layout the board. Today, logic design, constraint definition and layout are expected to proceed concurrently, with initial board definition and placement occurring while the schematic is still under development. Of course, even if a schematic is proclaimed complete there are almost always going to be ECOs (something that the recent Aberdeen study identified as a major obstacle to efficient design)-being able to easily update the design is critical. An engineer is basically communicating intent to the layout designer (e.g., packaging, connectivity, constraints, and component floor plans/groups). In an efficient collaboration this is done without side documents or "voice-driven mouse."

The other common collaboration is between

layout designer and manufacturing (typically with an NPI engineer acting as the middleman). This also used to be a very serial process, with manufacturing waiting until the layout was complete and with outputs generated before doing the first checks for manufacturability, creating a ton of design re-spins. Today, best practices involve leveraging the DFM rule deck from the target fabrication and assembly houses during placement and routing to optimize the layout before it's finished (known as concurrent manufacturability validation). The hand-off to manufacturing has also been streamlined, with ODB++ being leveraged as the single source of data for manufacture (replacing the multitudes of separate files that used to be passed to manufacturing, requiring time-consuming, errorprone re-integration to produce intelligent data for manufacturing).

Every PCB must have a mechanical enclosure. Traditional collaborations were done with very conservative constraints (limiting PCB de-

" Providing Solutions to Board Fabrication Challenges"

# FROM CONCEPT TO COMPLETION

### **Solutions for Every Complex Situation**

At Multilayer Technology we have the skills and the knowledge to be able to say "Yes We Can!" to your most complex design requirements.

We specialize in High-Speed Digital and RF Design constraints. In addition, we offer the following solution-based services:

- Extensive Exotic Material Processing

- Pre-DFM Services Available

- State-of-the-Art Industry Leading Processes

- Space-Based Reliability Requirements Standard

**REQUEST A QUOTE**

WWW.MULTILAYER.COM

Multilayer Technology 3835 Conflans Rd Irving, TX 75061-3914

(972) 790-0062

Mil-PRF-55110

sign options) and actual alignment wasn't determined until physical assembly. Today, PCB design systems include 3D visualization to enable optimization for the enclosure—and when collaboration is required to optimize the electro-mechanical product, dynamic communication with the mechanical engineer is provided via tools leveraging the ProSTEP IDX standard. Given basic outline constraints, design of the PCB can now proceed in parallel with refinement of the mechanical enclosure.

Integration of FPGAs on PCBs provides an opportunity for pin swapping to optimize the PCB for performance and cost—so efficient collaboration between FPGA and PCB engineers is critical. The cross-domain interchange has been vendor-specific, requiring flow-dependent processes and limiting optimization passes. Improved integration has enabled bi-directional collaboration and even multi-FPGA optimization based on PCB placement.

Most PCBs don't live by themselves; they're coupled with daughter cards or backplanes for cost-efficiency and flexibility. Definition of that multi-board PCB system has typically been isolated from the PCB design environment, requiring re-capture at the PCB stage (much like the original collaboration between PCB engineers and layout), increasing design time and potential for re-design errors, and also minimizing opportunities system optimization. Emerging environments support dynamic collaboration between system-level and PCB-level design, facilitating quick ECO updates and re-partitions for optimized system performance, size and cost.

Another system context is the design of IC through package to PCB. These three disciplines are often supported with disparate, disconnected toolsets. Tying the disciplines together (or even leveraging common tools) improves collaboration, resulting in optimal system performance, size and cost. Recent advances have automated definition of the connectivity between platforms, and also leveraged common design technologies to minimize the system design learning curve.

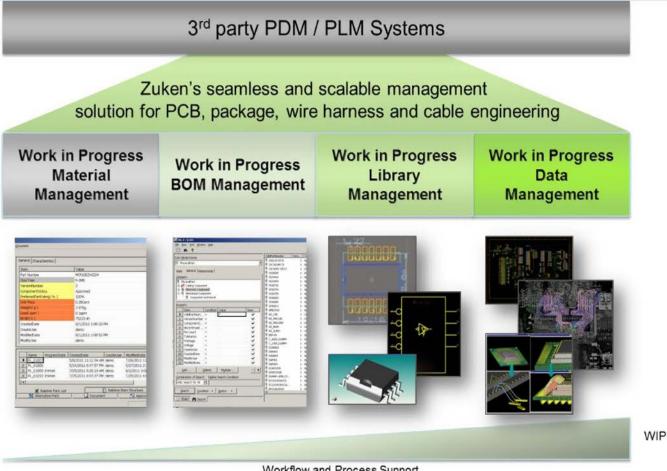

Mid-to-large enterprises achieve economies of scale by leveraging common design data (e.g., component libraries, simulation models, and reuse blocks) across multiple projects. They typically manage this data, as well as control access to work-in-process designs, via conventional PLM systems. While functional, this process views PCB data as black boxes, with no visibility into the actual data, limiting design reviews and collaboration opportunities. Emerging standards such as the EDX format coupled with PCB-level design data management enable efficient collaboration with enterprise-level teams, and provide optimal access control and visibility for PCB design data.

#### Intra-Discipline Collaboration

We've covered the parallelization of interdiscipline tasks, but what about concurrency within a design task like schematic or layout design? Given that legacy schematic entry and layout tools were designed for a single user, it's no surprise that a multi-user process is cumbersome, though some enterprising teams haven't created workarounds. Engineers have long teamed up on a schematic design, enabled by either a hierarchical or flat multi-sheet structure that allows them to partition and distribute schematic blocks, and later stitch them back together. This "split and join" process requires manual communication regarding system updates (e.g., a new global signal name), diminishes team visibility into each other's work, and provides fun alignment challenges when the blocks are reintegrated. Now imagine doing that on a layout (it's often done by region or layer). How do you ensure that cross-region traces or vias will line up when the design is reintegrated? How do you partition the design when you've got cross-board (side-to-side or front-to-back) connectivity? How do you decide partition areas if not all parts are placed?

To enable efficient concurrent intra-discipline collaboration, the tools must be re-architected to support the team model. A client/ server architecture enables multiple team members to concurrently access and edit a design, with dynamic updates so everyone is in sync. The communication between clients and server must also be optimized to deal with network latency issues if the team is distributed.

Applied to the schematic stage, multiple engineers could define logic in different sheets of

#### **OPTIMIZING COLLABORATION FOR PCB SYSTEMS DESIGN** continues

a common database (no need to partition the design first). This has the added benefit of resource flexibility—if there's no up-front partitioning pain, there's no problem adding team resources where necessary for short intervals to accelerate a project.

Optimization of designs for signal and power integrity is transitioning from isolated specialists (leveraging the inter-discipline collaboration model) to every design engineer. This means that the engineers must also be able to access simulation tools directly from the schematic, and transfer rules developed through analysis directly into the constraint system.

Most systems today allow definition of constraints within the schematic, a significant advancement from the days when spreadsheets were passed to the layout designer for inclusion. If you have multiple engineers working on the schematic, you also must allow concurrent constraint entry. Taking it a step further, since the layout team also needs to see the constraints, they must be able to access and edit constraints along with the engineers.

The real fun with true concurrent design comes at the layout stage. Without a partitioning hurdle, designers could jump into a design at any time. True concurrency means no boundaries, and no task limitations (i.e., it should work for placement, routing, plane definition, manufacturing preparation, etc). A side benefit of this approach is mentoring—a junior designer could work alongside a senior designer to learn best practices (in reality they could be on opposite sides of the planet). Design reviews and/or validation could happen concurrently with design. Some teams segregate design by functional boundaries (analog, SerDes, DDRx, RF); you could call this inter-discipline collaboration, but I've included it in this section since they all use the same tool for layout. And as you'd expect, true concurrency should allow all of these specialists to work in parallel, as shown in Figure 5.

Figure 5: Concurrent layout can shorten the completion time significantly.

#### **Impediments to Collaboration**

As you might expect, entering a concurrent world can have some challenges beyond just a new tool learning curve. You must also have awareness of hardware and network configuration requirements and limitations (particularly with geographically dispersed teams) to ensure optimal client/server performance.

There are also new opportunities for conflict between team members in the intradiscipline model. What if two people want to edit the same schematic block, constraint, component or route? Conflict resolution mechanisms can be automated within software minimizing the need to stop work, send e-mail, or deploy the "sneakernet" to resolve the issue. But an effective workflow must also be defined, with team leads

identified to drive the process and keep the team in sync. Disruptive updates, such as a logic or constraint ECO, should ideally be coordinated to minimize design cycle interrupts that impact all members working concurrently (constant forward/back annotations between a team of engineers collaborating with a team of layout designers will drive everyone crazy).

Another issue with intra-discipline collaboration (regardless of whether it's the traditional serial 24-hour shift model or a concurrent process) is re-engineering, also known as the not-inventedhere syndrome. Everyone has their own style for laying out a schematic or layout—team members must resist the urge to redo the work of others, or the gains of collaboration will quickly be lost.

#### Enabling Efficient, Concurrent Collaboration

The primary benefit of efficient collaboration is an accelerated design cycle. We've seen customers achieve more than 70% reductions in design time just on layout, with efficiencies nearing 100%. In addition, if the core flow is accelerated, additional virtual prototyping tasks can be added to the process to validate for improved quality (e.g., signal/power integrity, thermal, and manufacturability). Alternative architectures and layouts can also be explored (e.g., different place, route and stack-up scenarios) to optimize the product for performance and cost.

Concurrent collaboration (without the partition/reassemble overhead) is also a great resource management tool, enabling the CAD manager to shift resources to the most critical projects

at any time, maximizing resource usage. Design specialists can be de-

ployed in any geographic location concurrently with the rest of the design team. Dropping the partitioning step also improves data integrity by maintaining just one copy of the design data.

Moving from a serial to parallel collaborative process also reduces extra shifts and overtime—a significant design cost benefit. With the "round-

the-clock/world" design model, there's

a longer time between finding and fixing problems; specialists aren't fond of doing design reviews 24 hours a day. But a concurrent process resolves this (everyone's working in the same shift). There are limits to how many people can work concurrently on designs, so if you really want that overtime, it's still an option when design volume goes through the roof.

PCB systems design can't be done without some level of collaboration—everyone does it. There are a ton of design process and data format improvements that have emerged over the last five years to enable efficient collaboration. Take a look at your team collaboration, and ask yourself the question: Am I as efficient as my competitors? **PCBDESIGN**

#### References

1. PCB Design: A Guide to Optimizing Design Engineers, Kevin Prouty, The Aberdeen Group, March 2014.

David Wiens is a product marketing manager at Mentor Graphics.

We've seen customers achieve more than 70% reductions in design time just on layout, with efficiencies nearing 100%.

# ventec

### A HIGHER DEGREE OF THERMAL CONDUCTIVITY, WHERE AND WHEN YOU NEED IT.

|        | Thermal<br>Conductivity | Ceramic<br>Filled | Fully<br>Formable | Non-Glass<br>Reinforced | Halogen<br>Free |

|--------|-------------------------|-------------------|-------------------|-------------------------|-----------------|

| VT-44A | 1.0W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4A1 | 1.6W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4A2 | 2.2W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4B1 | 1.0W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4B3 | 3.0W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4B5 | 4.2W/m.K.               | $\checkmark$      |                   |                         |                 |

| VT-4B7 | 6.5W/m.K.               | $\checkmark$      |                   |                         |                 |

**VIEW THERMAL MANAGEMENT PRODUCTS**

#### Wherever technology takes you, we deliver.

Ventec Europe www.ventec-europe.com Ventec USA www.ventec-usa.com Ventec International Group www.venteclaminates.com

## Multi-Site Concurrent Design: Tips and Best Practices

**by Craig Armenti** ZUKEN

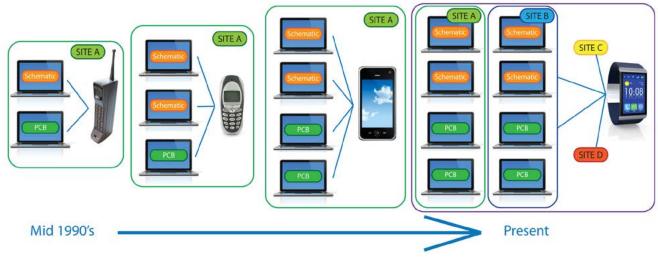

What does concurrent design mean to you? Chances are, if you ask six different engineers or designers you will get six different responses. Their responses will vary based on the types of industries they are in and their experience in this area. When I presented a paper on concurrent design at a conference in 1998, the highlight was having been able to achieve one schematic engineer and one PCB designer located at one site simultaneously working on one design. Since then, time-to-market demands, along with advances in networking technology and cloud computing, have pushed the process to require multiple schematic engineers and multiple PCB designers located at multiple sites, all accessing the same database concurrently: multi-site concurrent design.

#### **How Did We Get Here?**

When commercially-developed EDA software became readily available during the early 1980s, companies with multiple design centers shared very little design data. The EDA vendors were tightly aligned with computer hardware vendors and there were no standards for installation or GUIs. Typically, each design center was responsible for configuring and managing their individual installation of the EDA tool suite easy but limited. Each design center usually had a dedicated tools support person or team that would gladly customize the environment based on user requests. Configuration management was mostly ad hoc, with little traceability back to the original requirements for any environment customization.

Over time, as EDA software matured, as technology allowed for real-time collaboration, and as companies expanded, merged, or were acquired, each site's highly customized, locally optimized unique environment suddenly became a liability. In order for one design center to share data with another design center, the local environment and the local CAD library had to be self-contained (best case) or transferred in whole (worst case) in order for the design data to be viewable and editable at another site. Design teams quickly came to the realization that standardization of both the EDA environment

# It's a honor to receive Raytheon's highest supplier award ...again!

For the second consecutive year Murrietta Circuits was one of only 15 suppliers to receive the highest level of recognition the Integrated Defense Systems business supplier can achieve.

sales@murrietta.com | (714) 970-2430

RANDBROD Integration

#### **MULTI-SITE CONCURRENT DESIGN: TIPS AND BEST PRACTICES** continues

Figure 1: The evolution of concurrent design.

and the CAD library would be required in order to realistically share and reuse design data.

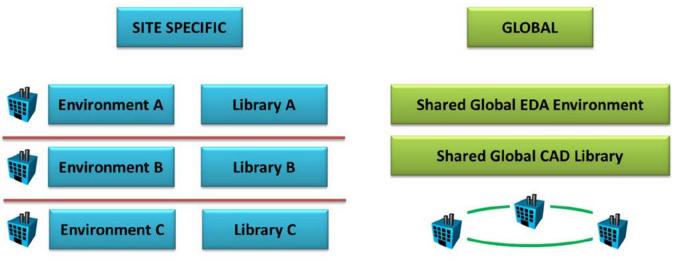

#### **The Foundation: The EDA Environment**

As the practice of maintaining design centers in different regions of the world has proliferated, the need to manage EDA tools globally and the opportunity for global multi-site concurrent design present themselves. If you are responsible for the configuration and management of an EDA environment, you already know this is a critical role. It's more than just an assemblage of tool executables. The underlying configuration files and the associated CAD library influence all system operations. The spiral of complexity rapidly increases when the installation spans multiple sites in the same region and becomes even more complex when the installation spans design centers around the globe. Proper configuration and management of a global EDA environment and CAD library is a prerequisite for global, multi-site concurrent design.

#### Global Multi-Site Product Development Requirements

A company that has a need to support multi-site concurrent design will require an underlying engineering data management (EDM) system that can dynamically manage the environment, the CAD library, and the design data per the following requirements:

#### 1. Environment Management

• All design sites utilize a common, centrally managed, continually synchronized enterprise-level EDA environment. Minor sitespecific variations are acceptable, as long as the variations do not compromise the fundamental requirement to seamlessly share design data.

• All environment data is under strict revision control with write access allocated only to those with responsibility for maintaining the environment.

• Environment data is updated as required, tested in a sandbox environment, approved for release, and then synchronized to each site's production environment.

• Only environment data customized to support the corporate requirements is managed at the enterprise level. All other environment data is accessed from the local install. The end result: you are only managing and replicating the minimum set of customized data to support your corporate requirements. You move from managing hundreds of environment files, to managing files that now potentially number only in the tens.

#### 2. Library Management

• All design sites utilize a common, centrally managed, continually synchronized CAD library.

### IT'S HIGH-PERFORMANCE RUGGEDIZATION. ONLY WITH MUCH HIGHER EFFICIENCY.

**Dymax 9309-SC** is the only light-curable edgebond material with patented See-Cure technology, giving you the speed and efficiency of visual cure validation with outstanding shock and impact resistance. And by holding its shape, 9309-SC minimizes capillary action and prevents material leaks. All this, backed by the Dymax Edge...an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise to deliver the best solution possible. Visit www.dymax.com/ruggedize to request a product sample.

877-396-2988

#### **MULTI-SITE CONCURRENT DESIGN: TIPS AND BEST PRACTICES** continues

Figure 2: Site-specific vs. global approach.

the by both the EDM system and the EDA softwa

• In its simplest form, write access to the library data is allocated only to those with responsibility for maintaining the library's logical, parametric, and geometric information. In its more sophisticated form the library can also be configured to interface with information from a centralized Component Information System (CIS). At this level the parametric data in a Material Requirements Planning (MRP) system, an Enterprise Resource Planning (ERP) system, or a content provider, is available for viewing during the component decision-making process.

• Library data is updated as required, tested in a sandbox environment, approved for release, and then synchronized to each site's production environment.

#### 3. Data Management

• All design data exists in a central vault, accessible from any design center at any time, enabling distributed design teams to work closely together.

• Design data is under continuous revision control, with data locked for non-editing team members during work-in-progress and to all team members during release to manufacturing.

• Access to design data is permission-based only those with a need to view and/or edit data have access to the data.

• Check-in and check-out of either entire designs or portions of designs is fully supported

by both the EDM system and the EDA software suite.

• A library of known good design data (circuit blocks and PCB blocks) is available and under strict revision control.

#### **Leveraging Your Global Configuration**

Now that you are managing your EDA environment, CAD library, and design data to properly support your global engineering team, let's leverage all three to enable effective multi-site concurrent design. As time to market for many high tech products continues to be a paramount driver, various methods and techniques to reduce design cycle time are continually being developed and evaluated. For leading-edge products with short lifespans, the first to market has the luxury of time, while the clock is ticking for the followers. In many cases the leader can produce multiple generations of a product before the follower brings their first "me too" product to market. A properly managed and configured global design environment can provide a competitive advantage that permits design cycle time compression without the need to add resources or to compromise quality.

### Manage and Share Work Locally and Globally

Design teams with resources distributed around the globe are a fact of life for many corporations today. The ability to work on a design

#### **MULTI-SITE CONCURRENT DESIGN: TIPS AND BEST PRACTICES** continues

Workflow and Process Support

continually, following the sun across multiple sites around the globe, may well be critical to your time-to-market success. Functional experts in different regions can be leveraged to continually move the design forward 24 hours a day. Think of your global configuration and supporting EDM system as a "virtual design center" that can seamlessly manage both the individual design objects along with their relationships at any point in time at any of your global design centers, ensuring rigorous configuration control throughout the design cycle.

#### **Partition the Design for Success**

Multi-site concurrent design employing a follow-the-sun methodology is more than just moving the entire design container from one design center to another and then back again throughout a 24-hour period. Any product development team member at any site must have access to the design data at any time. In order to facilitate this philosophy, the design team should first use its EDA tool to partition the design by functional area. For example, if a design contains memory, processor, WiFi, RF, and power functional areas, the design container should be configured so that both the schematic and the PCB are partitioned along those same functional areas. Most EDA tools support schematic partitioning using hierarchical blocks, but that's the easy part, your tool also needs to support:

#### • Partitioning the PCB

There are several ways for a design team to partition a PCB. One option is dividing the board along predetermined functional bound-

#### **MULTI-SITE CONCURRENT DESIGN: TIPS AND BEST PRACTICES** continues

aries with each designer routing to common virtual points. Another option is to simultaneously design without fixed boundaries. Design teams that are new to concurrent design, or with dense, highly-constrained designs, will find the former easier and more straightforward to implement than the latter. Furthermore, in the divided approach the PCB split often emulates the schematic partitions, not only facilitating the work in progress concurrent design, but also promoting subsequent vaulting of PCB blocks for reuse.

# • Management of schematic and PCB partitions both individually and as a whole

The EDM system needs to do more than just manage check-in and check-out, it needs to have a true understanding of the ECAD data. For example, if one schematic partition is checked out from your EDM system for edits, the other partitions should still be visible as read only in the schematic editor. The same applies to the PCB.

#### • Centrally managed parametric data

The component engineering tools should "suggest" the most appropriate component to a design engineer for a given partition based on corporate defined criteria such as price, availability, number of suppliers, pending obsolescence and reliability. This capability simultaneously improves quality while also properly managing component inventory.

#### • **Proper management of design rules** and constraints

Just because the design is partitioned doesn't mean the design rules and constraints become unusable. The EDA tool should support central constraint management for both electrical and physical rules that understands how to apply the constraints within the context of the partitioned schematic or PCB.

Figure 4: The "follow-the-sun" design methodology.

# www.5pcb.com

Convenient

Fast delivery

High quality

Low prices

With our online system, getting quotes and placing orders is fast, simple and convenient. In fact every step of the process can be managed online–even payment! And our quality is guaranteed.

All you need to get started is to set up your account.

D.M. Electronic International Co., Ltd.

#### **MULTI-SITE CONCURRENT DESIGN: TIPS AND BEST PRACTICES** continues

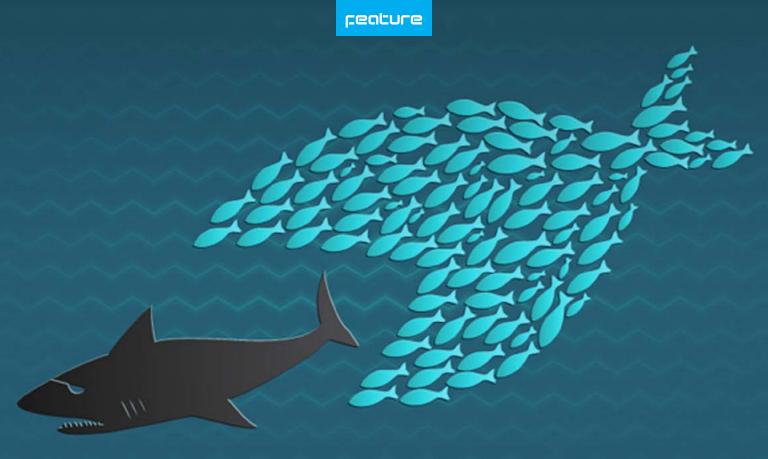

Figure 5: Do you want to be a leader or a follower?

#### Conclusion

In this article we have reviewed best practices and processes that can be applied to assist and, in fact, embolden EDA tool managers, engineers, and PCB designers to move forward with multi-site concurrent design. By investing the time to create a proper foundation with a standardized global EDA environment, then adding an EDM system that truly understands how to manage your ECAD data, you will be well on your way to sharing, reusing, and concurrently designing across all of your product centers.

In the end, you will benefit from a new level of collaboration between globally-distributed design centers, while also realizing tangential effects like promoting the documentation and sharing of engineering best practices and common processes for the benefit of all design teams in all regions. At the end of the day, you and your design team need to decide: do you want to be a leader or a follower? **PCBDESIGN**

Craig Armenti is senior technical marketing manager for PCB products at Zuken.

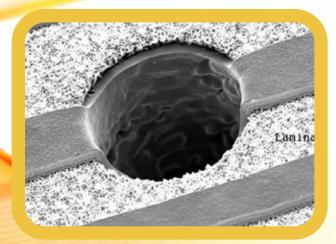

#### "Tiled" 36-core Chip Unveiled

For years, Li-Shiuan Peh, the Singapore Research Professor of Electrical Engineering and Computer Science at MIT, has argued that the massively multicore chips of the future will need to resemble little Internets, where each core has an associated router, and data travels between cores in packets of fixed size.

This week, at the International Symposium on Computer Architecture, Peh's group unveiled a 36-core chip that features just such a "network-on-chip."

The chip's 36 cores are given different, hierarchical priorities. Say, for instance, that during one interval, both core 1 and core 10 issue requests, but core 1 has a higher priority. Core 32's router may receive core 10's request well before it receives core 1's. But it will hold it until it's passed along 1's.

Cache coherence in multicore chips "is a big problem, and it's one that gets larger all the time," says Todd Austin, a professor of electrical engineering and computer science at the University of Michigan. "Their contribution is an interesting one: They're saying, 'Let's get rid of a lot of the complexity that's in existing networks. That will

create more avenues for communication, and our clever communication protocol will sort out all the details.' It's a much simpler approach and a faster approach. It's a really clever idea."

### INTRODUCING COOLSPAN® TECA thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

#### CONTACT YOUR SUPPORT TEAM TODAY

Leading the way in... • Support • Service • Knowledge • Reputation

#### SCAN THE CODE TO GET OUR CONTACT INFO.

Greg Bull Applications Development Applications Development Manager Northern Territory (U.S.) & Canada

Dale Doyle Applications Developmen Manager Western Territory (U.S.)

Applications Development Manager Southern Territory (U.S.) & South America

Applications Applications Development Manager Eastern Territory (U.S.)

Kent Yeung Regional Sales Director *Asia*

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

www.rogerscorp.com

#### North American PCB Industry Growth Still Slow

"With year-to-date growth rates improving but still negative, and a book-to-bill ratio just barely in positive territory for the second month, the North American PCB industry appears to be moving very slowly toward a modest recovery this year," said Sharon Starr, IPC's director of market research. "The negative month-to-month growth rates in April reflect normal seasonal patterns."

#### IPC PCQRR Database Allows PCB Fabricator Comparison

The IPC Printed Board Process Capability, Quality, and Relative Reliability (PCQRR) Database was developed by IPC and Conductor Analysis Technologies Inc. in 2001 for designers, purchasers, assemblers, and manufacturers of PCBs. It gives board buyers a way to compare board fabricators, and fabricators a way to compare their processes to the industry at large.

#### Invotec Strengthens Euro Team with New Appointments

Invotec Group is delighted to announce the appointment of Thomas Witt and Monika Braun as sales agent and sales assistant for Germany. Witt joins the company with extensive experience as a sales account manager, primarily within the high-reliability PCB sector, whilst Braun has a strong customer service background in the PCB industry with a particular focus on quick turnaround orders.

#### Candor Highlights Cutting-edge PCB Manufacturing

Candor President Yogen Patel remarks, "We're extremely excited over the success we've had achieving these high-end, technical builds. With the speed at which the industry changes these days, Candor wants to be ahead of the pack, at the forefront of technology.

#### **FPCB Report: Mektron Suffers First Loss**

The world's largest FPCB company, Mektron, suffered its first loss since its establishment, due to three main reasons: HDD and ODD markets contracted; the company began to intervene in the price war; and the company's 45% output came from China where RMB appreciation and rising labor costs eroded profits.

#### Multiline Restructures Business; Sharpens Focus

Multiline Technology has restructured its business to improve consistency and dependability while delivering custom equipment and spare parts. In the last few years, the company's business has changed to comprise predominately multiple camera, very tight tolerance, and large format post etch punches.

#### NCAB Expands U.S. Presence, Acquires M-Wave

One of the world's largest suppliers of PCBs, NCAB Group, has acquired 100% of M-Wave International LLC's PCB Division. Bob Duke, former president of M-Wave's PCB Division, commented, "Being selected by NCAB to be a part of their U.S. team is a great compliment. As the PCB supply market continues to evolve, I felt this was an excellent time for M-Wave to expand its resources."

#### Matrix Opens New "Value-added" California Warehouse

Branch Manager Jim Alves reports that the new warehouse is now in full operation. With the ongoing success of Panasonic High-Speed laminates, Jinzhou Carbide Tools, and Agfa Specialty products, the company is committed to expanding its services and presence in this region.

#### Technology Convergence Critical for PCB Fabrication

The PCB industry is showing signs of life, which indicates that the pendulum is swinging in a more positive direction economically, but we're not quite ready to uncork the champagne. A June 2013 report by Research & Markets forecast that the global PCB fabrication industry alone will reach about \$94 billion in 2017, with a compounded annual growth rate (CAGR) of 8.1% during this period.

#### Multilayer Technology Nets 2014 Best of Irving Award

Various sources of information were gathered and analyzed to choose the winners in each category. The 2014 Irving Award Program focuses on quality, not quantity. Winners are determined based on the information gathered both internally by the Irving Award Program and data provided by third parties.

# We deliver Advanced PCB Solutions!

### Landless Via Technology

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

CLICK TO LEARN MORE

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

## Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

CLICK TO LEARN MORE

### Impedance Tolerance <5%!

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

CLICK TO LEARN MORE

CANDOR INDUSTRIES, INC. ADVANCED PCB SOLUTIONS

www.candorind.com | sales@candorind.com | (416) 736-6306

**BEYOND DESIGN**

# **Concurrent Design**

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD AUSTRALIA

With the traditional PCB design process, the designer executes each stage of the design in sequence. But, as designs become more complex and time-to-market schedules become more demanding, we must take advantage of pre-layout simulation, and simultaneous process design in order to beat the competition. The pressure is on engineering managers to achieve more with their existing resources, although the design tasks have become more complex with increased levels of functional integration.

Concurrent design is the practice of developing products in which the different stages run simultaneously rather than consecutively. It decreases product development time and also the time-to-market, leading to improved productivity and reduced costs. Concurrent design is a relatively new process strategy and although the initial implementation can be challenging, the competitive advantage means it is beneficial in the long term. It eliminates the need to have multiple design iterations, by creating an environment for designing a product right-firsttime.

Typically, a high-speed computer based product takes two to three iterations to develop a working prototype. However, these days the product life cycle is very short and therefore time-to-market is of the essence. One board iteration can be very costly, not only in engineering time, but also in the cost of delaying the product's market launch. This missed opportu-

Figure 1: Traditional design process compared to the simultaneous design process.

# The Absolute Best Value in High Technology Printed Circuit Boards

Since 1979, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving **total customer satisfaction** on each and every job. It's just the way we do business!

001101\_01001

01001010001010101010100001010101010

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for a virtual tour of our facility!

www.eagle-elec.com

#### **CONCURRENT DESIGN** continues

nity could cost hundreds of thousands of dollars. All of the above impact on company profit by increasing prototype costs and the time-tomarket. Computer-based products have a very small market window these days (e.g., one year). If the product is delayed by six months (e.g., two re-spins) then the company has lost half its projected return.

Figure 1 illustrates the traditional design process compared to the simultaneous parallel design process. Pre-layout simulation can be done during design capture to establish the required design constraints. Functional sections of previously developed "golden" boards can be reused giving high confidence in performance and multiple designers can be employed on the same layout. Post-layout simulation and mechanical integration can be done towards the end on the layout to ensure compliance to specification prior to fabrication. This process can dramatically reduce development time.

The significant business benefits of concurrent engineering make it a compelling strategy. Introducing concurrent engineering results in:

- Competitive advantage—reduction in time-to-market means that the business gains an edge over their competitors.

- Enhanced productivity—earlier identification of design problems means potential issues can be corrected sooner, rather than at a later stage in the development process.

- Reduced development time—development of high-performance products, in less time and at a reduced cost.

Process improvement is a systematic approach to ensure a development team optimizes its underlying processes to achieve more efficient results. Process improvement is an aspect of organizational development in which a series of actions are taken to identify, analyze and improve existing design processes to meet new goals and objectives, such as increasing profits and performance, reducing costs and accelerating schedules. These actions often follow a specific methodology or strategy to increase the likelihood of successful results. There are many ways to improve efficiency in the PCB design process:

- 1. Simulation: stackup planning, PDN analysis and signal integrity

- 2. Design reuse

- 3. Collaborative PCB design

- 4. Virtual prototyping: ECAD/MCAD collaboration

#### 1. Simulation

Pre-layout analysis allows a designer to identify and eliminate signal integrity, crosstalk and EMI issues early in the design process. This is the most cost-effective way to design a board with fewer iterations, rather than starting with the "find-and-fix" based post-layout simulation.

There are multiple facets to pre-layout analysis including:

- Stackup planning for controlled impedance, SI, crosstalk, and cost control.

- Dielectric material selection for manufacturing yield, and high-frequency operation.

- PDN optimization for product reliability and cost reduction.

- I/O buffer and drive strength selection.

- Topology optimization.

- Termination strategy.

- Floor planning for critical components.

- Deriving layout routing constraints, including trace width, spacing and length matching.

- Signal Integrity analysis to meet the design specifications, with respect to noise margins, timing, skew, crosstalk, and signal distortion.

Although the trace impedance is specified on the fabrication drawing, stackup planning is often left until Gerbers are produced and the deliverables are sent to the fab shop. However, generally, the virtual dielectric material selection and trace width and clearance provided do not match the desired controlled impedance. So, the CAM engineer returns the calculations that may require trace width and clearance changes. This is not what we need at the end of the design cycle. This flawed process can be attributed to the fact the PCB designers do not have access to field solvers during layout and either have to wait until an SI engineer analyses

#### **CONCURRENT DESIGN** continues

the design, or—as commonly occurs—wait for the fab shop's report.

ICD has responded to this challenge by recently developing a bi-directional interface from the ICD Stackup Planner to Altium Designer 14. This new interface allows the designer to exact the rigid/flex stackup from the Altium Layer Stack Manager into the Stackup Planner. High-speed materials (up to 40GHz) can be merged from the Dielectrics Materials Library, of over 8,800 materials, and the impedance of multiple differential pairs can be simulated on the same substrate. Once finalized, the designer simply exports the data, including PTH and blind and buried microvia spans, trace width and clearances and differential pair rules back into Altium Designer. This allows the designer to route to impedance. A fabrication drawing of the stackup specifying all HDI requirements is also exported to Excel. (Thus ends my shameless plug. But it does work well.)

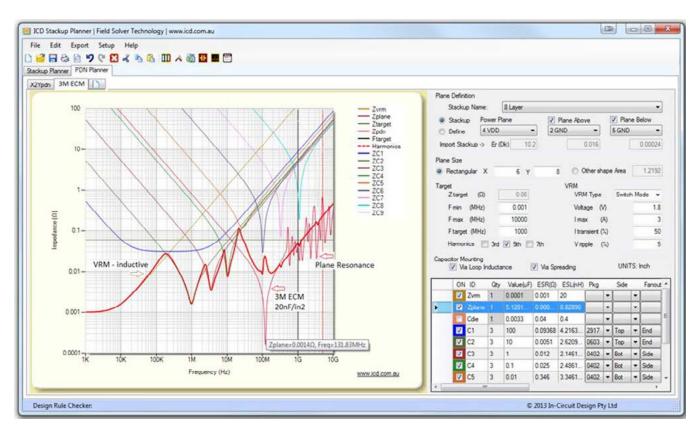

Similarly, PDN analysis is often overlooked completely. I can't stress enough how important low AC impedance is for high-speed designs that demand high-current drain at low core voltages. If the impedance is high at either the fundamental frequency or any of the odd harmonics, then higher levels of electromagnetic radiation can be expected. This has a direct impact on product reliability and the ability to pass EMC.

For years, application notes have recommended the use of three decoupling capacitors per power pin. This generally consisted of a 100nF, 10nF and a 47pF capacitor. The idea behind this was that different values provided current at different frequencies, but unfortunately not the right frequencies, as all boards are different. As can be seen in Figure 3, multiple capacitors per decade are required to keep the effective impedance, of the PDN, below the target up to the required bandwidth. If too few capacitors are used, spread widely across the frequency domain, then there is a good chance that anti-resonance peaks in the PDN will exacerbate the problem.

Also, in this case, I have incorporated the use of 3M Embedded Capacitance Material (ECM) which is the only practical way to pull the PDN low around the GHz region. This ma-

|                                                                                                                 |                | CD Station            | Panner   Fald Scher 3 | and the                                                           |                                                                  |        |       |       |                    |             |            |                   | the manage                              | State Land                          |

|-----------------------------------------------------------------------------------------------------------------|----------------|-----------------------|-----------------------|-------------------------------------------------------------------|------------------------------------------------------------------|--------|-------|-------|--------------------|-------------|------------|-------------------|-----------------------------------------|-------------------------------------|

|                                                                                                                 |                | File Lat              | Equal imput Se        | -                                                                 |                                                                  |        |       |       |                    |             |            |                   | Comercial                               |                                     |

|                                                                                                                 |                | 0.280                 | 10004                 | 501                                                               |                                                                  |        |       |       |                    |             |            |                   | um - 101.6                              |                                     |

|                                                                                                                 |                | Same Form             | FCA Parm              |                                                                   |                                                                  |        |       |       |                    |             |            |                   |                                         |                                     |

|                                                                                                                 |                | diam less             | - [41.00   81.00   1  | ine is                                                            | Line Hine Hine Mine Min                                          | Harris | 152   |       |                    |             |            |                   | 1.1.1.1                                 |                                     |

| Stack Manager UNITS: un                                                                                         |                |                       | \$/21/2014            |                                                                   |                                                                  |        |       |       | Total Board Thi    |             |            | knets: 1344.52 um |                                         |                                     |

|                                                                                                                 |                |                       |                       |                                                                   | Differential Pare > \$5.12                                       |        |       | -     |                    |             |            | and the second    |                                         |                                     |

| Save Land Presets                                                                                               | 0.12           | An Putel              | uar & Description     | Layer                                                             | Memoral Type                                                     |        |       |       | Trace<br>Clearance |             |            |                   | Edge Coupled Bri<br>Ordenential Unit: D |                                     |

| and the second                                                                                                  | -              | Contractory of        | Subbrash              |                                                                   | Lauri Petermagnatia                                              | 3.8    | 12.7  | -     |                    |             |            |                   | 3.0                                     |                                     |

|                                                                                                                 | Lauer Name     | 1 2037                | 52 203 Signal         | Tee                                                               | Conduitive                                                       |        |       | 55.88 | 205.2              | 301.6       | 8.43       | \$3.5             | 96.11                                   |                                     |

|                                                                                                                 |                |                       | Propeg                | -                                                                 | 370HR, 1080 .Re+ 86% (NONE)                                      | 3.72   | 75.88 | 17.78 |                    |             |            |                   |                                         |                                     |

| / / /                                                                                                           | top Overlay    | 9                     | Pare Core             | 010                                                               | STORE 1 1952 Re-435 Block                                        | 42     | 127   | 11.74 |                    |             |            |                   |                                         |                                     |

| 1                                                                                                               | top Solder     | 5 3                   | 8 graf                | Inter 3                                                           |                                                                  |        |       | 17.78 | 219.2              | 3018        | 9.78       | 54.03             | 101.32                                  | 2                                   |

| and the second                                                                                                  | Tea -          | 1 ( <u> </u>          | Prepag                |                                                                   | 3704R, 7828, Aur 375, (50Hz)                                     | 4.05   | 202.2 |       |                    |             |            |                   |                                         |                                     |

|                                                                                                                 | Dielectrical   | 4                     | Fare                  | V00                                                               | Store States                                                     | 42     | 826.6 | 17.29 |                    |             |            |                   |                                         |                                     |

|                                                                                                                 | SND            |                       | Fare                  | 198                                                               | Conduction                                                       |        |       | 17.78 |                    |             |            |                   |                                         | Internet D REMARKS                  |

| 6                                                                                                               | Dielectric2    | d • 1                 | 1 Lord                | tree 6                                                            |                                                                  |        |       | 17.78 | 203.2              | 101.6       | 0.19       | 54.03             | 101.32                                  |                                     |

|                                                                                                                 | Inner 3        |                       | Preprez               |                                                                   | 370-R. 7028. Rev 525, d Sinci<br>370-R. 1.1052. Rev-625, d Sinci | 425    | 2022  |       |                    |             |            |                   |                                         |                                     |

| and I fame I fame I fame I fame I fame I for                                                                    | Divisional     | 7                     | Para                  | 0402                                                              |                                                                  |        | -     | 12.78 |                    |             |            |                   |                                         | Layers'Inner 5                      |

| and the state of the | 00             |                       | Program               |                                                                   | 370HR, 1080, Run BITA (NOHA)                                     | 3.72   | 73.66 |       |                    |             |            |                   |                                         |                                     |

|                                                                                                                 | Distantia      |                       | Baral                 | Enton                                                             | Conductive<br>Lossed Photomographie                              | 18     | 127   | 55.88 | 253.2              | 101.8       | 0.43       | 83.5              | 98.77                                   |                                     |

|                                                                                                                 |                | 1.                    | Sector and            |                                                                   | Land Plater age at a                                             |        | 97    |       |                    |             |            |                   |                                         |                                     |

|                                                                                                                 | 155            | and the second second |                       |                                                                   |                                                                  |        |       |       |                    |             |            |                   |                                         |                                     |

|                                                                                                                 | Directric      | C Despitate           | Netter                | -                                                                 | a defense of hereits                                             | _      | _     | -     | _                  | _           | _          | - 10              | Diff In-Circuit Design Pr               | 114                                 |