August 2013 August 2013 MAGAZINE

How Electromagnetic Fields Determine Impedance, Part 1 p.24

Don't Forget to Terminate Cables p.32

Practical Signal Integrity p.36

PCB Materials that Empower Signal Integrity p.44

# **SIGNAL INTEGRITY**

**Differential Signal Design** (Part 1) by Lee Ritchey

S

For over 25 years, U.S. Circuit has been a premier supplier of both commercial and military Printed Circuit Boards in the United States. We have experienced continued and steady growth in a challenging economy through consistently high performance in on-time delivery, superior quality and an emphasis on the highest level of customer service. We are proud to be the Circuit Board Manufacturer of more than 400 growing companies

Markets:Medical, Military/AerospaceBoard Types:Double-sided, MultilayerMfg Volumes:MediumOther Services:Quick turn-aroundSpecialities:Blind/buried vias, Backplanes, Carbon contacts,<br/>Controlled depth drilling, Contalled Impedance,<br/>Filled/plugged vias, Heavy cop to, HDL BF<br/>Sequential lamination, Thermal.

SO 9001, ITAR registered, MIL-PF ompliant, UL

Click here to see a demo

### Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

### www.thepcblist.com

Click to see a partial list of registered OEMs!

Why did you choose THAT fabricator?

Designers: when you choose a fabricator, what guarantee do you have that they won't deliver scrap?

We can connect you with manufacturers that we have audited and are **qualified to deliver the product that you need**, on time and on budget.

### How we qualify PCB manufacturers

CLICK TO VIEW

(360) 531-3495 www.nextlevelpcb.com

### **FEATURED CONTENT**

It's not a question of whether you'll encounter signal integrity problems. It's a question of when. In this issue, the industry's top SI experts weigh in with the latest tips, tricks and techniques for achieving signal integrity.

**24** FEATURE COLUMNS

How Electromagnetic Fields Determine Impedance, Part 1 by Douglas Brooks, Ph.D.

32 Don't Forget to Terminate Cables by Istvan Novak

**36 Practical Signal Integrity** by Barry Olney

44 PCB Materials that Empower Signal Integrity by John Coonrod

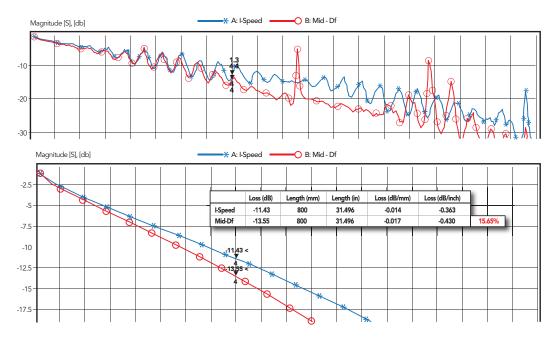

### The Next Generation High Speed Product from Isola

- Global constructions available in all regions

- Optimized constructions to improve lead free performance

- I-Speed delivers 15-20% lower insertion loss over competitive products through reduced copper roughness and dielectric loss

- Improved Z-axis CTE 2.70%

- I-Speed IPC 4101 Rev. C /21 /24 /121 /124 /129

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

- Minimizes micro-Dk effects of glass fabrics

- Enables the glass to absorb resin better and enhances CAF capabilities

- Improves yields at laser and mechanical drilling

- A low Df product with a low cost of ownership

### Effective Loss @ 4 GHz on a 32 inch line

I-Speed delivers 15-20% lower insertion loss over competitive low Df products.

http://www.isola-group.com/products/i-speed

The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these materials will be governed by the terms and conditions of the agreement under which they are sold.

Isola Group S.a.r.l. 3100 West Ray Rd., Suite 301, Chandler, AZ 85226 1-480-893-6527 http://www.isola-group.com

AUGUST 2013

VOLUME 2

NUMBER 8

thepcbdesignmagazine.com

THE OPTIMUM

MAGAZINE

DEDICATED TO

PCB DESIGN

### **CONTENTS**

AN CONNECTOR PUBLICATION

48 COLUMN 48 The CAD Library, Part 2 by Jack Olson

### VIDEO INTERVIEWS

46 Micro-Waves, Macro-Challenges

56 Bringing Manufacturing Back to America

### SHORT

56 New Material May Transfer Heat More Effectively

*EXTRAS* **60 Events Calendar**

61 Advertiser Index & Masthead

- TOP TEN NEWS HIGHLIGHTS

- 30 PCB007

- 54 Mil/Aero007

- 58 PCBDesign007

6 The PCB Design Magazine • August 2013

# The Absolute Best Value in High Technology Printed Circuit Boards

MIN 1

Since 1979, Eagle Electronics Inc. has provided our customers with the highest quality Printed Circuit Boards at fair and competitive prices. From our modern 50,000 sq. ft. facility, we continue to meet and exceed our customer's ever increasing expectations and requirements.

101003

001101 01001

101010101010101010101000101010101010

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

- Prototype to Production

- Time Critical Production

- · Commitment to Customer Service

- Best Quality Performance

- Best On-Time Delivery Performance

- Fair and Competitive Pricing/Costs

- Rapid Response to Quote Requests

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

click here to learn more

### www.eagle-elec.com

# **Differential Signal Design, Part 1**

### by Lee W. Ritchey SPEEDING EDGE

SUMMARY: In its most basic form, a differential pair is made up of two transmission lines that have equal and opposite polarity signals traveling on them. But engineers and PCB designers have been flooded with misinformation about differential signal design. Lee Ritchey breaks down diff pair design and design rules in this two-part series.

#### Introduction

Differential signaling has evolved into the signaling protocol of choice for nearly all emerging designs. Over the years I have written articles covering specific questions on the subject and have devoted chapters to it in Volumes 1 and 2 of my book series, *Right the First Time, A Practical Handbook on High-Speed PCB and System Design,* as well as articles in our newsletters.

Along with all of this, there has been a flood of both misinformation and accurate information in magazine articles, applications notes and design guides. Some of this misinformation makes PCB layout more complex than it needs to be and some of it actually introduces potential malfunctions. In order to help make the design task a little easier and sort through the misinformation, I decided it would be a good idea to pull all of this information together in a single place. This document is devoted to this topic in the hope that it will make it easier for engineers to get up to speed on this subject.

Throughout this article, I will use actual test data to determine where the limits are. At the end, there will be a list of design rules that apply to all differential pairs, along with a list of rules that should not be used as a starting point for creating a full rule set for a PCB or system.

This discussion focuses on differential pairs that are routed over planes as is common in PCBs. Differential pairs that travel on wires, such as UTP, are treated in my aforementioned books.

### What is a differential pair and how does it work?

In its most basic form, a differential pair is made up of two transmission lines that have equal and opposite polarity signals traveling on them. The property that these two signals have in common is that they are equal and opposite and they are tightly timed to each other. Beyond these two characteristics there are no other properties that matter when a design uses

### WHEREVER THE NEXT DESIGN CHALLENGE TAKES YOU, OUR LIGHT CURE TECHNOLOGY IS ALREADY THERE.

The Electronics Market continues to evolve at a faster rate than ever before. Today's complex designs, innovative materials, and increased focus on the environment can present challenges to manufacturers. Whatever demands you face, Dymax has you covered. From conformal coatings to encapsulants to edge bonding materials, we provide solvent-free, light curing technology that's truly game changing. Cost-reducing solutions that turn problems like shadowed areas, cure confirmation, and production throughput into non-issues. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. **Visit dymax.com/electronics**.

#### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

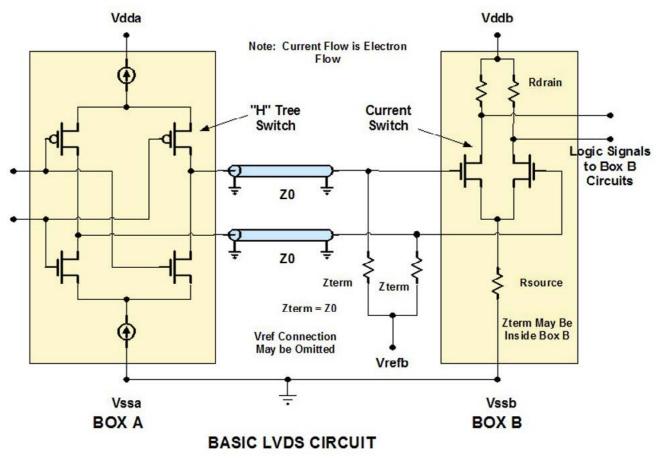

Figure 1: A typical CMOS differential signaling circuit.

differential pairs. Maintaining the equal and opposite amplitude and timing relationship is the guiding concept when using differential pairs.

Figure 1 is a typical CMOS differential pair driver and receiver pair. It is the usual circuit used in LVDS (low voltage differential signaling) type signaling protocols.

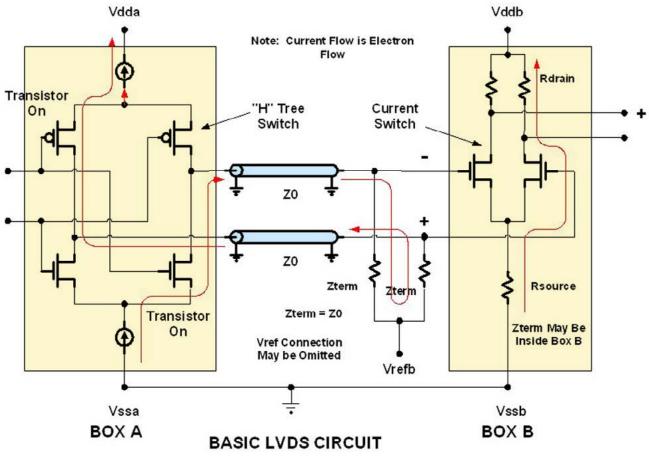

As can be seen from Figure 1, there are two independent transmission lines of characteristic impedance,  $Z_0$ , connecting the drivers and receivers. Each of these is terminated with a parallel termination of value  $Z_0$  to  $V_{ref}$  in or at the receiver. Figure 2 shows the current flow in the two signal paths when the circuit is in one of its two logic states. In the other logic state the currents reverse direction. (The two lines do not have to be the same impedance for the circuit to function properly.)

As can be seen, the current flows out of the current source in Box A through the upper transmission line and into  $V_{\rm refb}$  A different current flows out of  $V_{\rm refb}$  up through a terminating resistor, through the lower transmission line and into the upper current source. When all of the impedances in the path are of equal magnitude, the two currents are equal and opposite flowing into and out of  $V_{refb}$  so the net current into or out of  $V_{refb}$  is zero. When this is the case, it is convenient to leave off the V<sub>refb</sub> connection and place a single resistor of 2 times  $Z_0$  across the two ends of the pair. When the impedance of the two lines is 50 ohms each, this results in a single resistor of 100 ohms. As a result, those who don't understand how this circuit works mistakenly conclude that a 100-ohm differential impedance is required, when, in fact, what is needed is two 50-ohm transmission lines each terminated in 50 ohms. More about this later.

The receiver responds only to the difference in voltage between the ends of the two trans-

Figure 2: CMOS differential signaling circuit showing current flow.

mission lines and makes a decision as to whether a "1" or a "0" is present. When the polarity reverses, a logic state change is detected and sent on to circuits in the receiver box. It is at the moment of crossing that the logic state change is sensed. It is for this reason that minimizing jitter is so important. The receiver is a crossing detector so preserving the integrity of the crossing is essential. It is the primary concern when designing a differential pair. I'll come back to this later.

#### Why use differential pairs?

There are three reasons to use differential pairs in a digital or analog signal path. The most important one is that the ground connection between the two ends of the signal path can be very poor and data quality will not be compromised. Compare this to a single-ended signal path such as LVCMOS, where the signal arriving at the receiver is compared to a reference level in the receiver. If the grounds between the two ends are offset, the logic levels will be offset and one or the other of the two logic levels is compromised. This ability to "ignore" ground offsets has been the backbone of the wired Internet from the onset. In the case of Ethernet, the two ends of these links are transformer coupled. (I have seen examples of Ethernet links where the ground offset voltage was more than 6.5VAC, which would destroy the receiver if the circuit were DC coupled.)

In the case of the CMOS circuit shown in Figure 1, the driver transistor set (the H tree switch) is connected to  $V_{dd}$  and  $V_{ss}$  through two current sources. The switch is free to "float" with the circuits in the receiver circuit up or down as the ground offset between the two boxes changes. In some cases, the offset voltage can be as large as  $V_{dd}$ . As a result, the difference

#### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

voltage seen at the receiver is not affected by the offset. In some cases, the receiver circuit is connected with current sources instead of the driver circuit. ECL and most of the high-speed links with pre-emphasis or de-emphasis circuits in the drivers are examples of this. LVDS is an example of a link with the current sources in the driver.

A second reason to use differential signaling is that the link can suffer substantial attenuation of the signal and still function properly. In the case of the old ECL differential signaling circuit (the original differential protocol after which all later differential logic has been patterned), the signal leaving the driver is roughly 1000 mV. It only requires 20 mV for the receiver to successfully respond, so the signal could be attenuated as much as 24 db. In the case of many of the gigabit and higher differential signaling protocols currently in use, the signals can be attenuated as much as 20 db and the link still functions correctly.

A third reason to use differential pairs is for data paths with very high data rates such as gigabit and higher links. It is possible to drive differential paths at rates as high as 10 Gb/S over copper traces in standard PCB materials. This is impossible to do with single-ended logic paths.

#### When are differential pairs needed?

The usual conditions where differential pairs are needed can be determined from the characteristics discussed above. These are:

- Where the ground connections between the ends of the signal path are poor

- Where there is significant attenuation along the signal path

- When very high data rates are required

The first area where differential signaling was employed was the data paths between the various chassis in early mainframe computer systems. The protocol used was ECL differential signaling. Next, differential signaling was used for slow speed data links where the environment contained large amounts of electrical noise such as a factory floor. The usual protocol was RS-422 with very large signal swings.

Single-ended logic was successfully employed in almost all TTL and CMOS digital applications with wide parallel data buses until laptop computers came onto the scene with a large graphics data stream that had to pass from the motherboard through the hinge to the graphics display. When parallel data paths were used, two problems crept in: The wire bundle associated with the wide parallel data bus did not fit well into the hinge, and the ground connection was not satisfactory for single-ended operation as the simultaneous switching noise (SSN) was excessive. The solution was to switch to a serial data stream using differential signaling and call the protocol LVDS.

Since then, this protocol has been used in an increasingly wider array of products, giving rise to the following protocols. All of the following protocols share the same characteristics and can use the same design rules:

- Infiniband

- Ethernet

- Hyper Transport

- PCI Express

- Fiberchannel

- XAUI

- Rocket I/O

- Firewire

- IEEE 1394

- Universal Serial Bus (USB)

- SSCSI (serial SCSI)

- SATA (serial ATA)

- SIDE (serial IDE)

### Why aren't differential pairs used for all digital signal paths?

Knowing all of the advantages of differential signaling, we may ask, "Why hasn't it been adopted for every data path?" The reason is that most data streams are parallel bus organized, as used by CPUs and memory systems. In order to use a differential data link, which is usually serial, the parallel data stream must be first converted to a serial data stream as it enters the differential pair and then reconverted to a parallel data stream at the receiving end. This is accomplished with serializer/deserializer (serdes). The logic circuits required to do this are relatively complex and, until recently, were costly to im-

#### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

plement. As a result, this cost was only justified where no other method of communicating the data was successful.

There are examples of single data path signals that require differential signaling even when both ends of the path are on the same PCB. The clocks on DDR2 memory systems are examples of this. The SSN associated with large

data buses switching causes clocking problems with single-ended clocks, so these clocks are differential pairs.

With the advent of very in large scale integration and the shrinking of features on ICs, it has become possible to manufacture these serdes as part of a large IC at very little cost. This has made it possible to employ serial differential signaling on virtually any product including disc drives (SATA, SIDE and SSCSI), video games, PCs, and peripherals (USB).

### How is length matching tolerance determined?

At the beginning of this document, I mentioned that one of the most important design considerations when using differential signaling is making sure that the lengths of the two transmission lines are the same within some limit set by the characteristics of the circuit. A simple solution to the problem is to require that the two paths be length matched "as close as possible" or adhere to some other very tight specification. This solves the problem, but it may result in difficult or impossible routing of the PCB. Designability must also be taken into account in order to arrive at a design that is both routable and functional.

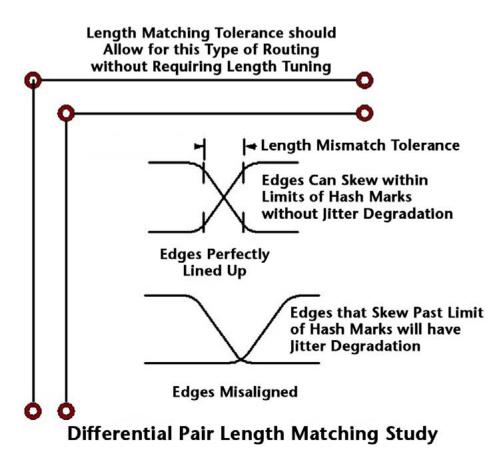

A better solution is to understand how length matching affects performance and calculate a length matching tolerance that is, on the one hand, tight enough to guarantee proper performance and on the other hand loose enough to be routable with reasonable effort. There is a straightforward way to do this. Figure 3 depicts an example of routing a differential pair using routing vias to change signal layers. It would be good if this technique could be used without requiring length be added to the shorter side of the pair. A similar condition often exists when entering or exiting connectors. Two examples of signals crossing are illustrated, the upper one with perfect matching and the lower one with the two waveforms skewed.

The primary consideration in length matching is keeping jitter to a minimum.

Jitter is the movement in time of

the crossing or data transition from bit to bit with respect to the clock that is part of the data path. Jitter is at its lowest when the two signals cross in the "straight" parts of the rising and falling edges. The circuit still detects crossings when the waveforms cross as shown in the lower case in Figure 3, but, from cycle to cycle, the crossing will move around in time with respect to the clock

due to the uncertainty associated with the low slope of the two waveforms. Crossings will also be detected when the waveforms are skewed even farther than that shown in the lower waveform pair. Because the slope of the waveforms is very near zero, jitter will be very bad and may render the circuit unusable.

Knowing this, it is possible to calculate the degree of mismatch that a given circuit can tolerate. This will allow specifying a matching tolerance that balances the demands of performance against ease of layout. The tick marks on the perfectly aligned set of waveforms mark the bounds of the "straight" portion of the switching waveforms. Jitter will stay at its minimum so long as the two edges cross within this time frame. All that is needed is to know the fastest rise and fall times of these waveforms as they arrive at the receiver to perform the necessary calculation. Once this time interval is known, multiplying it by the velocity of the waveforms on the transmission line (usually around 166 psec per inch in most PCB dielectrics) yields the length tolerance.

A couple of examples will illustrate this. LVDS is specified as working properly with length mismatches of 400 psec. Converting this

The primary consideration in length matching is keeping jitter to a minimum. Jitter is the movement in time of the crossing or data transition from bit to bit with respect to the clock that is part of the data path.

#### reature

### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

Figure 3: Example showing differential pair routing and length matching.

to a length results in a tolerance of approximately  $\pm 1200$  mils or  $\pm 1.2$  inches. Clearly, im-

mils is excessively tight. Another example is a 2.4 Gb/S serial link often used in high performance products such as routers, switches and servers. The fastest slope at the receiver is 60 psec in most systems. This results in a length matching tolerance of  $\pm 150$ mils- enough to allow routing as illustrated in Figure 3 without requiring special length matching. This will result in reduced layout time and congestion of the routing surface that results from the zigzag add length routine usually used for this purpose.

posing a length-matching requirement of  $\pm 10$

# Are there any undesirable side effects of length mismatching, even when within tolerance?

When the two edges are not aligned so that they don't cross exactly halfway from one volt-

age level to the other, as is the misaligned case in Figure 3, there is a short interval of time when current must flow into or out of the V<sub>ref</sub> terminal. If a single 100 ohm resistor is used instead of two 50 ohm resistors to V<sub>ref</sub> there is no connection. In this case, current is not available, so one of the edges will be slowed down. For low data rate protocols such as LVDS, this edge degradation is of little consequence.

When data rates are high and bit intervals are short, this degradation can have an adverse effect on bit error rate. This is certainly true for 2.4 Gb/S and higher signaling. To solve this problem, a path for the current must be provided. There are several methods for accomplishing this. One is to

use a Thevenin termination on the end of each transmission line. This has the unwanted side effect of increasing power consumption and using excessive real estate when done on die. An alternative is to provide the two 50-ohm terminating resistors and connecting their common pins through a very small capacitor to ground. The size of this capacitor need only be on the order of 10 pF for 2.4 Gb/S and higher data rates. This is a practical solution when done on die. (At gigabit and higher data rates, it is necessary to locate the terminations on die in order to preserve signal integrity.)

### **Choosing terminating resistor values**

Often, terminator values of 110 ohms are used when the specified differential impedance is 100 ohms. This looks like an error, but it is done on purpose. The reason for the higher value is as follows: Differential signal amplitudes are small, often leaving the driver at 400 mV

# Meet Ray Avalos. His only job is exceeding your expectations.

In the EMS business for over twenty years, Ray is passionate about doing things right when it comes to providing his customers with the best EMS solution on the market today.

PCB industry veteran Dan Beaulieu talked with Ray about how customers can benefit from our Integrated Solutions.

6

**CLICK HERE TO MEET RAY**

5000 East Landon Drive, Anaheim CA 92807 (714) 970-2430 | sales@murrietta.com | www.murrietta.com

### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

peak to peak. As a result, there isn't much noise margin. In order to preserve as much noise margin as possible, it is advisable to make sure that there are no reflections at the receiver from mismatches between the terminator and the line impedance. One way to help this is to use terminator resistor values that are  $\pm 1$  %. This helps, but the line impedance can vary  $\pm 10$  % as a normal part of the PCB fabrication process.

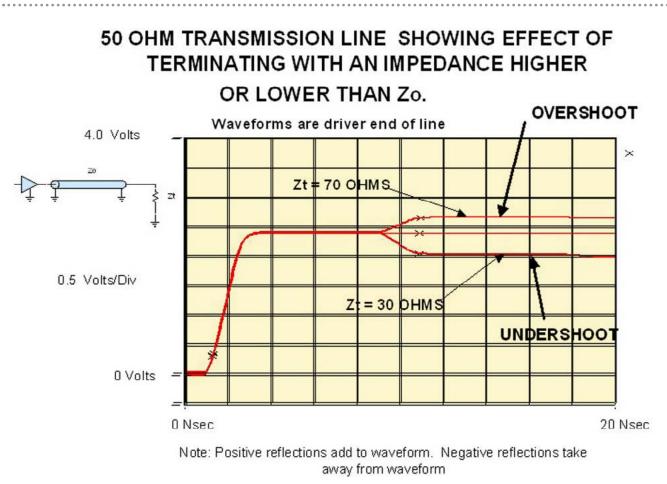

Figure 4 is the waveform observed at the driver end of a 50-ohm parallel terminated transmission line with a perfect termination and terminations that are mismatched. Notice that when the terminator value is higher than line impedance, in this case 70 ohms, the reflection is in the same direction as the original signal or adds to the incident signal. This is often called overshoot. If there is a reflection, overshoot is the one to have, as it does not degrade the signal level. When the terminator value is

less than the line impedance, in this case 30 ohms, the reflection is in the opposite direction as the incident waveform or takes away from the incident signal. This is often called undershoot. It is desirable to design the circuit so undershoot does not occur at any time.

Since the usual impedance of transmission lines in PCBs is 50 ohms and the tolerance is  $\pm 10\%$ , it would be wise to choose a terminator value that is 10% higher than 50 ohms, or 55 ohms. Similarly, for 100-ohm differential impedance, an impedance of 110 ohms would be chosen. In this case, the mismatches will result only in overshoot with an amplitude low enough that it will not cause over-voltage conditions. As can be seen, the 110-ohm value was not an error, rather it was good engineering.

As the operating voltages of DDR memory ICs have dropped, the same situation exists. The built in terminations for many of the newer

Figure 4: Overshoot and undershoot.

# Delivering the highest quality standard for Aerospace and Defense

### Ventec Accredited to AS9100 Rev. C

We are proud to announce that our parent company, Ventec Electronics Suzhou Co Ltd, is now fully certified to AS9100 Revision C.for both the design and manfacture of copper clad laminate and prepreg for aerospace applications.

AS9100 is the quality management standard specifically written for the aerospace and defence industry, to satisfy authorities such as the Federal Aviation Administration, ensuring quality and safety in the "high risk" aerospace industry.

### MORE INFO: POLYIMIDE & HIGH RELIABILITY FR4 PRODUCTS Wherever technology takes you, we deliver. Vertice Accredited AS9100 Rev C

Ventec Europe www.ventec-europe.com Ventec USA www.ventec-usa.com Ventec International Group www.venteclaminates.com

#### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

memory ICs is higher than 50 ohms, often 75 ohms. This has been done for the same reason. The number is higher than  $\pm 10\%$  due to the fact that resistor tolerances on ICs are often  $\pm 20\%$ .

### What do AC coupling capacitors do, and when are they needed?

AC coupling capacitors are inserted in series with each leg of a differential pair to provide DC isolation between the two ends of the data path. The usual reason for doing this is that the ground offsets between the two ends of the data path are too large for the built-in current sources in the driver or receiver to deal with. The most common situation where this is likely to occur is when signals travel between boxes or between cards in a large card cage. Many applications notes spell out AC coupling capacitors in paths that begin and end on the same PCB when both ends of the path are the same logic type. This is not necessary and should be avoided.

Another example of using AC coupling capacitors is when the two ends of the differential signaling path are of different technologies. The most common of these is when LVPECL (low voltage positive emitter coupled logic) is interfaced with LVDS (low voltage differential signaling).

Sizing the AC coupling capacitors is done by calculating their capacitive reactance at the lowest frequency data stream that will travel down the path. The capacitive reactance at that frequency needs to be a small fraction of the transmission line impedance to avoid excessive attenuation and signal distortion. For random data patterns, the lowest frequency may be at or near DC, in which case the capacitors will have to have very large values. Luckily, most of the data paths that use differential signaling employ an encoding scheme that makes sure the data stream never drops below some "idling" frequency. This idling frequency is used to recover the clock from the data stream at the receiver end. In this case, the capacitor value can be relatively small.

### Where should AC coupling capacitors be placed? Do they cause signal degradation?

Usually, the transmission lines that are connected to AC coupling capacitors are located on

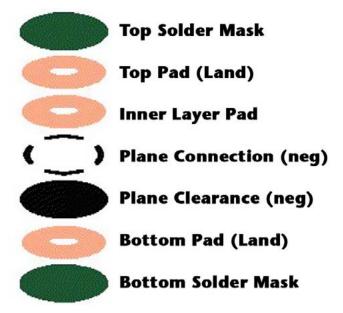

internal layers on the PCB. In order to connect the terminals of the capacitors to the transmission lines, a via is required at each end of the capacitor. These vias are almost always throughhole vias with a drill diameter of 12 mils. In a 100-mil thick PCB, the parasitic capacitance of each via is approximately 0.4 pF. There is concern that this added parasitic capacitance along with the parasitic capacitance of the capacitor mounting structure might adversely affect the performance of the transmission line. Much has been written about this possibility and much speculation has been done about how severe the effect will be.

Similar speculation takes place about where the capacitors should be located. Should they be placed near the driver? Should they be placed midway between the driver and receiver? Should they be placed near the receiver?

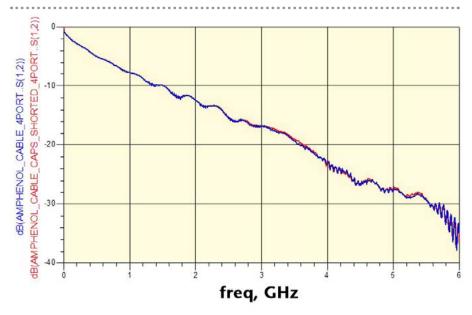

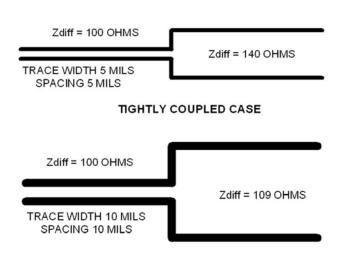

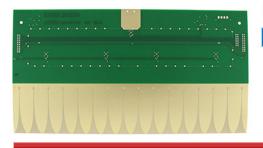

Simulations conducted in an effort to determine the effect of adding AC coupling capacitors have yielded few, if any, real conclusions. A direct approach might be to build identical transmission lines with and without the capacitors and measure the loss vs. frequency of the two paths to determine if there is any difference. This is exactly what we have done to resolve this confusion. Figure 5 is a photograph of a pair of test PCBs used to make these measurements, along with others discussed later in this document.

Figure 6 depicts the loss vs. frequency for the two paths from 100 KHz to 6 GHz. This is equivalent to 200 Kb/S to 12 Gb/S. The red curve is the path with no AC coupling capacitors and the blue curve is the path with AC coupling capacitors. Each AC coupling capacitor is 0.1 uF in a 0402 package connected to the transmission line on each side of the mounting pads with 12 mil drilled vias.

Notice that there are very small differences between the two curves, but nothing that would significantly affect signals out as far as 12 Gb/S. While this test does not actually change the locations of the capacitors along the length of the transmission line, it is reasonable to conclude that since the effect of the capacitor is very small at all frequencies of interest its location along the length of the trace will also not matter. If one considers that this is a linear

### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

Figure 5: Test PCB used to measure actual path losses.

Figure 6: Loss vs. frequency for data paths with and without AC coupling capacitors.

circuit, the location of the capacitors along the path will not change the overall behavior of the path.

### Any downsides to adding AC coupling capacitors to a differential pair?

An obvious downside to adding AC coupling capacitors to a differential pair is the need to find room for the capacitors, their connecting vias and their mounting pads, as well as the added parts on the bill of material. A notso-obvious downside is that the receiver side of the path will suffer a DC offset or drift if the data pattern traveling on the path is not symmetrical. There are two solutions to this problem. One solution is to encode the data in such a way that the data is symmetrical. This is what the 8b/10B encoding does. A second and more general solution is to add a resistive network on the receiver side of the AC coupling capacitor that "biases" the input such that the DC component of a nonsymmetrical of the waveform is eliminated.

### Is tight coupling of a differential pair a good idea?

There is the notion that tight coupling between differential pairs is a good idea. There is even one industry "guru" who is known to

say "everybody knows tight coupling is a good idea," as if anyone who does not know this must be incompetent. In some cases, the reason given is that it reduces unwanted coupling from other signals. This will be discussed later in its own section. Another reason given is that the "return currents" from one member of the pair will travel better on the other member when tight coupling is done.

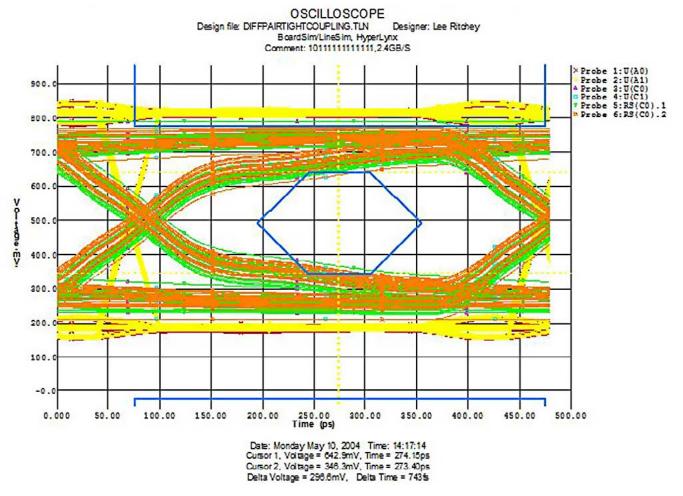

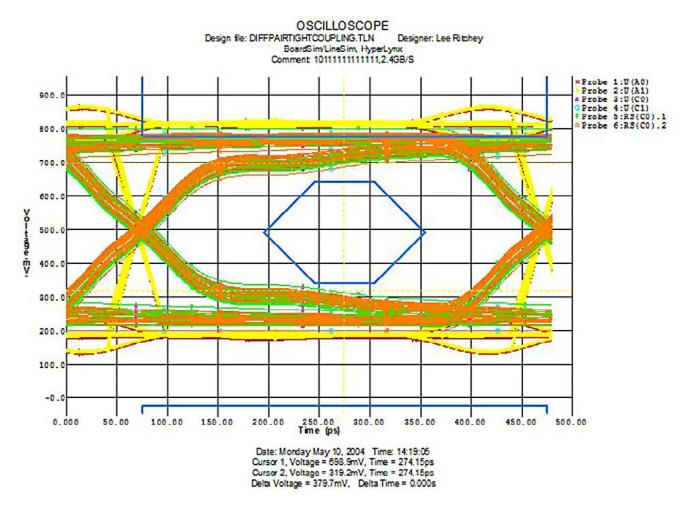

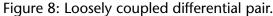

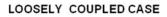

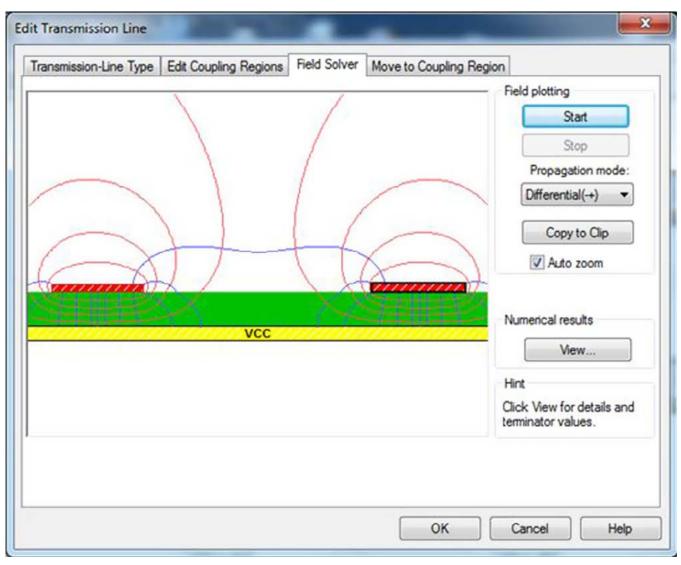

Figure 7 shows an example of a differential pair tightly routed (5 mil lines and 5 mil spaces with a height above the plane of 10 mils). Figure 8 shows the same differential pair routed with 10

#### reature

### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

Figure 7: Tightly coupled differential pair.

mil spacing. In order to achieve the same "100 ohm" differential impedance, the trace width was increased to 10 mils in the second case. The reason for this will be explained later. Both data paths are running at 3.125 Gb/S and are 30 inches long with copper thickness of ½ ounce or 0.7 mils (18 microns).

This method of viewing signal quality is called an eye diagram. It is created by setting up a storage oscilloscope so that one bit period is visible on the screen, and then the data path is exercised with thousands of randomly generated data bits. Eventually, the worst-case bit pattern will be captured, allowing assessment of the quality of the data path.

Notice that the signal amplitude or the eye opening is larger in the loosely coupled case than in the tightly coupled one. The reason for this is higher skin effect loss with the 5-mil trace used in the tightly coupled case. A consequence of crowding traces close to each other is that each trace drives the impedance of the other down due to added parasitic capacitance. Higher parasitic capacitance on a transmission line always drives impedance down. In order to get back to the 50 ohms needed on each trace to meet the 100-ohm differential impedance requirement, the trace must be narrowed resulting in higher skin effect loss. Jitter is also higher in the tightly coupled case.

As noted above, one consequence of tight coupling is higher skin effect loss. A second, and more consequence is that the two traces must always be kept tightly coupled along their entire length. Figure 9 illustrates what happens to the differential impedance when each of

# Where can I find a list of high-speed PCB materials ?

We have compiled a comprehensive list of high-speed materials and the manufacturers who distribute their products in North America.

Check it out today, just click below!

### www.HIGHSPEEDPCBMATERIALS.com

#### reature

### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

Figure 9: Tightly spaced and loosely spaced differential pair.

the two pairs in Figures 7 and 8 is separated to weave through a 1 mm pitch BGA or other pin field where it is not possible to maintain the tight spacing.

Both differential pairs are spaced 10 mils above the plane over which they are routed. Trace and spacing for Figure 7 is 5 mil lines and 5 mil spaces. Trace and spacing in Figure 8 is 10 mil lines and 10 mil spaces.

Notice that the differential impedance of the tightly coupled pair increases to 140 ohms when the traces are separated. Said another way, the individual impedance of one trace when separated from its partner is 70 ohms while the loosely coupled pair changes to 109 ohms or a single-ended impedance of 54.5 ohms.

#### **DIFFERENTIAL SIGNAL DESIGN, PART 1** continues

The reason the single-ended impedance of the tightly coupled pair is so high when the traces are separated is that introducing any metal, whether a trace or a plane fill, close to a transmission line adds parasitic capacitance resulting in a lowering of the impedance. In order to bring the impedance back to the desired 50 ohms, the trace must be made narrower, in this case to 5 mils. When the metal is removed from the near field, this added parasitic capacitance goes away and the single-ended impedance of the trace returns to 70 ohms.

As long as skin effect loss is not an issue, tightly coupled traces work fine. However, it is necessary to maintain the tight coupling along the entire length in order to avoid reflection problems. In many cases this is a severe routing handicap. A restriction that comes to mind is that it will not be possible to route differential pairs through the pin field of a high pin count 1 mm BGA. **PCBDESICN**

*Part 2 will continue in the September issue of The PCB Design Magazine.*

#### References

1. Child, Jeff, "Low-Voltage Differential Signaling (LVDS) Reports for Duty." *Electronic Design*. May 25, 1998.

2. Ritchey, Lee W, "How to Design a Differential Signaling Circuit." *Printed Circuit Design*, March 1999.

3. Crisafulli, Kellee & Kaufer, Steve, "Terminating Differential Signals on PCBs." *Printed Circuit Design*, March 1999.

4. EDN Staff, "Line Drivers/Receivers Conform to New LVDS Standards." EDN, June 10, 1999.

5. Johnson, Howard, "Differential Termination." EDN, June 5, 2000.

6. Desposito, Joseph, "Transceiver Chip Replaces Parallel Backplanes with High-Speed Serial Links." *Electronic Design*, February 7, 2000.

7. Goldie, John & Nicholson, Guy, "A Case for Low Voltage Differential Signaling as the Ubiquitous Interconnect Technology." *Electronic Systems*, March 1999.

8. Rothermel, Brent R, etal, "Practical Guidelines for Implementing 5 GB/S in Copper Today, and a Roadmap to 10 GB/S." DesignCon2000. 9. Cohen, Tom, etal, "Design Considerations for Gigabit Backplane Systems." Design-Con2000.

10. Patel, Guatam, et al., "Gigabit Backplane Design, Simulation and Measurement." Design-Con2001.

11. Bogatin, Eric, "The Return Current in a Transmission Line." *Printed Circuit Design*, Aug. 2002.

12. Bogatin, Eric, "When Should I Worry About Lossy Lines?" *Printed Circuit Design and Manufacture*, March 2005.

13. Bogatin, Eric, "A Designer's Guide to High Speed Serial Links." *Printed Circuit Design*, June 2005.

14. Clink, James, "Maximizing 10 GB/S Transmission Paths in Copper Backplanes." DesignCon 2003, January 2003.

15. Johnson, Howard, "Modeling Skin Effect Loss." EDN, April 2001.

16. Johnson, Howard, "Who's Afraid of the Big, Bad Bend? Right Angle Turns." EDN, May 2000.

17. Johnson, Howard, "Differential Signaling, Measuring Differential Impedance." EDN, January 2000

18. Bogatin, Eric, "Skewering Skew, Laminate Weave Induces Skew." *Printed Circuit Design and Manufacture*, April 2005.

19. Theorin, et al., "Differential TDR Testing Techniques." W. L. Gore, March 1998.

20. Brooks, Douglas. "90 Degree Corners, The Final Turn." *Printed Circuit Design*, January 1998.

21. Brist, Gary et al., "Non-classical conductor Losses Due to Copper Foil Treatment." *CircuiTree*, May 2005.

Lee Ritchey is founder and president of Speeding Edge. A longtime PCB design instructor and consultant, Ritchey is the author of

*Right the First Time: A Practical Handbook of High-Speed PCB and System Design.*

### **BROOKS' BITS**

### How Electromagnetic Fields Determine Impedance, Part 1

Douglas Brooks, Ph.D.

ULTRACAD DESIGN

We talk a lot about trace dimensions and relationships when discussing signal integrity issues. In particular, we like to talk about how close traces are to underlying planes and how close traces are to each other. But there is another way to think about things that is sometimes much more practical and intuitive, and that is by thinking about the electromagnetic field *around* the trace(s) we are considering. The position and shape of the electromagnetic field can tell us a lot about trace impedance, EMI and crosstalk coupling, and signal propagation speed.

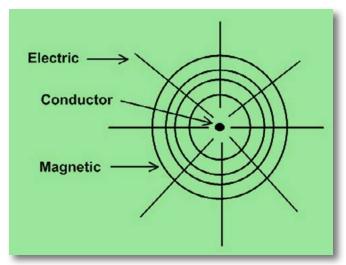

When a current flows down a conductor (Figure 1) an electric field and a magnetic field radiates away from that conductor. Collectively, this is called the electromagnetic field. What is important to note is that this field *always* exists. Furthermore, the electromagnetic field and the current are inseparable. That is: (a) the electric field can't move ahead of the magnetic field; (b) the magnetic field can't move ahead of the electric field; and (c) neither field can get ahead of or fall behind the current itself. They all have to move together along the conductor.

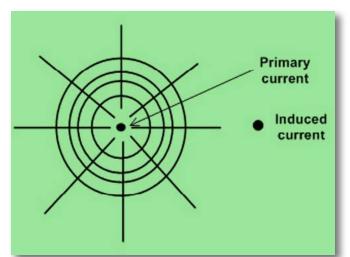

Another point that should be intuitive needs to be said anyway. It is that important. If a current causes an electromagnetic field to exist around a conductor, then a changing current causes a changing electromagnetic field to exist around the conductor.

A changing current in a conductor induces a current in an adjacent conductor (Figure 2). This is related to Faraday's Law of Magnetic Induction and is also the principle behind a generator, a transformer, EMI, and crosstalk.

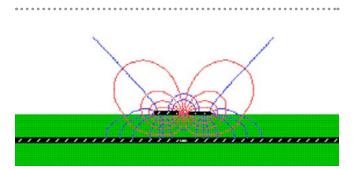

Some signal integrity simulators allow us to visualize the electromagnetic field

Figure 1: The electromagnetic field around a conductor when current flows.

Figure 2: A changing primary current in a conductor induces a current in a nearby conductor.

# Prototron Time

### Delivering your Boards On Spec and On Time

### Don't Be Late!

LEARN WHAT LATE BOARDS MAY BE COSTING YOU AND HOW WE CAN HELP.

### brooks' bits

#### HOW ELECTROMAGNETIC FIELDS DETERMINE IMPEDANCE, PART 1 continues

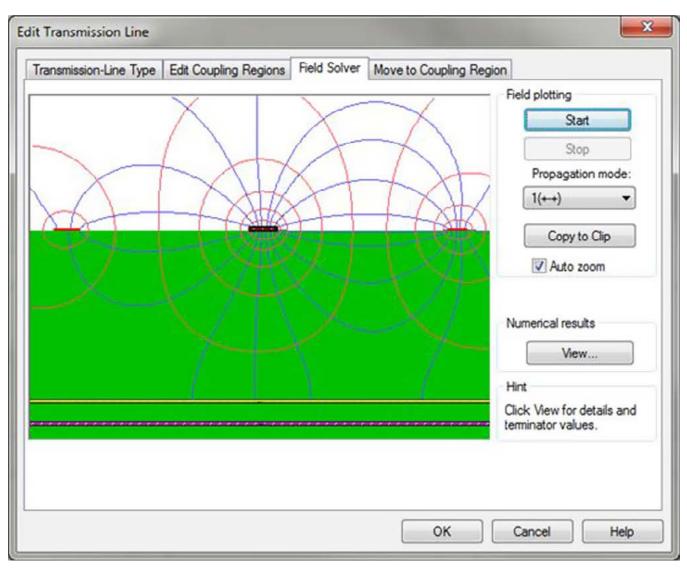

Figure 3: Electromagnetic field illustration shown in HyperLynx.

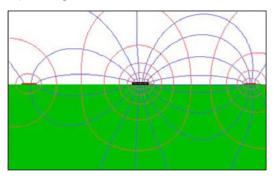

around a PCB trace. The Mentor Graphics HyperLynx tool is one of them. Figure 3 is an image of the Field Solver screen under the Edit Transmission Line menu. The blue lines radiating away from the trace are the electric field lines, and the orange lines circling around the trace are the magnetic field lines. We can infer several things from thinking about and visualizing the electromagnetic field. This column addresses what the field can tell us about the impedance of the trace.

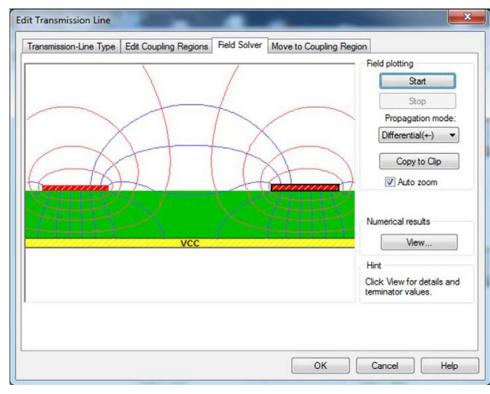

Figure 4 illustrates the electromagnetic field around an 8 mil wide, 0.5 oz. trace, 6

mils above the underlying plane. The trace is part of a differential pair. The second trace separation is 20 mils from the first. The single-ended characteristic impedance of each trace is given by the model as 59.6 ohms. (This results in a Zdiff of 114.9 ohms.)

Figure 5 shows the field patterns for a pair of 16 mil traces, 12 mils above the plane, and 1.0 oz. in thickness, separated by 40 mils. It looks much like Figure 4. In fact, it almost looks like we have repeated Figure 4 by mistake. But we haven't! The field patterns look identical. In fact, the field

### HOW ELECTROMAGNETIC FIELDS DETERMINE IMPEDANCE, PART 1 continues

Figure 4: An 8 mil trace, 20 mil separation, 6 mil above plane, 0.5 oz. thick.

Figure 5: A 16 mil trace, 40 mil separation, 12 mil above plane, 1.0 oz. thick.

patterns are identical! And the single-ended characteristic impedance is identical at 59.6 ohms. (And the Zdiff is also identical at 114.9 ohms.) In fact, everything is identical; it's just scaled.

This illustrates a very important point. impedance The is not necessarily determined by the stackup dimensions. Several combinadifferent tions of stackup dimensions will lead to the same characteristic impedance. The impedance of the trace is determined by the electromagnetic field distribution. If we scale the dimensions, we don't change the electromagnetic field pattern, and therefore we don't change the impedance.

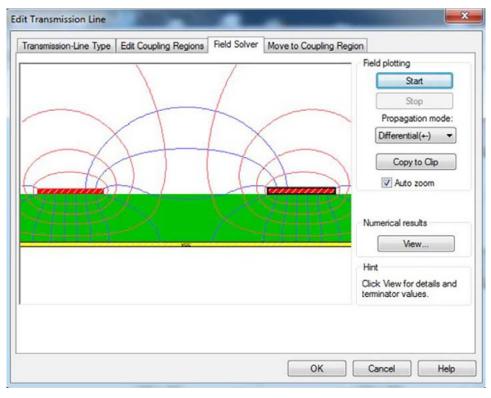

This illustrates one example of how visualizing the electromagnetic field pattern (or in this case the difference in the pattern between two different stackups) can help us visualize some of the parameters related to the traces. To illustrate this point another way, consider Figure 6. This is the same stackup as Figure 4. but with a trace separation from the plane of only 3 mils. Looking at the figure, we see that more of the

### brooks' bits

#### HOW ELECTROMAGNETIC FIELDS DETERMINE IMPEDANCE, PART 1 continues

Figure 6: 8 mil trace, 20 mil separation, 3 mil above plane, 0.5 oz. thick.

field is captured between the trace(s) and the plane. This would imply that the capacitance between the trace and the plane is greater (than in Figure 4), and that therefore the characteristic impedance would have gone down. In fact, the model gives the impedance as 39.5 ohms.

When thinking about signal integrity issues, train yourself to think in terms of what the electromagnetic field might look like, or what it might look like if some change were made. This can result in some quick and intuitive insights about what will happen on your boards. **PCBDESIGN**

Douglas Brooks, Ph.D., is the founder of UltraCAD Design Inc. He has written numerous articles in several disciplines and held signal integrity seminars around the world. He has spent most of his career in the

electronics industry in positions of engineering, marketing, management, and as CEO of several companies. Prentice Hall recently published Brooks' latest book, <u>PCB Currents: How</u> <u>They Flow, How They React</u>. Visit his website at <u>www.ultracad.com</u>.

**Advanced PCB Solutions**

# OUR TECHNOLOGY GIVES DESIGNERS EVERY POSSIBLE ADVANTAGE

Landless Via is an exciting new technology that allows Design Engineers to resolve space restrictions by eliminating via pad requirements. Our plating methods eliminate the need for an annular ring to facilitate proper plating in the hole and on the surface, giving our customers a design advantage.

CLICK TO LEARN MORE

Candor Industries, Inc.

WE DON'T JUST SAY I

...WE CAN PROVE IT!

www.candorind.com

416 736 6306

#### PragoBoard Joins FabStream's Network of PCB Makers

FabStream, the integrated PCB design and manufacturing solution developed by DownStream Technologies and targeted at the DIY electronics market, has announced that PragoBoard has become the sixth PCB manufacturer to join the FabStream network of global PCB manufacturers.

### Graphic Plc Acquires Flex PCB Maker Calflex

Graphic Plc. has acquired the assets of Californiabased Calflex, a flex PCB specialist with 30 years experience in supplying military, aerospace, and medical industries. The Graphic Group now has a real world presence of PCB manufacturing with specialist IMS plants in the UK, the U.S., Europe, and Asia.

### Endicott Interconnect Files for

#### **Chapter 11 Protection**

Endicott Interconnect Technologies filed for Chapter 11 protection in U.S. Bankruptcy Court on July 10. According to court documents, the New York-based company owes between \$50 and \$100 million; former parent company IBM is El's largest creditor, with \$5.5 million in unsecured debt.

#### IPC APEX EXPO 2014: 95% of Booth Space Sold

The show sold out of exhibitor space last year and 2014 is promising to sell out as well. "Our number one priority is to give our exhibitors and attendees the best return on their investments, giving them an opportunity to grow their businesses and increase revenue," said Alicia Balonek, senior director of trade shows and events.

### German PCB Market on the Rise

Sales of PCBs in Germany were up by 5.7% in April, year-on-year, according to the Central Association of PCB and Electronic Systems. This is the third consecutive month of growth in 2013.

### **Gorilla Circuits Lands Zeta Certificate**

Integral Technology, Inc. has announced that PCB manufacturer Gorilla Circuits is the next PCB fabricator certified to produce circuit boards using Inte-

gral's revolutionary Zeta® glass-free laminate and film solutions for rigid PCB applications. "Gorilla Circuits is a shining example of how entrepreneurial vision can guide a company to success even in a down economy," stated Integral President Ken Parent. "Gorilla's commitment to engineering quality and reliability makes them a valued member of the Zeta® team."

### Multek: New Interconnect Technology Center In Silicon Valley

"Our Interconnect Technology Center will focus on future technologies for the printed circuit board industry with the understanding that critical decisions are made specific to connections within the board and the device as a whole," said Franck Lize, president.

### N.A. May PCB Shipments Down 4.4%, Bookings Up 8.3%

"PCB sales and orders have been below last year's levels for most months of the past year, but they have been improving in recent months," said Sharon Starr, IPC director of market research. "Order growth rates have improved faster than sales growth rates, which accounts for the positive book-to-bill ratios of past five months," she explained.

### Maskless Completes Series D Financing; Collaborates with CBT

Bill Elder, president and CEO of MLI said, "I am very pleased to have closed this round of financing that will enable MLI to continue its rapid growth into the global PCB market. In addition to the new funding, as part of the collaboration between MLI and CBT, MLI will be able to integrate its existing direct imaging technology into CBT's vast array of lithography products, all focused on the PCB industry."

### Epec, Suncoast Digital Technology

### Join Forces

Ed McMahon, CEO of Epec, commented, "We are very excited to welcome Suncoast Digital into the growing Epec family. Paul Knupke, Joe Frangione, and their dedicated team have built a tremendous reputation that seamlessly fits into Epec's proven business model, focusing on providing customers with high-level engineered solutions."

# PCB MANUFACTURING SUCCESS!

### We Have a Better Way to Predict

DFMStream provides powerful DFM capabilities in an easy-to-use tool suite designed to help engineers and designers verify design and manufacturing rules on PCB design databases, Gerber and NC data any time during the PCB design cycle. DFMStream bridges the gap between engineering and fabrication, helps save valuable time and reduces new product introduction bottle necks.

- Provides powerful DFM functionality

- Easy to learn, even for infrequent users

- Easy to implement as part of the everyday design flow

- Saves time and increases productivity

For more information visit downstreamtech.com or call 800-535-3226

#### Netlist errors are quickly validated in DFMStream

Define DFM checks by area so components such as BGAs can be verified with unique rules different from rest of design

#### **QUIET POWER**

## **Don't Forget to Terminate Cables**

#### **by Istvan Novak** ORACLE

We know that in high-speed signal integrity measurements, one of the first rules is to properly terminate traces and cables. However, many of our PDN measurements may be limited to lower frequencies, such as measuring the switching ripple of a DC-DC converter. Do we really need to terminate our measurement cables if the signal we want to measure is the switching ripple of a converter running at 1 MHz? We may think that termination is not needed or does not matter in this case, but we may be in for some surprises!

Let us look at the output ripple of the LTM4604 converter<sup>1</sup>, which was our device under test in an <u>earlier column<sup>2</sup></u>. The converter is powered from a 4.5V battery pack, and its output voltage is set to 1.2V. An approximate 1A DC load is created by a small incandescent bulb. The output ripple is measured by a Tektronix TDS540B oscilloscope that I recently bought on eBay. The 1 GS/s maximum real-time sampling rate and 500 MHz analog bandwidth, together with a maximum 1 mV/ div vertical sensitivity makes this category of

Figure 1: LTM4604AEV DC-DC converter evaluation module (courtesy of Linear Technologies), connected to CH1 of a Tektronix TDS540B oscilloscope through a coaxial cable.

oscilloscopes very useful for many PDN measurements even today. The setup is shown in Figure 1.

# **epec** *build to print* **DELIVERING QUALITY** *electronics* SINCE 1952.

# LEADER IN QUICK-TURN PCBs

With more than 100 dedicated employees throughout North America and Asia, Epec Engineered Technologies has become one of the fastest growing companies in the Industry.

- Controlled Impendance

- Many RoHS and RF Materials

- Heavy Copper/EXTREME Copper

### Thermal Clad

- Up to 34 Layers

- Fine Lines & Spaces

### **TECHNICAL ENGINEERING GUIDES**

Epec's new Product Guides are a must have for anyone in the engineered electronics industry. Click Here for Instant Access.

# **ONLINE PCB QUOTING SOLUTION**

Build your printed circuit boards quotes online 24/7 at your convenience. Every quote created is saved in your InstantPCBQuote<sup>™</sup> profile, which can easily be viewed, compared, ordered, and reordered at anytime.

Register Today and experience InstantPCBQuote<sup>™</sup> for yourself.

InstantPCBQuote fast.easy.24/7.

RoHS2 Certified Certified

TS-16949 ISO9001 ISO14001

Certified

174 Duchaine Blvd. | New Bedford, MA 02745 | Toll Free: (888) 995-5175 | www.epectec.com

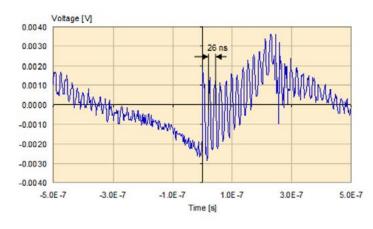

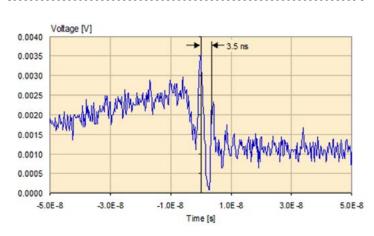

Figure 2: Output ripple of the DC-DC converter shown in Figure 1.

Figure 3: Output switching ripple measured with 50 ohm termination at the oscilloscope input.

Figure 4: Same waveform as in Figure 3, except zoomed in around the end of the ON period.

When we connect the output BNC socket to CH1 of the oscilloscope with a coaxial cable, we get a waveform shown in Figure 2.

Figure 2 shows approximately one full cycle of the converter, with the trigger point aligned to time zero. The ON time, shown by the positive ramp, is approximately 0.3 ms. The peak-to-peak ripple is below 10 mV, so everything makes sense, except we see a strong oscillation during the ON time with a 26 ns period. When we check the oscilloscope settings, we notice that, in order to show the small AC contents on top of the 1.2V DC, the autoscale feature uses AC coupling on the oscilloscope input. Checking further, we will notice that the input impedance is set to 1 MOhm. This 38 MHz ringing is caused by the reflections on the one-meter Belden RG 58C/U coaxial connecting cable. The coaxial cable has almost full reflections at both ends: an approximately +1 voltage reflection coefficient at the oscilloscope input and an approximately -1 voltage reflection coefficient at the DC-DC converter output. These conditions create a quarter-wave resonator with a resonance period of four times the one-way propagation delay. The unloaded propagation delay is 5.1 ns/m; with the load reactances at the input and output of the cable we may get a delay of 6.5ns, which results in a 38 MHz ringing frequency. We will notice by using different cables that the ringing frequency changes proportionally with the cable delay.

Unfortunately, the 38 MHz ringing frequency is not high enough so that we could count on eliminating it by switching on the customary 20 MHz BW limit option. The proper way to eliminate this ringing is to use a 50 ohm termination at the oscilloscope input. We can use either an external 50 ohm termination at the end of the cable and then we can keep the 1 MOhm input setting on the oscilloscope, or switch the oscilloscope input to 50 ohms. When we switch the oscilloscope input to 50 ohms (and leave the AC

### quiet power

#### **DON'T FORGET TO TERMINATE CABLES** continues

coupling setting), we get a warning reminding us that the 50 ohm input impedance together with the series capacitor providing the AC coupling will result in an increased high-pass cut-off frequency. Since in this case our lowest frequency component of interest is the 1MHz fundamental wave of the switching ripple, this will not degrade our measurement.

Using the 50 ohm termination setting on CH1 input, we get a ringing-free switching waveform as shown in Figure 3.

This waveform is much cleaner and it now allows us to hunt for finer details. For instance, as shown in Figure 4, if we zoom in on a switching transition, we will notice a high-frequency ringing; this time, on the other hand, the ringing is "real," generated by the DUT.

This high-frequency ringing now has a 3.5 ns period, corresponding to a 286 MHz frequency. As opposed to the 38 MHz ringing we had before, this ringing does not change as we change cables. By looking at the switch-node waveform, we can convince ourselves that this ringing is the parasitic ringing originated inside the DC-DC converter module and is the result of the fast switching edge exciting the parasitic inductances and capacitances associated with the switching elements. **PCBDESIGN**

#### References

1. Linear Technologies LTM4604AEV evaluation module, <u>www.linear.com</u>.

2. <u>"Do Not Measure Across Capacitors!"</u> February 2013 issue of The PCB Design Magazine.

Dr. Istvan Novak is a distinguished engineer at Oracle, working on signal and power integrity designs of mid-range servers and new technology developments. With 25 patents to his name, Novak is co-au-

thor of "Frequency-Domain Characterization of Power Distribution Networks." To contact Novak, click <u>here</u>.

### video Interview

### Zuken and AWR Team up for RF/PCB Design

by Real Time with... PCBDesign007

Zuken and AWR recently partnered up to provide a more integrated RF/ PCB design solution. This alliance should make life easier for PCB designers in the RF arena.

#### **BEYOND DESIGN**

# **Practical Signal Integrity**

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD | AUSTRALIA

"There are two types of designers: Those that have signal integrity problems and those that will." —Sun Microsystems.

If you are a digital designer, you will eventually have SI problems whether you like it or not. But all is not lost. If you learn to work with these issues, then you will soon become proficient with high-speed design.

Advances in semiconductor lithography enable IC manufacturers to ship smaller and smaller dies. However, Moore's law (1965) is still in effect: The number of transistors on ICs doubles every two years and will continue for at least 10 years. Arguably, the predictions about the law were short-sighted, and the paradigm will continue to apply as chip sizes continue to scale down. But keeping up with it is becoming more challenging. Intel for instance, changed transistor structure into 3D form, by placing transistors on top of each other, on the latest 22 nm process to enable them to continue shrinking silicon.

Each new generation of semiconductor process technology delivers greater levels of integration, higher performance and lower cost. However, these benefits are offset by increases in power consumption that seem to unavoidably accompany each reduction in feature size. In order to reduce power consumption, IC manufacturers have moved to lower core voltages and higher operating frequencies which of course mean high current requirements and faster edge rates.

Faster edge rates mean reflections and signal quality problems. So even when the package and your clock speed haven't changed, a problem may exist for legacy designs. The enhancements in driver edge rates have a significant impact on signal quality, crosstalk, timing and EMI. So whether you like it or not, welcome to the domain of high-speed design.

At U.S. Circuit, we had the vision to purpose-build our facility from the ground up with you, the customer, in mind. We invite you to step on in for a virtual tour of our state-of-the-art facility today. Welcome to U.S. Circuit!

U. S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 Ph: (760) 489-1413 Fax: (760) 489-2965 www.uscircuit.com

## Superior Quality Superior Service

Call for a Quote: (760) 489-1413 or email: rsojitra@uscircuit.com

ITAR Registered

ISO 9001:2008

MIL-PRF-55110G

#### **Impedance** Control

Impedance is the key factor that controls the stability of a design—it is the core issue of signal integrity methodology. At low frequencies, a PCB trace is almost an ideal circuit with little resistance, and without capacitance or inductance. Current follows the path of least resistance. But at high frequencies, alternating current circuit characteristics dominate, causing impedances, inductances and capacitances to become prevalent. Current then follows the path of least inductance. The impedance of an ideal lossless transmission line is related to the capacitance and inductance:

$$Zo = \sqrt{\frac{L}{C}}$$

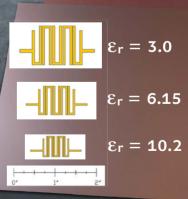

Equation 1

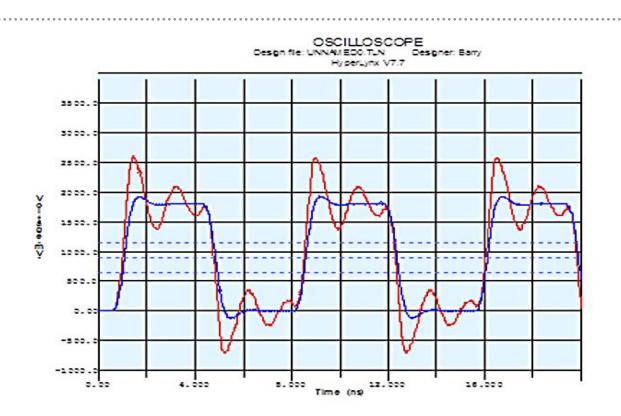

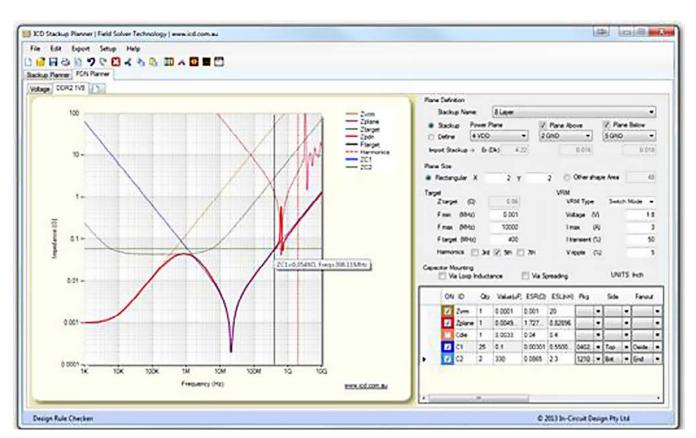

But this is very simplistic and the impedance should be simulated by a field solver (Figure 1) to obtain accurate values of impedance for each signal layer of the substrate. The impedance of the trace is extremely important, as any mismatch along the transmission path will result in a reduction in quality of the signal and possibly radiation of noise. For perfect transfer of energy, the impedance at the source must equal the impedance at the load. However, this is not usually the case and terminations are generally required at fast edge rates to limit ringing.

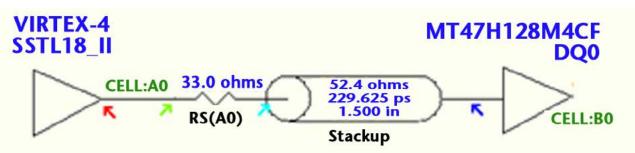

Figure 2 shows a typical scenario where there is a Virtex-4 driving into a 1.5" transmission line and then to the DDR2 receiver. The impedance of the driver is 20 ohms—its value is embedded in the devices IBIS model. Now, obviously, a 20 ohm driver does not match a 52.4 ohm transmission line.

The red waveform in Figure 3 shows the ringing of the un-terminated trace. However, once a 33 ohm series terminator is placed close to the driver, the impedances are matched resulting in the blue waveform. Notice that the rise time is slower now. There are, of course, different types of termination strategies but series is the best for point-to-point terminations because it slows down the edge rate without drawing extra current. Parallel terminations are typically used as end terminators on the address busses pulling the signal up to VTT.

| CD Stackup Planner   Feld Solver Technology   www.icd.com.ex |                   |                                                                                                                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                       |                                            |                                          | 10     |        |            |       |                |                       |  |

|--------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|--------------------------------------------|------------------------------------------|--------|--------|------------|-------|----------------|-----------------------|--|

| File Edit Import Export Setup Help                           |                   |                                                                                                                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                       |                                            |                                          |        | Co Cor | welfing II |       |                |                       |  |

| □ 日本目ので 日本当本目本目ので □                                          |                   |                                                                                                                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                       |                                            |                                          |        | 304.8  |            |       |                |                       |  |

| lacke                                                        | the second second | and second s |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 202.02       |                                       |                                            |                                          |        |        |            |       |                |                       |  |

|                                                              | _                 |                                                                                                                | And in case | and the second se | 10-01-02     | Laver Malayer 16 Laver 18 Laver My S  | tanin Ith                                  | 1                                        |        |        |            |       | mb             | 12                    |  |

| UNITS                                                        | 10.000            | -                                                                                                              | 2.50        | a la casa i s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Caller C. La | ICD STACKUP PLANNER FX                | 10,400                                     |                                          | 7.00.0 | 2018   |            |       |                |                       |  |

| UNK 25                                                       |                   |                                                                                                                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | Differential Pairs > 50/10            | series and the factor of such              | A state of the state of the state of the |        |        |            |       |                | Total Board Thickness |  |

|                                                              | N.                |                                                                                                                |             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Laver        | Material Type                         | ALC: 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Delectric                                | Conner | Trace  | Trace      | Count | Characteristic | Edge Coupled          |  |

|                                                              |                   |                                                                                                                | Meter       | C. C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Name         | · · · · · · · · · · · · · · · · · · · |                                            | Thickness                                |        |        | Vidth      |       | Impedance (Zs) |                       |  |

|                                                              |                   |                                                                                                                |             | Soldermask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | Defectors                             | 33                                         | 05                                       |        |        |            |       |                |                       |  |

| 1                                                            | 2                 | ï                                                                                                              | 4           | 5-gnal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Top          | Conductive                            |                                            |                                          | 0.7    | 12     | 5          | 0.22  | 50.12          | 97.4                  |  |

|                                                              |                   |                                                                                                                |             | Pieceg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | 370HR, 1080 , Re+ 64% (20Hz)          | 3.89                                       | 28                                       |        |        |            |       |                |                       |  |

| 2                                                            | 11                |                                                                                                                |             | Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OND          | Conductive                            |                                            |                                          | 1.4    |        |            |       |                |                       |  |

|                                                              | 1.1               |                                                                                                                |             | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 370HR . 2-3313 . Re+51% (20Hz)        | 4.23                                       | 8                                        |        |        |            |       |                |                       |  |