High-Frequency Materials for Lead-Free Soldering p.20

Design for Assembly: Components p.24

**Component Placement** p.50

## **DESIGN FOR ASSEMBLY**

## Improving Quality During Assembly with DFX

by Murad Kurwa and Jesus Tan, Page 10

avy

JL,

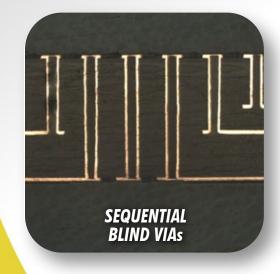

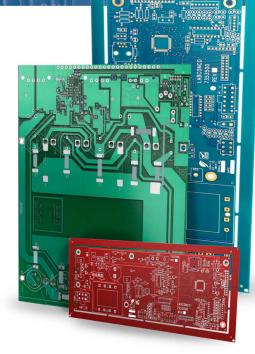

Colonial Circuits is currently pursuing its 32nd year as a full service manufacturer of high quality circuit boards. The company's 65 employees serve military, space, and commercial markets from its 40,000 square foot facility in historic Fredericksburg, Virginia.

Colonial's capabilities include multilayer constructions, a collection of rigid, flexible, and rigid/flex materials, blind/buried vias, and a variety of other skills not found in many shops. Lead times as short as 24 hours.

| Markets:        | Communication, Industrial, Medical,<br>Military/Aerospace                                                                               |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Board Types:    | Double-sided, Multilayer, Flex, Rigid-Flex                                                                                              |  |

| Mfg Volumes:    | Prototype, Small, Medium                                                                                                                |  |

| Other Services: | Quick turn-around, Other: Des n Workshops                                                                                               |  |

| Specialities    | Blind/buried vias, Controlled de transformer<br>Controlled Impedance, Filled/plu<br>copper, HDI, Sequential laminatio<br>CMCIA, heaters |  |

D 9001, ITAR registered, MIL-PRF-310 L-P-50884, MIL-PRF-55110, ROHS con her: MIL-I-45208, MIL-S-13949, MIL-S L-STD-275, NASA/NHB 5300.4(3I), NRC 10 CFR 50 B

## Click here to see a demo

## Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

## www.thepcblist.com

Click to see a partial list of registered OEMs!

## SMTA iNEMI **Medical Electronics SYMPOSIUM**

November 12-13, 2013 Embassy Suites, Milpitas, CA

## FEATURED EVENTS

Keynote Address — Tuesday, November 12, 2013 The Accelerating Technology Convergance in Medical Devices — Implications for the Future, Mark Kemp, President, Flextronics Medical

Panel Discussion — Wednesday, November 13, 2013 Key Issues Facing the Medical Electronics Industry — From the 2013 iNEMI Roadmap

>> Find out more at www.smta.org/medical

## **FEATURED CONTENT**

In the rush of meeting time-to-market deadlines, it's easy for PCB designers and design engineers to overlook issues related to assembly. But processes that take place downstream can still have an effect on your job on the front end. This month, our contributors provide a rundown of some assembly trends that designers need to be aware of, and they offer valuable tips on DFA as well.

## Discover the Best-in-Class Laminate for High Voltage, Tight-pitch PCB Designs

## **I-Speed® High Speed Digital Materials**

I-Speed laminate and prepreg products are manufactured with Isola's patented high-performance multifunctional resin system, reinforced with electrical grade (E-glass) glass fabric. This system delivers a 15% improvement in Z-axis expansion and offers 25% more electrical bandwidth (lower loss) than competitive products in this space. These properties coupled with superior moisture resistance at reflow, result in a product that bridges the gap from both a thermal and electrical perspective.

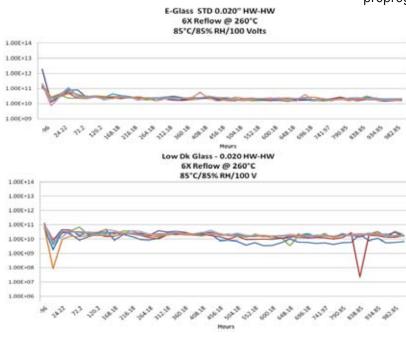

## **I-Speed CAF Test Vehicle Results**

- Passed: 85°C/85% RH/100V after 1,000 hours at 0.65 and 0.75 mm pitch

- Passed: 35°C/85% RH/10V after 500 hours at 1.0 mm pitch

## **I-Speed Features**

- Global constructions available in all regions

- Optimized constructions to improve lead-free performance

- Improved Z-axis CTE 2.70%

- IPC 4101 Rev. C /21 /24 /121 /124 /129

- A low Df product with a low cost of ownership

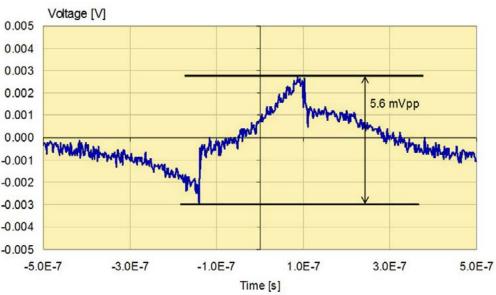

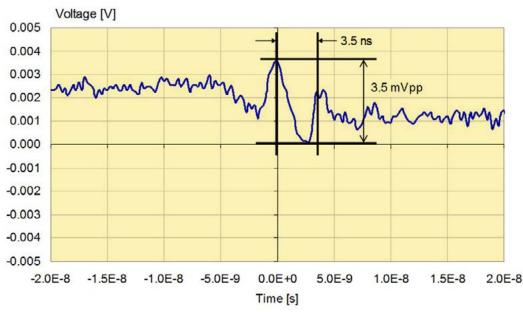

- VLP-2 (2 micron Rz copper) standard offering

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

## www.isola-group.com/i-speed

OCTOBER 2013

**VOLUME 2**

NUMBER 10

thepcbdesignmagazine.com

THE OPTIMUM

MAGAZINE

DEDICATED TO

PCB DESIGN

## CONTENTS

AN CONNECTOR PUBLICATION

ARTICLE 54 Designed for Manufacture? by Neil Day

**COLUMNS**

- **36 Impedance Matching: Terminations** by Barry Olney

- 46 Cable Quality Matters by Istvan Novak

- 60 Crazing and Conductive **Filament Formation** by Paul Reid

- 68 A Tale of **Two Materials** by Amit Bahl

**EXTRAS** 74 Events Calendar

75 Advertiser Index & Masthead

**VIDEO INTERVIEWS 18 Best Presentation for Materials Management**

58 Chinese Growth Fuels New **JTAG Product**

**SHORTS 18 New Tech Aids** Production of Organic Semiconductors

**43 Tiny Computer** with Carbon Nanotube **Transistors**

## **TOP TEN NEWS HIGHLIGHTS**

- 44 PCB007

- 66 Mil/Aero007

- 72 PCBDesign007

" Providing Solutions to Board Fabrication Challenges"

## FROM CONCEPT TO COMPLETION

## **Solutions for Every Complex Situation**

At Multilayer Technology we have the skills and the knowledge to be able to say "Yes We Can!" to your most complex design requirements.

We specialize in High-Speed Digital and RF Design constraints. In addition, we offer the following solution-based services:

- Extensive Exotic Material Processing

- Pre-DFM Services Available

- State-of-the-Art Industry Leading Processes

- Space-Based Reliability Requirements Standard

**REQUEST A QUOTE**

WWW.MULTILAYER.COM

Multilayer Technology 3835 Conflans Rd Irving, TX 75061-3914

(972) 790-0062

Mil-PRF-55110

### THE SHAUGHNESSY REPORT

## **PCB West a Good Omen for 2014**

by Andy Shaughnessy I-CONNECT007

It had been a few years since I last attended PCB West, but the show has been growing steadily over the past few years. I'm glad I went this year. It's always great to see old friends and meet new ones.

This event kicked off with the Zuken party. The company plans to spend millions expanding its presence in North America, starting with a new Silicon Valley office, and they held a poolside party at the Hyatt Regency Santa Clara. The weather cooperated, and a talented jazz band set the mood for the night.

Zuken showed off some of their customers' products: A Fiat 500 and a few Zero electric motorcycles were parked around the pool, bracketing a great sushi selection. Customers and potential customers mingled throughout the night; Zuken has been encouraging direct communication between non-customers and customers, so potential users can get information about Zuken's tools first-hand. Speakers included Zuken COO Jinya Katsube, GM of Zuken Americas David Gullickson, and Synopsys CEO Aart de Geus, who discussed the companies' partnership. And Senior Technical Marketing Manager Humair Mandavia detailed the future of the Silicon Valley office, which he will be heading up.

The exhibition opened on Wednesday, and attendees jammed the aisles for much of the day. I didn't see any real dead times, though traffic did slow down after lunch. At 5 pm, EMA Design Automation turned on the margarita machine, Altium got the beer and wine flowing, and the place was packed again.

Now at 75 exhibitors (not quite 2000 levels, but moving that way), PCB West was buzzing. The exhibitors I spoke with all support the oneday show, anchored by a three-day technical conference. A show like this isn't too much of a budgetary bite for these small and mid-sized companies.

#### PCB WEST A GOOD OMEN FOR 2014 continues

#### **On the Show Floor**

• Nolan Johnson of Sunstone Circuits said the company is continuing to grow. Sunstone recently introduced a new version of its PCB123 design tool.

• The DownStream Technologies booth stayed busy, with founder Rick Almeida discussing new solutions such as SoloPCB. Down-Stream took home a New Product Introduction award for SoloPCB.

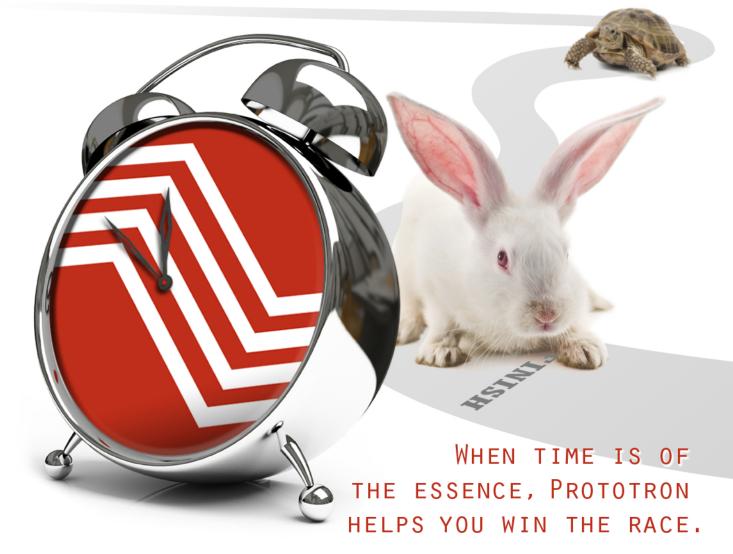

• Prototron Circuits' Dave Ryder and Mark Thompson said the company has been slammed for months. Thompson has barely had time to work on his hobby: Flying and restoring old airplanes.

• Colonial Circuits Sales Manager Wendy Osborn said the company has been busy, and they plan to keep investing in American-made equipment.

• Gary Carter, CAD manager at Fujitsu Network Communications, showed off two more PCBs that have been manufactured by different fabricators – Sanmina-SCI and Sierra Circuits – using the IPC-2581 data format. The boards were designed on Cadence Allegro PCB design software. This marks three boards that have been successfully fabricated with the upand-coming IPC-2581 format, and the first to be created using Frontline Genesis fabrication software.

• Semblant is seeing more companies select the Semblant Plasma Finish (SPF) and conformal coatings. The company expects to have solid growth over the next year.

• Sierra Circuits' Amit Bahl said the fabrica-

tor continues to experience steady growth, and he sees a great 2014 for the company.

• Bay Area Circuits' Peter Brissette said the company has moved into a larger facility in Fremont, California. The fabricator held an open house to celebrate the move, which Brissette believes will lead to increased turnaround times.

• Leo Lambert of EPTAC said the company has expanded its training courses. Now, EPTAC has begun offering IPC Designer Certification, in addition to its manufacturing curriculum.

All in all, PCB West was a great show, and a good omen for the electronics community and the trade show season. At I-Connect007, we're getting ready for SMTA International, October 15–16, in Fort Worth, Texas. Next, we move on to productronica, November 12–15, in Munich, Germany.

We'll be providing <u>Real Time</u> video coverage of both of these shows, bringing you interviews with the industry's top technologists and managers. Then, in 2014, we're off to DesignCon, IPC APEX EXPO, CPCA, and NEPCON China.

See you at the shows! **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 13 years. He can be reached by clicking here.

## **Improving Quality During Assembly with DFX**

#### by Murad Kurwa and Jesus Tan FLEXTRONICS

SUMMARY: The number of DFM issues reported on a PCBA is inversely proportional to the components' pitch values. The authors discuss the problems facing designers who use cutting-edge BGAs, and the Flextronics DFX process that detected them before mass production.

Engagements between contract manufacturers and product companies can take place at various points in the product life cycle. However, it's very common for manufacturers to engage with product companies in the later stages of the product life cycle, during product transfer to mass production. This is the stage when companies tend to face some tough challenges such as launching products on time, meeting target cost, and maintaining quality and performance goals.

Manufacturing success is enabled by a robust product design, and design for manufacturing (DFM) is the methodology or art of designing a product in such a way that it is easy to manufacture. DFM also helps facilitate the manufacturing process in order to reduce the overall manufacturing costs.

DFM involves several types of analyses that are as diverse as products in the industry, and can consist of adjacent areas such as "design for" printed circuit board fabrication, assembly, enclosure, test, reliability and cost. In addition to core manufacturing processes, there are other areas of support including design for supply chain, design for automation and design for repair. These areas are becoming more and more important as the strength of labor arbitrage is diminishing, making way for "right-shoring" products in different parts of the world.

All of these elements are grouped under the terminology "Design for X" (DFX), with the X as a variable for the combination of analysis types that can be triggered at different stages of the product life cycle. Regardless of the variables used, it is well understood in the manufacturing community that all the functions previously described have the highest potential on return of investment if aligned during the early stages of product design and development.

## Murrietta Circuits: The Integrated Solution A lot of quality under one roof.

We're proud of our commitment to quality. Delivering the best design, fabrication, assembly and test is what we're all about. Murrietta Circuits: everything you need from one company.

#### **IMPROVING QUALITY DURING ASSEMBLY WITH DFX** continues

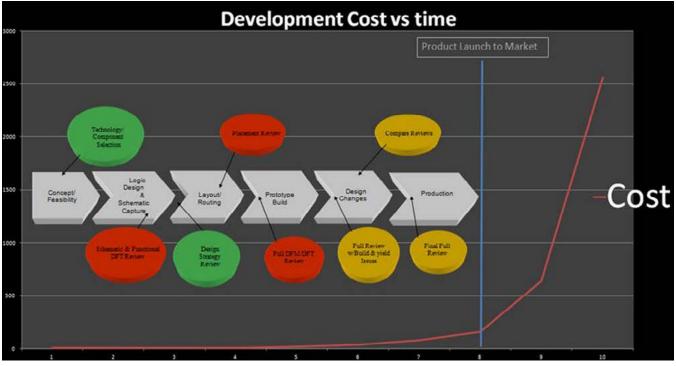

Figure 1: Development cost vs. time.

DFM has also been a crucial part of successful product development and an important methodology that is driven by concurrent engineering and time-to-market models. All the actions around this process are most effective when DFM is done at the earliest phase of the design or when the product is still being conceptualized. As the product approaches mass volume build, it becomes increasingly difficult and costly to implement modifications and design improvements to fix DFM challenges. We recommend engaging your DFX team as early as possible in the product development phases (Figure 1).

Successful DFX engagement includes collaboration and communication between the company's designers and the manufacturer. Early collaboration can help prevent potential issues on the design bench, reduce overall timeto-market risk, and eliminate additional investments to repeat prototype samples before entering the new product introduction stage.

In most cases, the tools used to perform the DFM analysis are sophisticated CAD software tools, some of which specialize in circuit board analysis, mechanical and thermal analysis, and

simulation such as assembly times/cost simulation or reliability simulation. Every tool is used in different stages of the design development process, depending on whether the product requirements and functions use some of the subanalysis or not.

### **Case Study**

The DFM process has different development phases required for each product. To serve as an example for this discussion, we will focus on the technology component selection for circuit board assemblies and its correlation with the production yield.

The number of DFM issues reported on a printed circuit board assembly (PCBA) is inversely proportional to the pitch value of the components, so it is worthwhile to revisit what packages the designers are using.

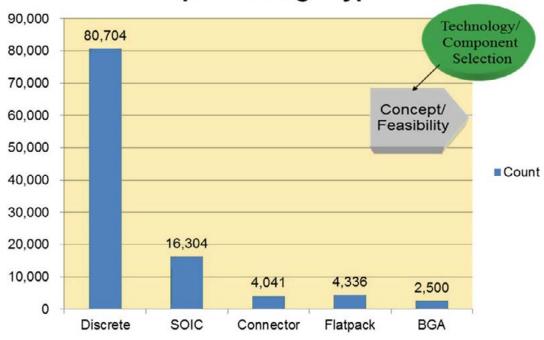

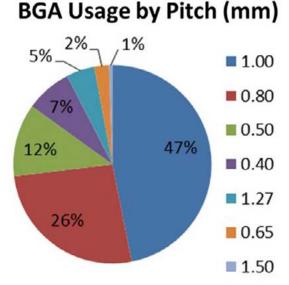

Figure 2 depicts the packages selected for different products built by Flextronics. As of September 2013, the Flextronics Component Team has created 114,875 unique geometric packages for use in DFM analyses. A full 70% of them are discrete parts and 2,500 of them are BGA packages. BGAs are among the top five

**IMPROVING QUALITY DURING ASSEMBLY WITH DFX** continues

## Top 5 Package Types

Figure 2: Top five package types used by projects at Flextronics.

package types used at Flextronics. This is due primarily to the high-velocity class of products we manufacture, combined with today's technology trends.

Almost 50% of the designs that featured BGAs utilized a 1.0 mm pitch followed by 0.8 mm pitch BGAs, both of which are prevalent in large and complex infrastructure products. On the other hand, 17% are fine pitch, 0.50 mm and 0.40 mm BGAs, which are commonly found on handheld devices (Figure 3) such as mobile phones.

Now, we'll focus on BGA usage trends on designs. 1.0 mm BGAs are commonly used in lowcost and low-power complex programmable logic devices (CPLDs). These components are selected because they save board real estate in designs of main logic boards, offer more density and a greater footprint in terms of input/output signals.

### **Challenges and Recommendations**

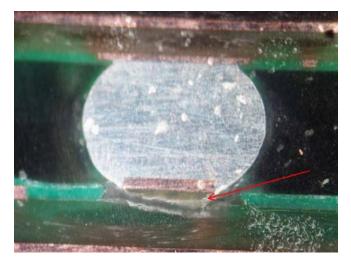

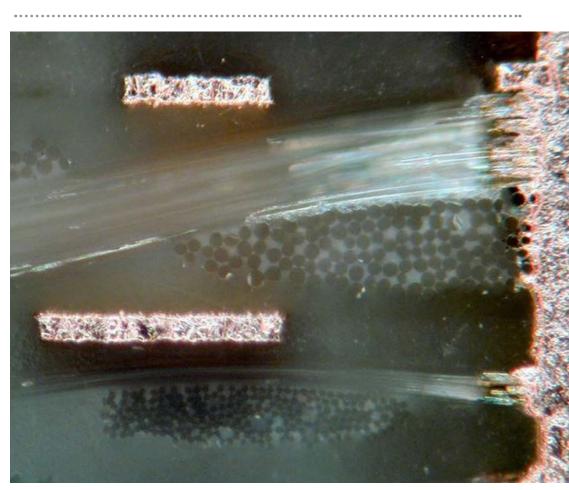

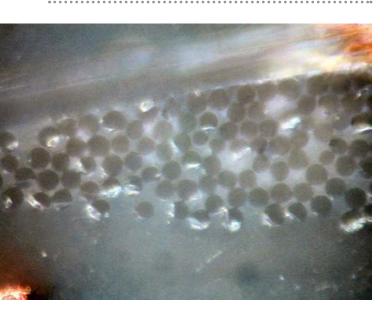

BGAs with 1.0 mm pitch usually involve a high pin count and relatively larger body size. This type of BGA is prone to component warp during thermal cycling, so it is important to de-

Figure 3: BGA usage by pitch, as recorded at Flextronics.

sign the corner pads to minimize the PCB pad lift or pad cratering (Figure 4).

If this issue is detected early in the design, steps can be taken to minimize the pad lifting on corner pads, such as connecting the corner

October 2013 • The PCB Design Magazine 13

#### reature

#### **IMPROVING QUALITY DURING ASSEMBLY WITH DFX** continues

Figure 4: Sample of PCB pad lift.

pads to wider copper trace. Another method is to use a soldermask-defined pad. If the design cannot be changed, then the manufacturer needs to implement alternate or secondary processes such as adding glue on corners or underfill on affected BGA parts, which would increase the cycle time on the assembly. This process requires the addition of materials such as adhesives over the original design, and increases process steps.

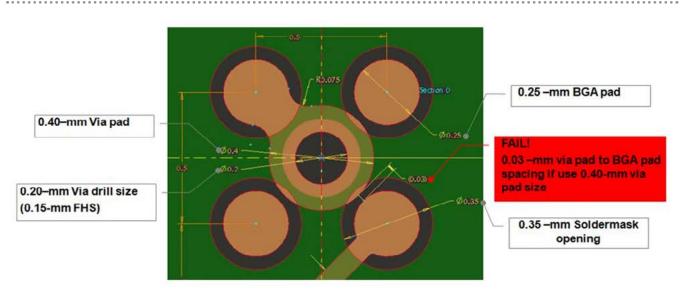

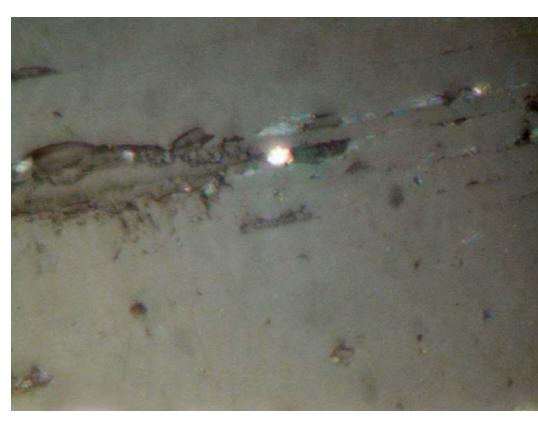

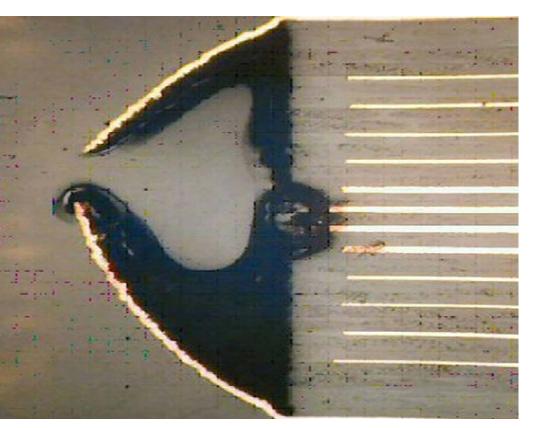

The smaller the pitch of the BGA, the tougher it becomes to achieve the optimal PCB design that meets all design rules. As the pitch approaches 0.50 mm, the designer must decide whether to use microvias to meet the pad size recommended by contract manufacturers, or sacrifice the pad size and then route fine traces in between pads to save PCB cost. Figure 5 shows how difficult it is to add through-hole via in between fine pitch BGA pads.

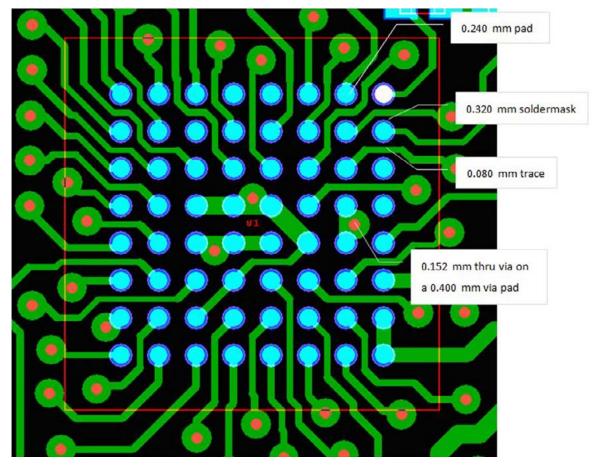

As much as possible, steps need to be taken to avoid using a microvia to save on PCB cost. This example below is a 0.50 mm pitch BGA footprint that got away from microvia.

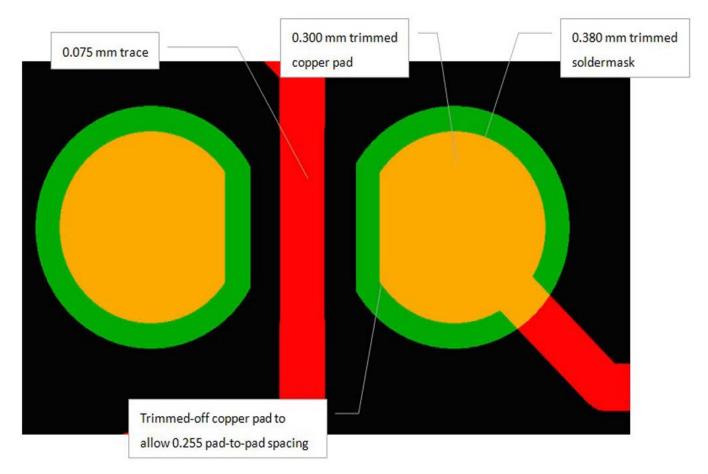

Another way of avoiding a microvia on a 0.50 mm BGA is to trim off a portion of the pads to make way to route copper trace in between BGA pads (Figure 7).

For BGA pitch 0.80 mm and below, if underfill and underfill rework is required, a DFX analysis would recommend soldermask-defined pads for a higher rework yield, except for 0.3 mm pitch CSP due to PCB fabrication limitations.

If DFX is performed properly and early on during the product development phase, both customer and manufacturer can benefit by making the design more manufacturable prior to mass production.

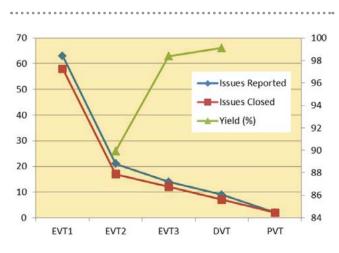

Figure 8 is based on actual data collected during product development. At the start of the DFM analysis in this case, 58 out of 63 issues were fixed by the designer, and then as the product development progressed, DFM issues

Figure 5: A 0.50 mm pitch BGA pad design with through-hole via.

AMERICA'S OLDEST, A HISTORY OF INNOVATION.

## GIVE YOUR END PRODUCT THE TECHNOLOGY IT DESERVES.

## CONCEPT THROUGH PRODUCTION

**epec** *build to print electronics*

RoHS2 TS-16949 ISO9001 ISO14001 Certified Certified Certified

#### reature

#### **IMPROVING QUALITY DURING ASSEMBLY WITH DFX** continues

Figure 6: Sample of 0.50 mm BGA pad design.

reported were reduced, while the first-pass yield became higher. This is a simple demonstration of how DFM analysis can help in identifying the manufacturing risks and, by rectifying the design to address the DFM challenges, can result in a higher yield, which is the ultimate goal of manufacturing.

Engineering validation trials (EVT) that most often involve non-commercial and non-form factor designs are the best opportunities for starting DFX. This can lead to some iterative processes, which in turn lead to design validation trials (DVT). During this stage, more end-product and close to end-product are tested and validated to ensure performance meets specifications.

Furthermore, at this stage, production, tooling, and equipment including layout is designed, all of which is ultimately tested during product validation trails (PVT). At the PVT stage, one would expect very few DFX issues or violations, and when found, they are typically minor and can be addressed through a simple process optimization exercise, not product redesign.

### Conclusions

In summary, with an increase in innovative product development, new product markets and a rise in customer demand for better products, it is imperative for OEMs and ODMs to partner with the contract manufacturer to apply DFX early in the design cycle.

More and more design check cycles are now co-managed by the designer and the manufacturer, who both share responsibilities and reduce the development cycle. DFX has also led to more use of simulation techniques such as finite element analysis (FEA) traditionally used for large form factor products or industrial product design. FEA includes both stress-strain predictions and thermal simulation, and both

## **IMPROVING QUALITY DURING ASSEMBLY WITH DFX** continues

Figure 7: Alternate design for 0.50 mm BGA.

are now commonly used in Flextronics design centers as well as by the Central Advanced Engineering Group.

Figure 8: Correlation between DFA issues and manufacturing yield.

Contract manufacturers must work closely with customers to bring products to mass production and meet the customers' targets and goals. Early communication with the PCB designer and a robust DFX process can help reduce the number of design issues found during fabrication and assembly. **PCBDESIGN**

Murad Kurwa is vice president of Flextronics Advanced Engineering.

Jesus Tan is Asia DFX manager of the advanced engineering group at Flextronics.

## video interview

## **Best Presentation for Materials Management**

## by Real Time with... NEPCON South China

Mentor Graphics' Valor products have long been high-end leaders for front-end engineering processes. Patrik Eriksson explains how Mentor continues to broaden its reach with process preparations and total materials management tools for design through assembly.

## New Tech Aids Production of Organic Semiconductors

Research and development on organic semiconductors has intensified in recent years. Organic semiconductors can be used in various applications such as organic solar cells, flexible displays, organic photodetectors and various other types of sensors.

Current methods for patterning organic semiconductors include shadow masking and inkjet printing. However, these patterning methods are not suitable for high-resolution patterning on large-size substrates. Patterning based on photolithography would solve this issue. But photolithography is currently

mainly adopted for patterning of silicon semiconductors. When applying it to organic semiconductors using standard photoresists, the photoresist dissolves the organic semiconductor material during processing.

Fujifilm and Imec have developed a new photoresist technology that enables submicron patterning on large substrates without damaging the organic semiconductor materials. The new photoresist technology was developed by fusing the semiconductor processing technology of Fujifilm and Imec, with Fujifilm's synthetic-organic chemistry material design technology. Since existing i-line photolithography equipment can be used, and investment for new equipment is unnecessary, the new technology contributes to a cost-effective production of highresolution organic semiconductor devices.

For technical verification, Fujifilm and Imec developed organic photo detectors (OPD) and organic light-emitting diodes (OLED) using the new photolithography technology, and tested their performance. Organic semiconductor materials were patterned to produce OPD composed of fine light receiving elements down to 200µm×200µm size.

Generally, patterning of organic semiconductor materials degrades the property of converting light into electricity, but the OPD developed in this case were patterned without degradation. With respect to the OLED arrays that were produced using the newlydeveloped photolithography pattering method: 20µm pitch OLEDs emitting uniform light, were realized.

## WHEREVER THE NEXT DESIGN CHALLENGE TAKES YOU, OUR LIGHT CURE TECHNOLOGY IS ALREADY THERE.

The Electronics Market continues to evolve at a faster rate than ever before. Today's complex designs, innovative materials, and increased focus on the environment can present challenges to manufacturers. Whatever demands you face, Dymax has you covered. From conformal coatings to encapsulants to edge bonding materials, we provide solvent-free, light curing technology that's truly game changing. Cost-reducing solutions that turn problems like shadowed areas, cure confirmation, and production throughput into non-issues. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. **Visit dymax.com/electronics**.

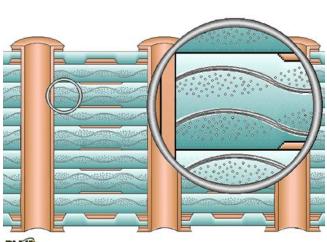

#### LIGHTNING SPEED LAMINATES

## High-Frequency Materials for Lead-Free Soldering

#### by John Coonrod

ROGERS CORPORATION, ADVANCED CIRCUIT MATERIALS DIVISION

Some OEMs' qualification procedures dictate that PCBs be subjected to multiple passes through a lead-free solder reflow cycle. The qualification requirements differ from one OEM to another but some will require 5, 6 or even 10 passes through a lead-free solder reflow process. There are a few different criteria for these tests, however the basic demand is that the PCB must remain mechanically intact and show no signs of delamination. The materials that make up the PCB can have a major impact on the ability of the PCB to survive the lead-free solder evaluations, and some materials perform better than others.

The material properties related to lead-free solder survival are typically coefficient of thermal expansion (CTE), glass transition temperature ( $T_g$ ), decomposition temperature ( $T_d$ ) and moisture absorption.

As a general rule, the material should have a CTE of 70 ppm/°C or less and closer to the CTE of copper, about 17 ppm/°C, which is best. Other general rules suggest a T<sub>g</sub> value higher than 170°C, T<sub>d</sub> greater than 300°C and moisture absorption less than 0.5%.

The high-frequency circuit material industry offers many laminates and prepregs (or bonding material) to choose from. Some of the laminates and bonding materials are robust for leadfree soldering, and others are not. Additionally, there are some bonding materials which are not intended to be used at lead-free soldering temperatures.

A broad classification of bonding materials can be thought of in two categories. Some bonding materials are thermoplastic, while others are thermoset. A thermoplastic bonding material has the attribute of being able to reflow or melt when subjected to certain elevated temperatures. The thermoset materials will not melt or reflow when subjected to elevated temperatures. However, at high temperatures, the

## Where can I find a list of high-speed PCB materials ?

We have compiled a comprehensive list of high-speed materials and the manufacturers who distribute their products in North America.

Check it out today, just click below!

## www.HIGHSPEEDPCBMATERIALS.com

### HIGH-FREQUENCY MATERIALS FOR LEAD-FREE SOLDERING continues

concern can be related to material decomposition.

Each type of thermoplastic bonding material has different characteristics, and one of these is the melt temperature. Some common thermoplastic bonding materials used in

high-frequency PCB fabrication are PTFE, FEP and chloro-fluorocopolymer (Rogers' 3001 material). As for the PTFE bonding materials, some of these are pure PTFE and others are filled PTFE. Depending on the filler, some of these bonding films can have a lower or higher melt temperature than PTFE.

The 3001 bonding material is often used for laminating high-frequency PCBs m when a bonding material with low dissipation factor (Df) and low dielectric constant (Dk) is needed. The Df of this material is 0.003 and the Dk is about 2.3 when tested at 10 GHz per IPC-TM-650 2.5.5.5c (the clamped stripline test). This material is also intended

to be used when subsequent processes are not beyond the melt temperature of the material. During the lamination process, the 3001 bonding film is held under pressure and brought to a temperature of about 450°F (232°C). After the lamination process is complete, the PCB should not be subjected to temperatures above 350°F (176°C); however, this is not the melt temperature of the material.

As thermoplastic materials are heated, their modulus decreases; higher temperature translates into softer material. The 350°F limit for 3001 bonding film is due to the material being very soft at this temperature, and any mechanical stress could cause delamination of the PCB.

When a bonding material with low Dk and low Df is needed and the PCB will be subjected to elevated temperatures after the lamination process, FEP is often used. This material has a Dk of 2.1 and Df of 0.001 when subjected to the clamped stripline test. The melt temperature of

As thermoplastic materials are heated, their modulus decreases; higher temperature translates into softer material. The 350°F limit for 3001 bonding film is due to the material being very soft at this temperature, and any mechanical stress could cause delamination of the PCB.

this material is higher than the 3001 material, so the lamination temperature is higher as well. A lamination temperature of 565°F (296°C) is recommended and PCBs using this material should not be subjected to temperatures above

520°F (271°C) in follow-on processes.

Lead-free soldering temperatures are typically lower than 520°F, so FEP has been used in PCB applications where lead-free soldering is necessary.

The other thermoplastic material suitable for high-frequency PCB bonding is PTFE or filled PTFE. This requires a special fusion lamination process, and few fabricators have this capability. Thermoset bonding materials (prepregs) are generally easier to laminate, and they are more robust for elevated temperature exposures in successive processes. While this is true, some of the thermoset systems have trouble surviving lead-free soldering. This is generally due to the materials' CTE,

$T_g$ ,  $T_d$  or moisture absorption properties. A relatively new bonding material that is thermoset and robust for lead-free soldering is Rogers' 2929 material. With a CTE of 50 ppm/°C,  $T_g$  of 170°C and a  $T_d$  at 400°C, this material has proven to be a good choice for high-frequency multilayer PCBs where lead-free soldering is required.

Fortunately for PCB designers, a variety of available bonding materials can withstand the elevated temperatures often associated with lead-free soldering of high-frequency PCBs. **PCBDESIGN**

John Coonrod is a market development engineer for Rogers Corporation, Advance Circuit Materials Division. To contact Coonrod, click here.

# PCB MANUFACTURING SUCCESS!

## We Have a Better Way to Predict

DFMStream provides powerful DFM capabilities in an easy-to-use tool suite designed to help engineers and designers verify design and manufacturing rules on PCB design databases, Gerber and NC data any time during the PCB design cycle. DFMStream bridges the gap between engineering and fabrication, helps save valuable time and reduces new product introduction bottle necks.

- Provides powerful DFM functionality

- Easy to learn, even for infrequent users

- Easy to implement as part of the everyday design flow

- Saves time and increases productivity

For more information visit downstreamtech.com or call 800-535-3226

#### Netlist errors are quickly validated in DFMStream

Define DFM checks by area so components such as BGAs can be verified with unique rules different from rest of design

### reature

## **Design for Assembly: Components**

## by Tom Hausherr

PCB LIBRARIES

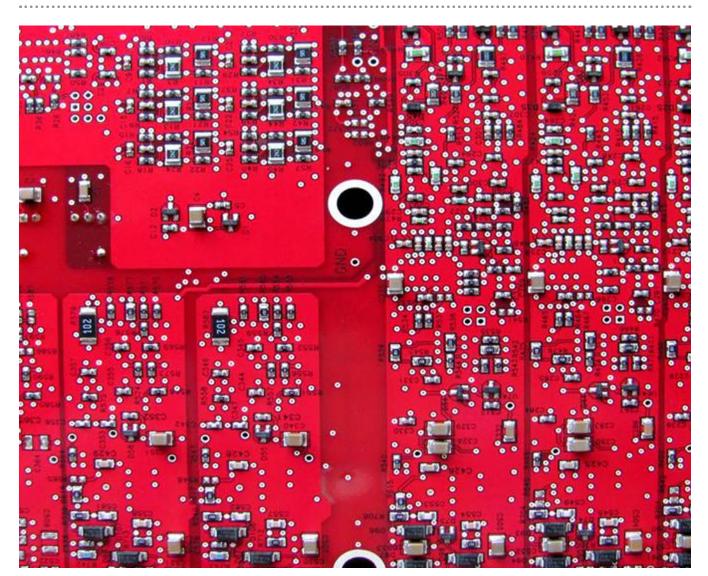

Every PCB layout must go through the component assembly process, and a PCB designer can do several things to make the assembly process easier.

### IPC Classes 1, 2 & 3 for Defect Reject/Accept Criteria

A PCB designer needs to design every layout to meet one of the IPC product classes so that the manufacturer knows the category classification of the end electronic product being designed. A PCB designer can find these three product classes in most IPC standard publications:

## **CLASS 1: General Electronic Products**

Includes products suitable for applications where the major requirement is function of the completed assembly.

### **CLASS 2: Dedicated Service Electronic Products**

Includes products where continued performance and extended life are required, and for which uninterrupted service is desired but not critical. Typically the end-use environment would not cause failures.

## CLASS 3: High-Performance/Harsh Environment Electronic Products

Includes products where continued highperformance or performance-on-demand is critical, equipment downtime cannot be tolerated, end-use environment may be uncommonly harsh, and the equipment must function when required, such as medical life support, military battlefield or other critical systems.

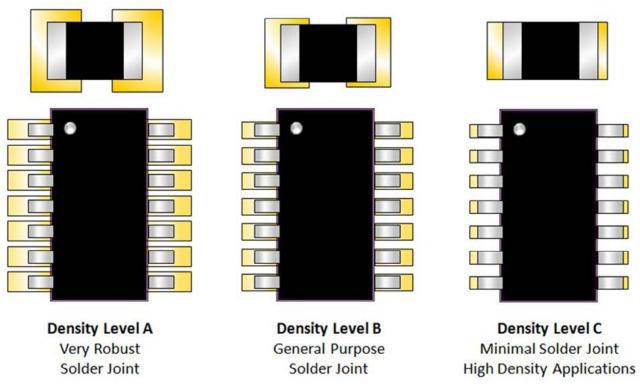

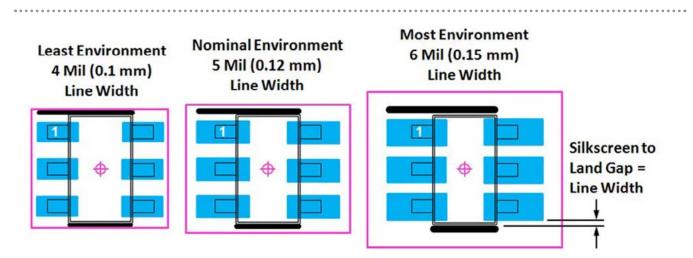

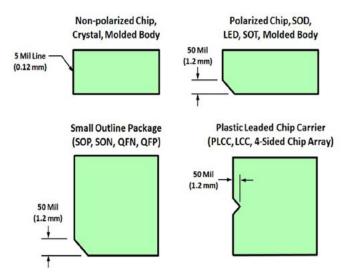

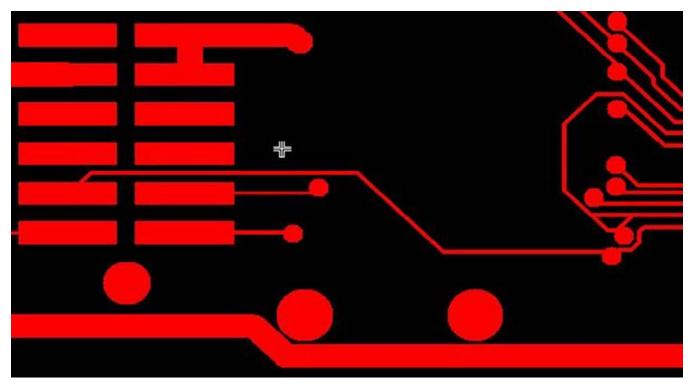

The IPC-7351B land pattern standard uses a three-tier PCB library system for various electronic device applications. These include most, nominal and least dimensional criteria. Figure 1 shows the three-tier footprint density levels.

These three tiers are not directly related to the three IPC classes, but picking the most appropriate land pattern might help the manufacturer achieve a higher yield for a specific IPC product class. It is widely assumed that designs that need to meet IPC Class 3 must use a "Most – Level A" land pattern. This is not true. Any of the IPC-7351B three-tier environments can be

## The Absolute Best Value in High Technology Printed Circuit Boards

Since 1971, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving **total customer satisfaction** on each and every job. It's just the way we do business!

001101\_01001

0100101001010101010100001010101010

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for more reasons why you should use eagle!

## www.eagle-elec.com

### reature

## **DESIGN FOR ASSEMBLY: COMPONENTS** continues

Figure 1: IPC-7351B uses this three-tier footprint density level system.

used to build a Class 3 board assembly. It's just that a Density Level A (Most Environment) land pattern will make it easier for manufacturing to achieve a higher yield. However, an IPC-7351B Nominal Environment land pattern can be used to create a Class 3 electronic product. And the Least environment might also be used to create a Class 3 product but the manufacturing price will go up as the yield goes down.

## **Useful Silkscreen Outlines**

Silkscreen outlines add cost to PCB fabrication and in most cases they are not necessary.

However, if you use silkscreen outlines, here are my guidelines for creating PCB library parts.

1. Silkscreen outlines should never be located under the component because they are covered up during assembly and do not provide any useful function to the assembly process

2. Follow J-STD-001E Assembly Requirements Section 9.2: Silkscreen polarity marking, reference designators, revision level and serial numbers shall be visible after assembly, as shown in Figure 2 3. Silkscreen outlines should be mapped to the maximum component body outline

4. Your company's pad-to-silkscreen drafting rule should override maximum component body mapping

5. Silkscreen outlines are used for assembly placement registration accuracy and post assembly inspection

6. The silkscreen line width and pad to line gap are normally the same value

7. Silkscreen outlines should always be located inside the placement courtyard, otherwise the silkscreen outlines can get confused with other components or overlap with other silkscreen outlines

8. Only one line width should be used throughout the entire PCB library

## Silkscreen-to-Pad Clearance

The yet-to-be-released IPC-7351C will introduce guidelines for three-tier silkscreen lines' widths as shown in Figure 3. Some PCB designers allow silkscreen on pads and they expect the fabrication shop to trim the silkscreen away

### **DESIGN FOR ASSEMBLY: COMPONENTS** continues

Figure 2: Silkscreen polarity marking, reference designators, revision level and serial numbers should be visible after assembly.

from the pad. But what if the fabrication shop doesn't do that? Silkscreen ink on a solder pad becomes a solderability issue. The assembly shop will be scrapping the silkscreen ink off the pads prior to applying the solder paste via stencil if fabrication shop does not. But assembly will be dealing with soldering issues from the pad contamination!

Figure 4: Recommendation for silkscreen polarity.

### **Polarity Markings or Not?**

Components that can be inverted (like resistors) during assembly do have polarity marking. All parts that have to be inserted in a particular rotation require a silkscreen marker to indicate polarity or Pin 1. My recommendation for silkscreen polarity is to extend the silkscreen line the full length of the Pin 1 pad as shown in Figure 4.

For bottom-termination components, the placement courtyard hugs the package body or the pads. In this case, the absence of silkscreen is the best polarity marker as shown in Figure 5 for a QFN package.

#### **Assembly Outlines and Polarity Marking**

The assembly drawing component outlines should be a simple closed polygon and the po-

Figure 3: Three-tier silkscreen lines widths will be covered in the upcoming IPC-7351C guidelines.

#### reature

## **DESIGN FOR ASSEMBLY: COMPONENTS** continues

Figure 5: The best polarity marker.

Figure 6: A good way to locate Pin 1.

Figure 7: Courtyard excess.

larity marker should be a simple chamfer to locate Pin 1 as shown in Figure 6.

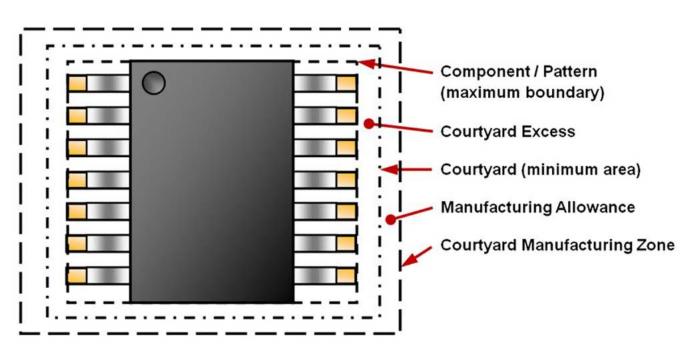

## **Courtyard Excess**

Courtyard excess as shown in Figure 7 is used as a guideline for part placement. Every assembly shop has its own unique tolerances, and if the guidelines place the components too close together, the assembly shop has a manufacturing allowance: the necessary gap between courtyards.

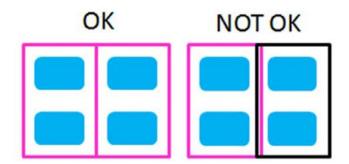

If the assembly shop does not require a manufacturing allowance, the PCB designer can place the courtyards so that they touch, but

# We have been Mil-Spec certified for over 30 years.

Dragon Circuits (DCI) was the first PCB manufacturer in Texas to acquire Mil-PRF-55110 certification. In addition to aerospace, defense and military, we bring an ongoing commitment to quality and reliability to all the markets we serve, including medical, industrial, telecom, computing, R&D and semiconductor.

**VIEW CERTIFICATIONS**

**START A QUOTE**

**Legendary manufacturing, service and engineering.** www.dragoncircuits.com | info@dragoncircuits.com | 972.790.7610

### **DESIGN FOR ASSEMBLY: COMPONENTS** continues

Figure 8: Courtyards should touch, but not overlap.

not overlap as shown in Figure 8. Crowding and overlapping courtyards can lead to solder bridging during assembly.

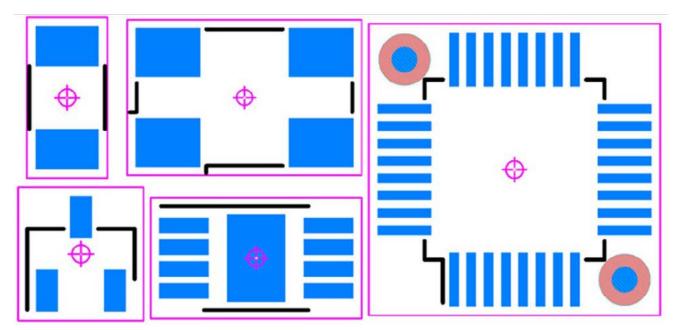

#### **Part Placement and Alignment**

In the 1980s, assembly shops preferred all polarized parts should be pointed in the same direction. With today's technology, that is no longer necessary; however, aligning parts in neat rows will add aesthetic value to the final PCB. And if you're selling boards on the open market, consumers will naturally choose the prettiest board. Also, nicely ordered parts are better for signal routing and use of space.

#### **Footprint Origins**

Components come packaged in tape and reel, tubes and trays. The pick-and-place machines pick up the component at the center of gravity. When PCB designers put the origin of the PCB library part in the center, they are aiding the assembly shop. However, some component packages have irregular shapes and the center is difficult to determine. And for PCB design layout routing, through-hole connector pins might need to fall on a grid pattern and making Pin 1 the origin optimizes signal routing. A centric origin marker helps the PCB designer identify the location of the footprint origin. However, some CAD tools auto-generate an origin marker in the software and in that case there is no need to add an additional origin marker in the PCB library part.

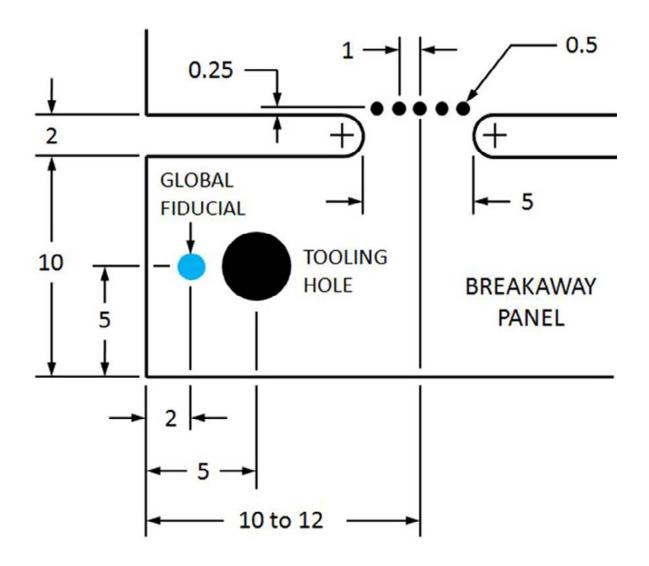

### **Assembly Rails or Frames**

The assembly shop needs the board edge to clamp onto while the board travels through the pick -and-place machines and the solder reflow oven. If the PCB designer places components close to the board edge due to high density part placement, then a breakaway panel must be added to aid the assembly line. The breakaway tab could also contain the

Figure 9: Centric origin markers may be auto-generated by EDA tools or added by the designer.

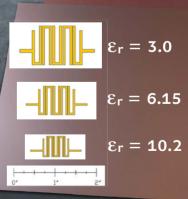

## smaller IS BFT TFR Design with ROGERS materials for smaller antennas

obile

ALS A

## The Leader in HIGH Dielectric Constant Circuit Materials

In today's mobile and connected world, designers must compact increased functionality into smaller spaces. Smaller circuits are possible with highdielectric constant (high- $\varepsilon_r$ ) printed-circuit-board (PCB) materials. Rogers offers the widest variety of high- $\varepsilon_r$  PCB materials for high frequency circuit designs that simply must be made smaller.

Look to Rogers Corporation not only for PCB materials with high- $\varepsilon_r$  values, but for circuit materials with the widest range of  $\mathcal{E}_r$  values in the industry. Rogers' PCB materials provide circuit designers with true flexibility, not just for the electrical performance they seek, but to achieve it in the smallest-sized circuits possible.

| Product   | ٤r   | Df @ 2.5GHz |

|-----------|------|-------------|

| RO4360G2™ | 6.15 | 0.0030      |

| RO3006™   | 6.15 | 0.0018      |

| RO3010™   | 10.2 | 0.0020      |

If it's a circuit that has to be smaller. make sure it is also better, with Rogers!

ews

wifi

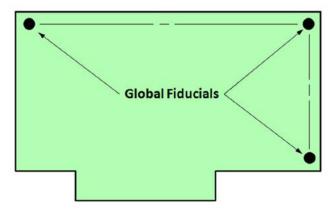

Figure 10: Breakaway tab with global fiducials and tooling holes.

global fiducials and tooling holes as shown in Figure 10.

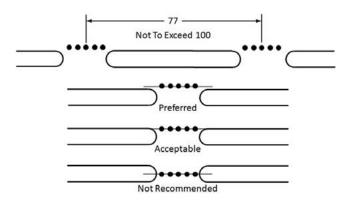

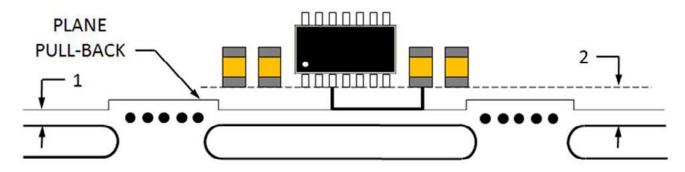

When the board is completely assembled the breakaway tabs must be removed. There are two methods of separating the breakaway tabs. The first and most popular method is the use of routing and mouse bites as shown in Figure 11. The trace routing must be at least 1 mm away from the finished board edge and the mouse bites. And components should be located at least 2 mm away from the routed edge and mouse bite holes as shown in Figure 12.

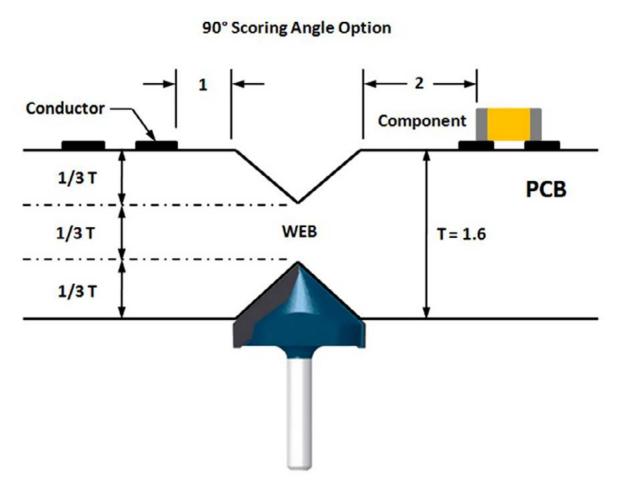

The other process of separating the breakaway panel is V-scoring, as shown in Figure 13.

Figure 11: Not recommended: routing and mouse bites.

Figure 12: Components are at least 2 mm away from routed edge and mouse bite holes.

Figure 13: V-scoring is an alternative method for separating breakaway panels.

Some PCB designers like to ensure that the breakaway tabs are secure and won't breakaway during handling. In this case, the PCB designer will add a frame around the entire PCB design and use mouse bites and routing channels. Add-

ing a frame reduces the number of boards you can get on a panel but it does add rigidity to the individual board to ensure the breakaway tabs do not prematurely break away during assembly handling.

### **DESIGN FOR ASSEMBLY: COMPONENTS** continues

Figure 14: Global fiducials register the board for placement accuracy.

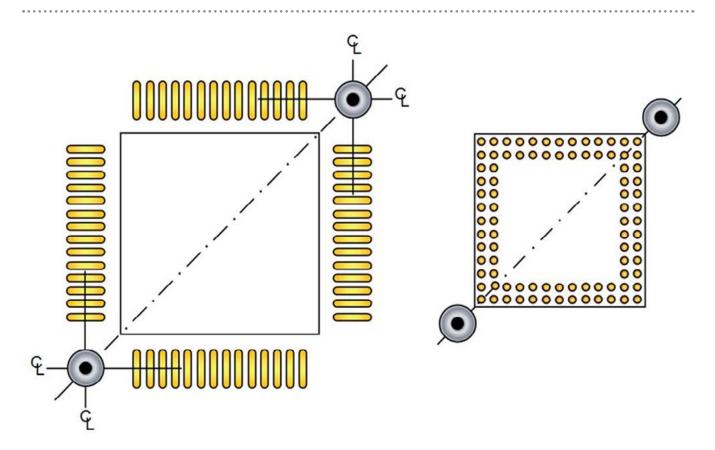

## **Global and Local Fiducials**

Global fiducials are a must for the pick-andplace machine to optically bombsite the fiducial locations and register the board for machine placement accuracy as shown in Figure 14. Local fiducials are used for fine-pitch QFP components when the pin pitch is less than 0.625 mm and BGA components when the pin pitch is less than 0.8 mm as shown in Figure 15. With today's modern equipment, many assembly shops do not require local fiducials; however, they might come in handy for repair/ replacement. **PCBDESIGN**

*Part 2 of this article will continue in the November issue of The PCB Design Magazine.*

Tom Hausherr CID+, CIT, is founder and CEO of PCB Libraries Inc. To contact him or read his past columns at PCBDesign007, <u>click here</u>.

Figure 15: Local fiductials are not always required. But they may come in handy for repair work.

**Advanced PCB Solutions**

## OUR TECHNOLOGY GIVES DESIGNERS EVERY POSSIBLE ADVANTAGE

Landless Via is an exciting new technology that allows Design Engineers to resolve space restrictions by eliminating via pad requirements. Our plating methods eliminate the need for an annular ring to facilitate proper plating in the hole and on the surface, giving our customers a design advantage.

CLICK TO LEARN MORE

Candor Industries, Inc.

WE DON'T JUST SAY I

...WE CAN PROVE IT!

www.candorind.com

416 736 6306

#### BEYOND DESIGN

## **Impedance Matching: Terminations**

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD | AUSTRALIA

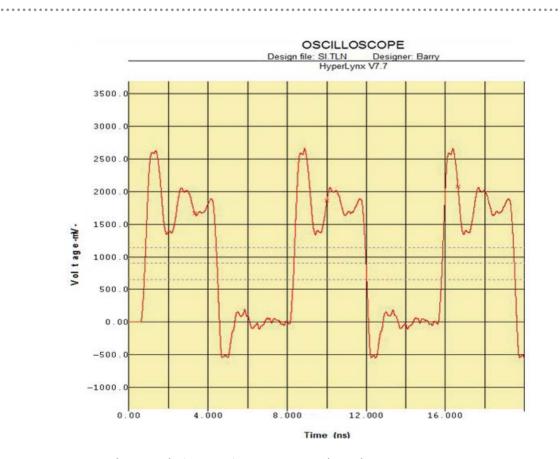

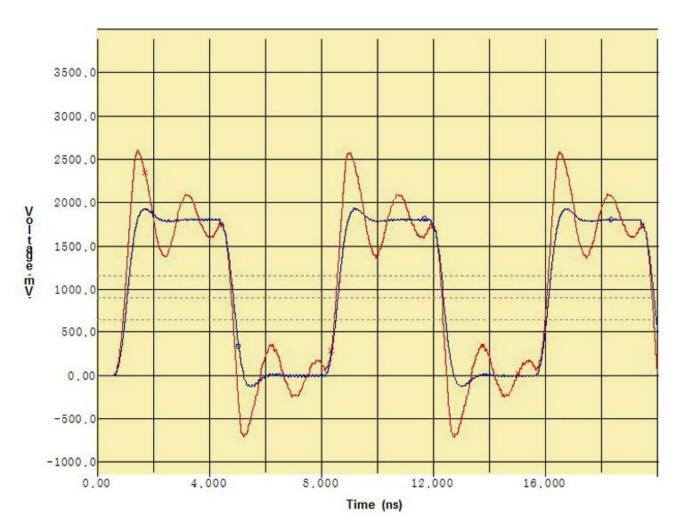

The impedance of the trace is extremely important, as any mismatch along the transmission path will result in a reduction in signal quality and possibly the radiation of noise. Mismatched impedance causes signals to reflect back and forth along the lines, which causes ringing at the load (Figure 1). The ringing reduces the dynamic range of the receiver, eats into the noise budget and can cause false triggering.

Reflections occur whenever the impedance of the transmission line changes along its length. This can be caused by unmatched drivers/loads, layer transitions, different dielectric materials, stubs, vias, connectors and IC packages. By understanding the causes of these reflections and eliminating the source of the mismatch, a design can be engineered with reliable performance. For perfect transfer of energy and to eliminate reflections, the impedance of the source must equal the impedance of the trace, as well as the impedance of the load. When the signal path has an impedance discontinuity, place a terminator at the point of line discontinuity to equalize the impedance.

Everyone would agree that the signal at the load in Figure 1 is not pretty and obviously has an impedance mismatch that needs to be addressed. But when should a transmission line be terminated and how?

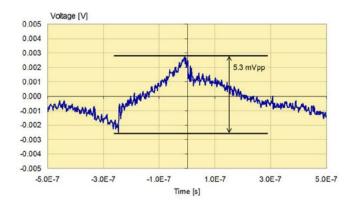

Figure 1: Unterminated 1.5 inch (38 mm) transmission line shown in HyperLynx.

Ventec Europe ventec-europe.com Ventec-USA ventec-usa.com Ventec International Group venteclaminates.com

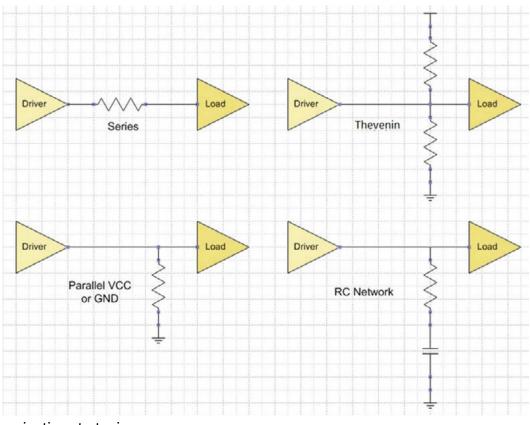

Figure 2: Termination strategies.

As signal rise times increase, consideration should be given to the propagation time and reflections of a routed trace. If the propagation time and reflection from source to load are longer than the edge transition time, an *electrically long trace* will exist. If the transmission line is short, reflections still occur but will be overwhelmed by the rising or falling edge and may not pose a problem. But even if the trace is short, termination may still be required if the load is capacitive or highly inductive to prevent ringing. Generally when the trace length exceeds one sixth of the electrical length of the rising edge rate, then termination is required.

For a driver signal with a 1 ns rise time, since the speed of a signal in FR-4 is approximately 6in/ns (150 mm/ns) then an unterminated trace can only be  $6 \ge 1.0$  inches (25 mm).

This brings us to the rule of thumb: All drivers whose trace length (in inches) is equal to or greater than the rise time (in nanoseconds) must have provision for termination. The easiest way to terminate is to use a resistive element. Termi-

nation can be made at the source or at the load.

Different terminating methods have advantages and disadvantages for different applications but in general:

1. Series is excellent for point to point routes, one load per net. It works well for traces that are electrically short and is used to fanout multiple loads radially from a common source—star routed—without affecting other circuits in the network. Series termination reduces ringing and ground bounce. Series is the most used termination for high speed design.

2. Parallel is preferred for busses.

3. Thevenin is commonly used for driving logic busses also.

4. RC networks provide good signal quality but are not good for high frequencies or long trace lengths.

5. Diode networks are used to limit overshoot but do not affect trace impedance or reduce reflections and the clamping diodes are generally on the IC inputs.

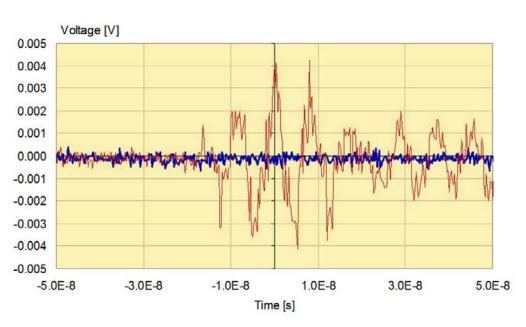

Figure 3: Impedance backmatching.

### **How Backmatching Works**

For a point to point topology, the most common method of impedance termination is to use a series resistor close to the driver. The sum of the series resistor and the source impedance should equal the transmission line impedance.

Impedance backmatching slows down the rise and fall times and reduces the ringing (overand undershoot) of clock drivers. A half voltage pulse is launched from the source due to the voltage divider network formed by the source impedance, series terminator and the transmission line. As this half voltage pulse reaches the load, it is instantaneously reflected back along the trace. This reflected pulse adds to the initial pulse to form a full voltage square wave—so we get the signal we want at the load.

The reflected pulse travels back to the source. When it reaches the series terminator it sees the series resistor (24  $\Omega$ ) plus the source impedance

| File        | Edit  | Exp   | ort   | Import Se        | tup Help      |                                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |       |                |                   |                                  |                                      |

|-------------|-------|-------|-------|------------------|---------------|----------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|----------------|-------------------|----------------------------------|--------------------------------------|

| 121         | 8     | 30    | 19    | C 🖸 ⊀            | B B II        | 🛛 🔺 🕅 🗢 💡 🛅                            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |       |                |                   |                                  |                                      |

| ackup       | Plann | er Pl | N PL  | anner            |               |                                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |       |                |                   |                                  |                                      |

| 1           | 1.41  |       |       | er 8 Layer 1     | 01 mmr   12   | Layer 14 Layer 16 Layer 18 Layer 8 Lay | ar materiale         | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |       |                |                   |                                  |                                      |

|             | -     | a) er | o Lay | er   o Layer   1 | u cayer   12  | ICD STACKUP PLANNER FX                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0/10                | /2013 |                |                   | -                                | Barrist Third Street C               |

| UNITS:      | : mil |       |       |                  |               |                                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9/10                | /2015 |                |                   | Iotal                            | Board Thickness: 6                   |

|             |       |       |       |                  |               | Differential Pairs > 50/100            | in the second second | and the second s |                     | -     | -              |                   | -                                |                                      |

| ayer<br>No. |       | Diam  |       | Description      | Layer<br>Name | Material Type                          |                      | Dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Copper<br>Thickness | Trace | Trace<br>Width | Current<br>(Amps) | Characteristic<br>Impedance (Zo) | Edge Coupled<br>Differential (Zdiff) |

|             |       |       |       |                  |               |                                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |       |                |                   |                                  |                                      |

|             |       |       |       | Soldermask       |               | Dielectric                             | 3.3                  | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |       |                |                   |                                  |                                      |

| 1           | 8     | 4     | 8     | Signal           | Тор           | Conductive                             |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.7                 | 12    | 5              | 0.22              | 50.13                            | 97.4                                 |

|             |       |       |       | Prepreg          | 10000         | 370HR : 1080 : Rc= 64% (2GHz)          | 3.89                 | 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                 |       |                |                   |                                  |                                      |