# PCB BOOM A GAZINE

l·Connect007

## **REABLING** It all comes down to the landing.

## OUR LIBRARY IS ALWAYS OPEN

Registered members of my I-Connect007 have 24/7 access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to Complex PCBs.

Enrich your mind and expand your knowledge! Download these popular titles with just a click.

They're pretty awesome!

## Your how-to guide for making Rev 1 work.

In this book, readers will learn how to design complex boards correctly the first time, on time. A must-read for anyone designing high-speed, sophisticated printed circuit boards. THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

#### **Executing Complex PCBs**

Scott Miller Freedom CAD Services

1.007 Books

DOWNLOAD NOW

I-007ebooks.com/ecd

#### JULY 2019 • FEATURED CONTENT

## PCB007 MAGAZINE

## Reliability

Our industry is embarking on a new age of technical development to achieve the reliability now required of the devices we fabricate. Reliability will be crucial to both our success and safety. We look at the latest developments in reliability improvement for PCB fabrication.

28

10

Microvias: Links of Faith Are Not Created Equally by Jerry Magera and J.R. Strickland

28 Interconnect Reliability Correlation With System Design and Transportation Stress by Dr. Paul Wang, etal.

38 How Changing Cleaning Technologies Affect Reliability Interview with Michael Konrad

- 46 A Guide to High-reliability PCBs From Design to Specification by Jeff Beauchamp

- 58 Avoiding CAF Failures at the IPC High-reliability Forum Interview with Terry Munson

- 72 How to Feed Test Data Back to Engineering for Process Improvement by Todd Kolmodin

- 84 Focusing on Surface Sensitivity for Reliability Interview with Elizabeth Kidd and Alex Bien

#### FEATURE COLUMNS:

68 When You Do Everything Right and Something Still Goes Wrong by Tara Dunn

78 Avoid Failures in PCB Production With Compliance Control by Didrik Bech Leverage technology for competitive advantage: it's what leaders do.

CapStone<sup>™</sup> is the culmination of ESI's decades of laser-material interaction expertise and technology leadership in flex PCB processing.

Double your throughput and dramatically decrease your per-panel processing costs.

Adopt CapStone's new technology early... and stay ahead.

## CapStone

##

ESI is now part of MKS. On February 1, 2019, ESI became part of MKS Instruments, Inc. The combination will leverage the respective companies' strengths and expertise to provide rich and robust solutions that meet the challenges of our customers' evolving technology needs.

For more information about CapStone, visit us at www.esi.com

#### JULY 2019 • ADDITIONAL CONTENT

#### SHORTS:

26 A Tribute to Greg Beck

- 41 Building a Brain

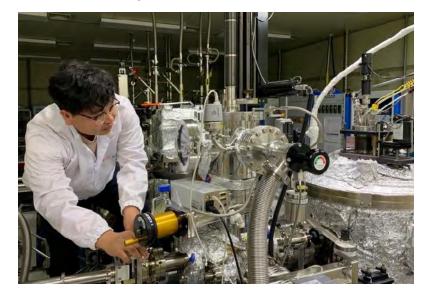

- 45 Establishing the Ultimate Limits of Quantum Communication Networks

- 65 New Interaction Between Thin-film Magnets for Faster Memory Devices

- **70** Widening the Net

- 94 Denny Fritz: The Difference Between Quality and Reliability

#### COLUMNS:

- 8 Reliability...It All Comes Down to the Landing by Nolan Johnson

- 42 What Do You Mean "Passed" Isn't Enough? by Todd Kolmodin

- 52 Moving Into Microvias, Part 4 by Michael Carano

- 62 A Conversation With Prototron's Van Chiem by Steve Williams

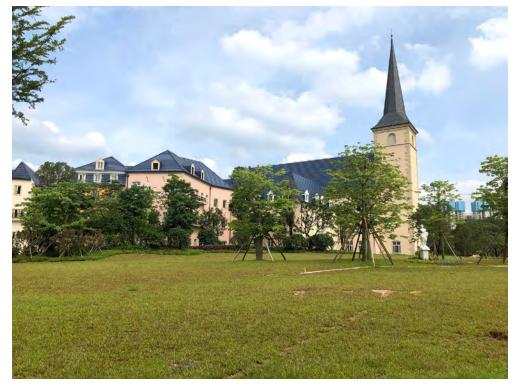

**90 Sunday Afternoon in Dongguan** by Marc Ladle

#### **HIGHLIGHTS**:

- 56 EINO07 Industry News

- 66 MilAero007

- 82 PCB007 Suppliers

- **96** Top 10 from PCB007

#### DEPARTMENTS:

- 99 Career Opportunities

- 108 Events Calendar

- **109** Advertiser Index & Masthead

#### 6 PCB007 MAGAZINE I JULY 2019

## tec-speed 20.0 Dk 3.0-3.48

## No More Compromises Performance, Price & Availability

SUPERIOR loss characteristics

**GREATER** reliability **UNRIVALED** high frequency performance

Visit www.ventecsolutions.com/tec-speed-20

ventec-speed

## **Reliability...** It All Comes Down to the Landing

#### Nolan's Notes by Nolan Johnson, I-CONNECTOO7

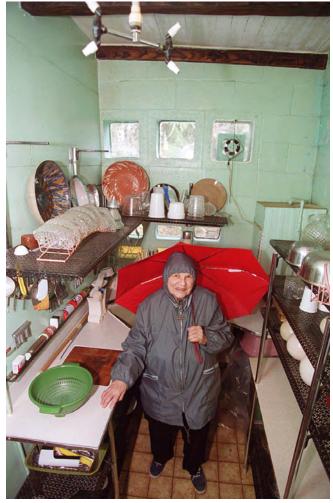

My grandmother, Frances, was something. Some thought she was brilliant, and others were convinced she was full-blown crazy. She certainly was creative, though; nobody could argue that point. She spent almost 50 years designing and building a prototype self-cleaning house. She did not have an engineering degree; she was entirely self-taught. Over the years, she worked out all sorts of mechanical solutions and developed water-repellent materials and fabrics of her own formulation so that

Grandma Frances in her self-cleaning kitchen in 2002.

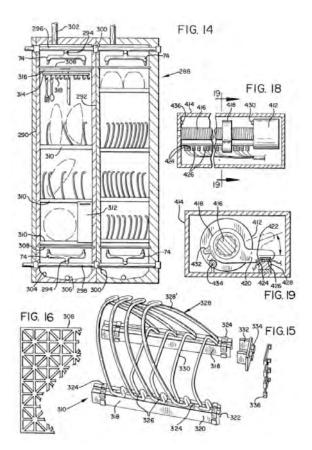

Detail of self-cleaning cupboard, a patented design held by Frances Gabe.

her home could simply shower itself clean. She lived in that prototype for 40+ years.

However, I have to say that when one detail started to go wrong, everything cascaded out of control very quickly. At one point, Frances made the dish cupboard do double-duty as the dishwasher; just put the dirty dishes back with the clean ones and wash them all, every time. If the cupboard malfunctioned, then a couple of dirty dishes would end up making a mess of everything. Later on, she just kept the dishes on a rack on the wall. To wash the dishes, you had to spray down the whole kitchen. Needless to say, most of the time, the house was like a rainforest. While some of her implementations may have been a bit impractical overall, her self-cleaning house was a reliable solution to her housecleaning problem in that it worked and she didn't have to.

And that's our theme for this issue—reliability in the products that we turn out for use in the world. Of course, to talk about reliability, we also have to talk about the failures we're trying to avoid. Grandma Frances had a pacemaker that served her well for many years, triggering a heartbeat something like 800 million times while keeping her alive and creative—longer.

A demonstration of a very different level of reliability is illustrated on this month's cover. Falcon Heavy's reusable side boosters are shown landing in unison at Cape Canaveral Landing Zones 1 and 2 following a SpaceX test flight in February 2018.

Our industry is embarking on a new age of technical development to achieve much higher levels of overall reliability that will be required of the devices we fabricate. Medical devices will be relied upon to keep us living in many more situations. Autonomous vehicles will need to be failure-free to keep riders and pedestrians alike safe in the world. IoT will bring opportunities to put smart electronics in new places, performing in unthought-of ways. Reliability will be crucial to both our success and safety.

Right now, it's hard to avoid the conversation. Recently, IPC hosted the IPC High-Reliability Forum and Microvia Summit in Baltimore, Maryland—two full days of discussion on how to increase reliability. I-Connect007 sent Design007 Managing Editor Andy Shaughnessy to cover the event.

"The conference in Baltimore was solid with attendance up from last year," said Shaughnessy. "The big topic at the conference was mil/aero microvia failure and the investigations by Motorola and other members of the IPC V-TSL-MVIA subcommittee. By the way, that committee would love to have more input from the industry if you're able to share your company's data on microvia failures." Thus, we look to those conversations for this issue. We start with Jerry Magera and J.R. Strickland who set the tone with their technical article titled "Microvias: Links of Faith Are Not Created Equally." Right on their heels is research from Paul Wang, et al., into "Interconnect Reliability With System Design and Transportation Stress." Completing the technical hat trick, Mike Konrad discusses "How Changing Cleaning Technologies Affect Reliability" with Andy Shaughnessy.

Columnist Todd Kolmodin changes up the pace with his column, "What Do You Mean 'Passed' Isn't Enough?" NCAB's Jeff Beauchamp brings us "A Guide to High-reliability PCBs From Design to Specification," and Mike Carano's column moves into part four on "Moving Into Microvias."

In another interview, Andy Shaughnessy talks with Terry Munson about avoiding CAF failures. And columnist Steve Williams files an interview with Prototron's Van Chiem on the topic of reliability. Tara Dunn continues the theme with "When You Do Everything Right and Something Still Goes Wrong."

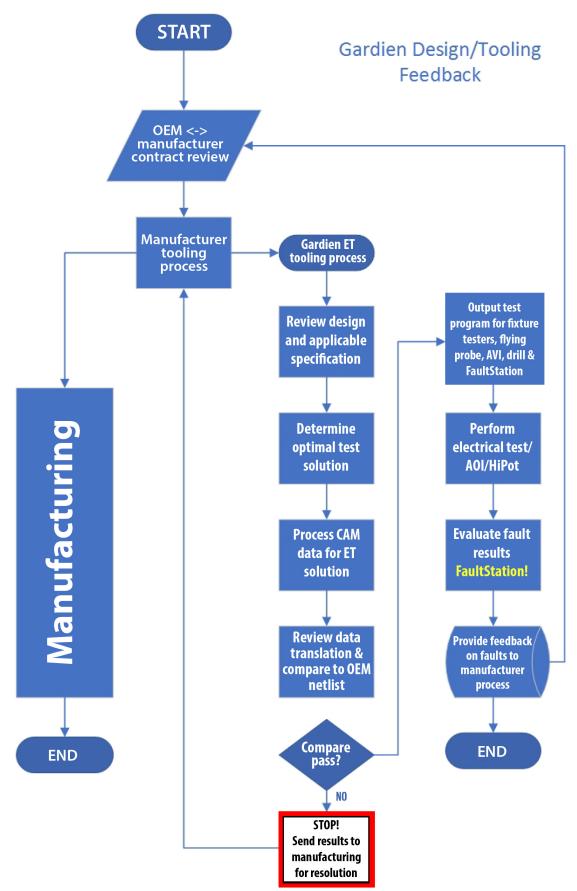

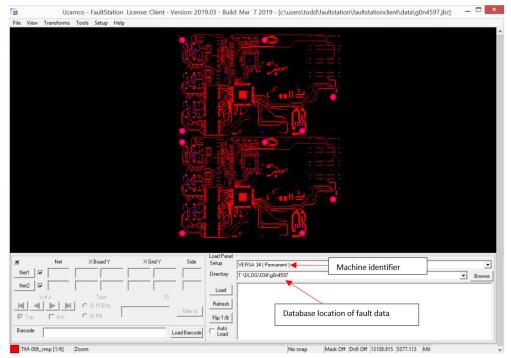

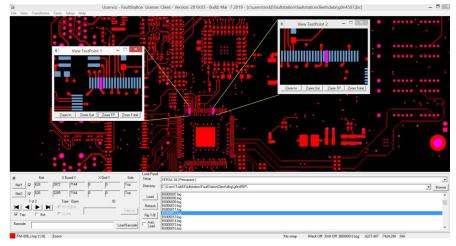

Gardien's Todd Kolmodin (in addition to his column in this month's issue) goes deeper into the feedback loop between post-fab test and ongoing design optimization in his article, "How to Feed Test Data Back to Engineering for Process Improvement." And Didrik Bech discusses how to "Avoid Failures in PCB Production with Compliance Control." Finally, Marc Ladle holds onto his column's anchor position with a visit to and a discussion of Huawei's influence on the community of Dongguan, China.

My grandmother's self-cleaning house may have been reliable for her, but it was never ready to take over the world. However, the products we build for our customers (SpaceX included) will. So, dive into this issue with us and we'll all stick the landing. **PCB007**

**Nolan Johnson** is managing editor of *PCB007 Magazine*. Nolan brings 30 years of career experience focused almost entirely on electronics design and manufacturing.To contact Johnson, click here.

#### **Microvias: Links of Faith Are Not Created Equally**

#### Feature by Jerry Magera and J.R. Strickland MOTOROLA SOLUTIONS INC.

#### Abstract

Microvias connect adjacent copper layers to complete electrical paths. Copper-filled microvias can be stacked to form connections beyond adjacent copper layers. Staggered microvias stitch adjacent copper layers with paths that meander on the layers between the microvias. Both microvia configurations are formed by essentially the same sequential operations of laser drill, metallization, and patterning, using various chemical, mechanical, and thermal treatments to form each laver, one over the other. Stacked microvias must be filled while staggered microvias do not. Process specifics differ from manufacturer to manufacturer. Stacked microvias fracture during reflow assembly while staggered microvias do not. Assembly reflow subjects the printed wiring board (PWB) to the greatest temperature excursion. Stacked microvias with a weak interface fracture during assembly reflow and are a hidden reliability threat. This phenomenon

was reported in IPC-WP-023 <sup>[1]</sup> in May of 2018. IPC-TM-650 Method 2.6.27A is a performancebased PWB acceptance test that detects fractured microvias. SEM pictures are presented to initiate discussions in the search for the root cause. Included are cross-section images of completed microvia structures, SEMs after laser drill, and after electroless copper. Not all stacked microvias fail. To learn why, microvia samples were collected from different PWB suppliers. Microvias drilled by UV lasers are compared to microvias drilled by other laser configurations. The images show that microvia structure was influenced by laser type. This article discusses the various laser-drilled microvias and presents SEM photographs to begin the search for the root cause of weak copper interface.

#### Introduction

The search for root cause in this article focuses on laser drill. Not all stacked microvias fail. To learn why, microvia samples drilled by UV lasers were visually compared to microvias drilled by other laser configurations. Samples

## Unrivaled Test Speed with Full Automation

Introducing the newly designed atg A8a with 8 test probes and a new high speed "lights out" automation for unrivaled throughput.

atg

0

3 1

#### Highlights:

- Small footprint (6 square meters)

- Dual shuttle pick & place automation

- High accuracy combined with high test speed

- Pen or label marking option

#### Watch video

Get more info

atg Luther & Maelzer GmbH Zum Schlag 3 • 97877 Wertheim • Germany Phone + 49-9342-291-0 • Fax + 49-9342-395 10 klaus.koziol@cohu.com • www.atg-lm.com

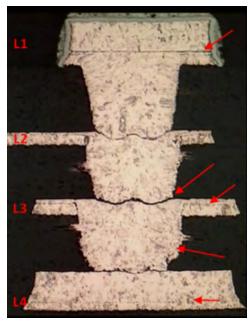

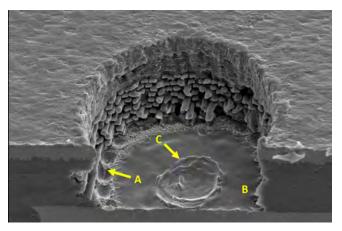

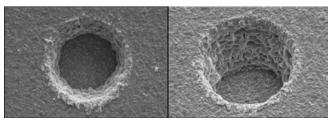

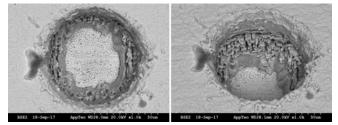

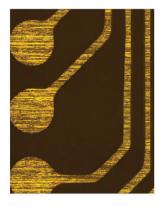

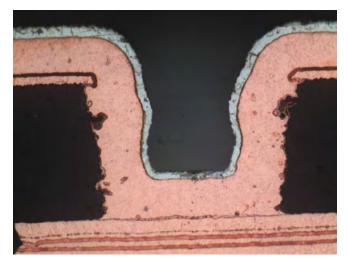

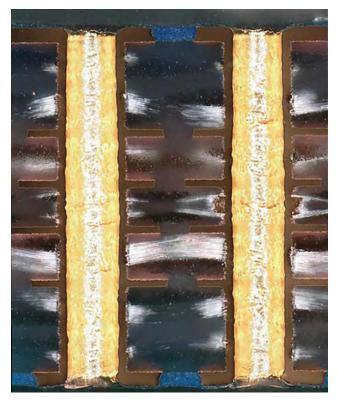

Figure 1: Cross-section of layer 1 to layer 3 staggered copper filled microvia and layer 1 to layer 4 stacked copper filled microvia. Cross-sections were polished and microetched to reveal copper structure.

were extracted after laser drill and after electroless copper. SEM analysis provided highresolution views for comparison. The SEM pictures revealed that microvia structure was influenced by laser type.

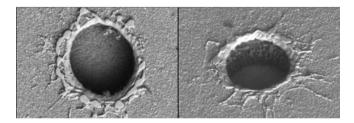

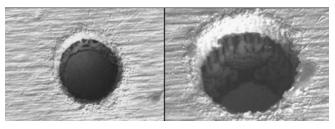

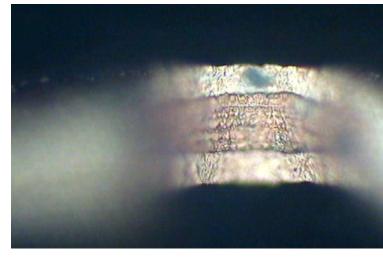

Figure 1 shows a two-level staggered microvia and a three-level stacked microvia. Both configurations are used in PWBs; however, when both were used on same PWB, the stacked microvia failed during reflow assembly while the staggered microvia did not. The microvias were formed with a UV-CO<sub>2</sub> combo laser UV clean followed by desmear, electroless copper, and electrolytic copper fill.

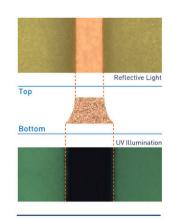

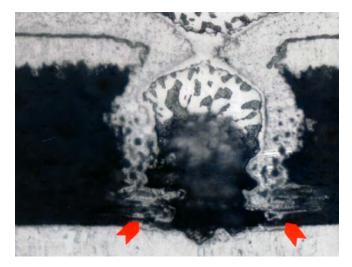

Both stacked and staggered microvias must survive reflow assembly. A cross-section of a failed three-stack microvia shown in Figure 2 revealed a separation between the target pad and plated copper fill at both layers 2 and 4. The microvias were drilled with a UV laser followed by desmear, electroless copper, a copper strike, then copper fill. The UV laser ablation parameter was set to dig into the copper target

Figure 2: Cross-section of a three-stack microvia failure.

pad. The UV-drilled microvia failed during reflow assembly.

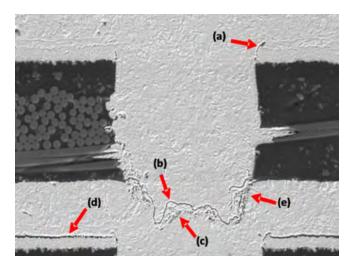

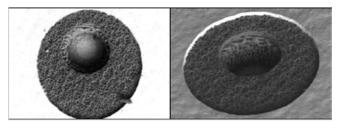

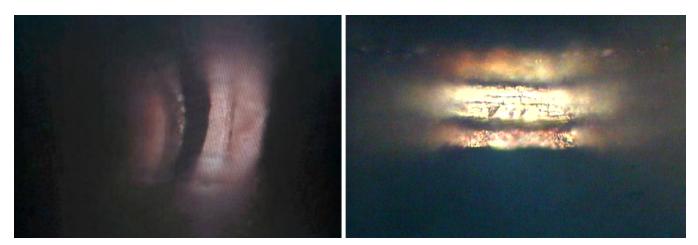

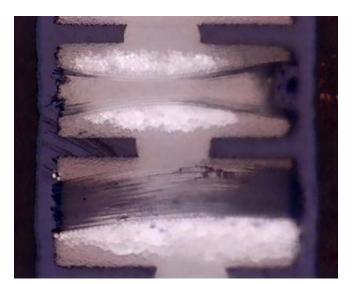

Figure 3 is SEM photograph of a UV laserdrilled, copper-filled microvia cross-section before assembly reflow. The copper-fill to target pad interface as shown is a complex structure that meanders into the layer 2 plated copper. Arrow (a) points to a UV laser-formed copper burr at the knee of the copper foil. Arrow (b) points to a thin demarcation that follows the copper fill to copper strike interface. Arrow (d) points to the electroless layer between the copper foil and electroplated copper. Arrows (c) and (e) point to interface features that are darker and coarser than the plated copper. The electroplated copper strike to electroless copper to target pad interfaces were obscured by the features created by the UV laser ablation.

UV laser-drilled stacked microvias failed reflow assembly more frequently compared to microvias drilled by other laser types. The difference was related to the UV laser created features present between the copper fill and target pad as shown in Figure 3. The features, only observed in UV laser-drilled microvias formed as copper melted and recast in the presence of air, coincide with the weak points that fracture

Figure 3: UV-only laser-drilled copper-filled microvia: (a) UV-laser-induced burr formed on copper foil; (b) Demarcation between copper fill and copper strike; (c) Feature with different texture compared to the plated copper; (d) Electroless copper layer between copper foil and electroplated copper; (e) Feature with texture different compared to the plated copper.

when thermally stressed during reflow assembly. The rest of this article presents SEM photographs of microvias after laser drill and after electroless copper to show the condition of the copper surface of the target pad produced by the commonly practiced laser processes.

#### **Results and Discussion**

The PWB manufacturing base uses different laser types, plating chemistries, and laminate materials in the manufacture of PWBs with microvias. A reliable stacked microvia depends on the condition of the target pad after the laser process. Laser drilling is the accepted method of forming microvias. UV Nd:YAG and CO<sub>2</sub> lasers were developed to drill microvias and are commercially available in four different configurations to the PWB industry.

#### 1. UV Nd:YAG Laser

The UV laser can micro-machine a variety of materials, including copper and glass-reinforced dielectric laminate to produce unique features. The ability to ablate copper can potentially damage copper surfaces, such as the target pad of a microvia. SEM photographs of target pads touched by the UV beam show evidence of melted copper and copper particles that were explosively ejected from the melted copper surface. Copper flow patterns were visible on the target pad along with porosity and inclusions that were characteristic of the sputtering and recasting of molten copper. Molten copper flow patterns were visible over the surface of the target pad and the rim of the outer layer copper foil surrounding the microvia opening—basically any copper surface the UV beam contacted. Constructions require surface copper thickness thinner than target copper thickness to prevent the UV beam from piercing the target pad copper. In most constructions, UV copper ablation requires entry copper to be less than 0.5-oz. copper weight.

#### 2. UV-CO<sub>2</sub> Laser

Referred to as a combination laser drill machine, it consists of a UV laser and a  $CO_2$  laser. The UV laser first creates a window through the copper foil and slightly bites into the glass-

reinforced dielectric material. After the UV laser opens the copper window, the  $CO_2$  laser then removes the remaining laminate material to expose the target pad. The copper target pad reflects the  $CO_2$  laser beam, and the reflected photons collide with the incident photons at the copper surface. The photon interaction and reflection leaves a very thin resinous skin <sup>[2]</sup> on the copper surface of the target pad that must be removed before the microvia is plated for a reliable connection.

Many manufacturers today add a UV target pad cleaning step to remove the residual film. The intensity of the UV laser cleaning step may adversely modify the target pad copper surface. It was observed that melted and recast copper features were produced around the rim and edge of the copper foil at the outer layer of the microvia, but this damage did not produce reflow-induced failures. The entry copper thickness is typically less than 0.5-oz. copper.

#### 3. CO<sub>2</sub> with Chemically Etched Copper Window

A low-power CO<sub>2</sub> laser beam cannot ablate through reflective copper but can ablate glass-reinforced dielectric material. An opening must first be created in the copper foil to allow the CO<sub>2</sub> laser beam to drill a microvia. The window is created by imaging and etching the copper foil. The diameter of the copper window may be either less than or greater than the CO<sub>2</sub> beam diameter. The process practiced depends on the ability to register the CO<sub>2</sub> beam within the copper window and target pad, taking into account cumulative registration tolerance for material stretch and shrink. The CO2 beam reflects off the target pad and leaves the characteristic resinous film that must be removed. Since copper windows are formed by a print-and-etch process, there is no restriction on entry copper thickness. The low-power CO, laser does not melt or recast target pad copper.

There are two etched window processes practiced. The conformal etched copper window process consists of an etched copper window diameter that is less than the  $CO_2$  beam diameter, so the copper window defines the microvia diameter. The oversized etch copper

window process consists of an etched copper window diameter that is greater than the  $CO_2$ beam diameter, so the  $CO_2$  laser beam diameter defines the microvia diameter.

#### 4. Laser Direct Drill With CO<sub>2</sub>

The laser direct drill (LDD) process uses a high-power  $CO_2$  laser to drill through thin, specially coated copper foil and through glassreinforced dielectric. After piercing the entry copper, the  $CO_2$  laser parameters are adjusted to reflect off the target pad; therefore, it does not melt or recast the copper surface of the target pad. The cut through the thin treated copper does leave the characteristic melted and recast copper feature around the rim of the outer layer copper foil. The entry copper foil must be less than 9-µm thickness and treated to absorb the  $CO_2$  beam.

After laser drill, a series of chemical operations remove the residue from the target pad left by the  $CO_2$  laser. These operations will be covered in future papers.

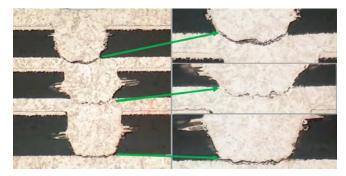

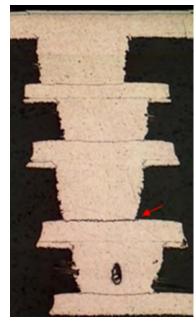

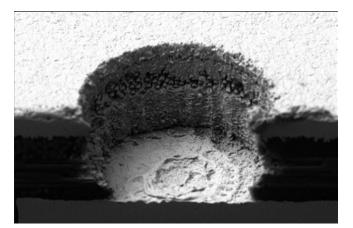

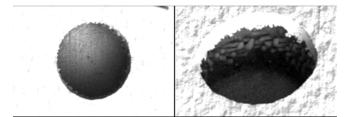

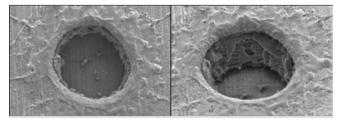

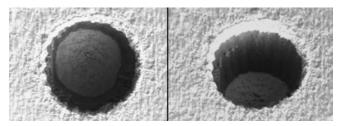

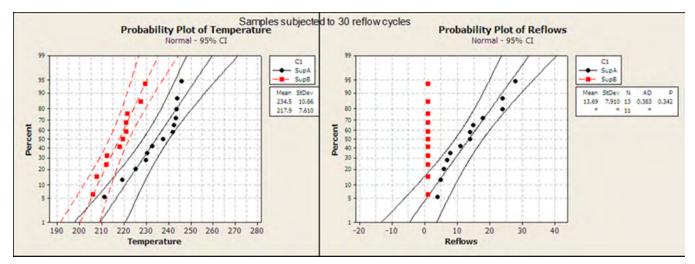

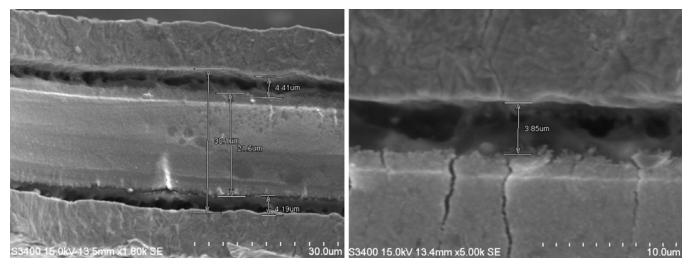

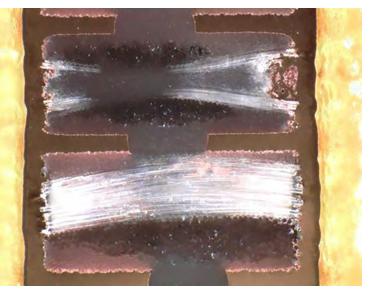

Reflow-induced failures were observed to follow demarcations between the copper fill and target pad. Demarcations in microvias visually vary for different laser processes. Figures 4–6 provide examples produced by different laser processes. Figure 4 is a UV-CO2-UV cleaned microvia stack, which failed in six reflow cycles. Figure 5, a UV-formed stack, failed in the first reflow cycle. Figure 6, an LDD CO2 laser-drilled stack, survived 30 lead-free reflow passes with a peak temperature of 245°C.

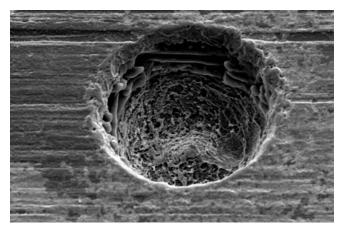

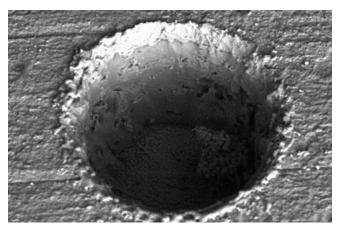

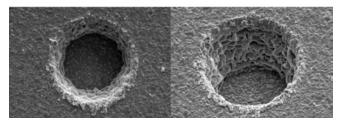

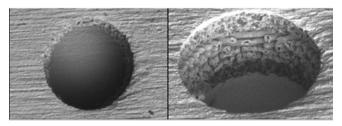

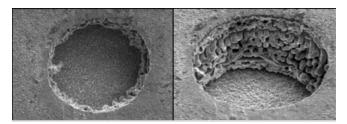

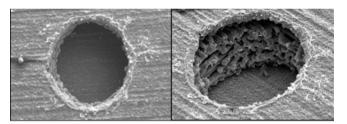

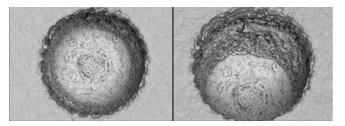

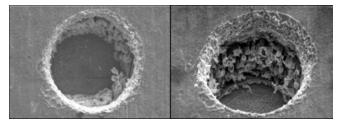

Figures 7 and 8 are SEMs of a 0.003"-diameter microvia at 30° tilt and 1000x magnification. Figure 7 is after UV laser drill, and Figure 8 after electroless copper. The microvia was UV laser drilled in 0.5-oz. outer layer copper foil and 106 prepreg. Figure 7 shows the target pad condition after UV laser ablation. The copper surface of the target pad was modified. Also visible is a copper burr and scalloping on the rim of the outer layer copper. Spherical copper particles are attached to the microvia sidewall. Figure 8 is a picture taken after 40 µin of electroless copper was deposited. An agglomeration of small spherical copper particles was trapped inside the microvia. Cracks are visible in the 40 µin copper deposit. Features outside the target pad are interesting, but because failures were observed between the plated copper fill and the target pad, this investigation focused on the condition of the target pad im-

Figure 4: UV-CO<sub>2</sub>-UV laser-drilled microvia stack that failed in six reflow cycles. Red arrow points to failure.

Figure 5: UV laser-drilled microvia stack that failed first reflow cycle. Red arrow at layer 3 points to failure.

Figure 6: CO<sub>2</sub> laser direct drill microvia stack survived 30 lead-free reflow cycles.

### InPro<sup>®</sup> MVF2 Advanced HDI BMV filling

## Advanced BMV filling in vertical conveyorized systems for HDI production

BMV filling with dimple < 5  $\mu m$  and surface copper 12  $\mu m$

Over 70% throwing power in through holes with AR 6.4:1

Our next generation filling process is designed for vertical conveyorised systems with insoluble anodes. It offers much improved filling performance and a wider working window compared to older generation products. By filling at lower surface thickness InPro<sup>®</sup> MVF2 enables cost saving potential and allows for finer resolution. The new process is applicable for next generation HDI BMV filling and also for half-filling in Flex application.

A/dm<sup>2</sup> applicable current density

12

$\mu m$  plated copper necessary for BMV filling (100×75  $\mu m)$

Atotech Group +49 30 349850 info@atotech.com

Figure 7: UV laser-drilled 3-mil diameter microvia at 30° tilt, 1000x magnification.

mediately after laser drill. As shown in Figure 7, a significant portion of the copper target pad was ablated away and left roughened by the UV beam. The manufacturer's UV laser process intentionally drilled into the copper surface to remove perceived contaminants before further processing.

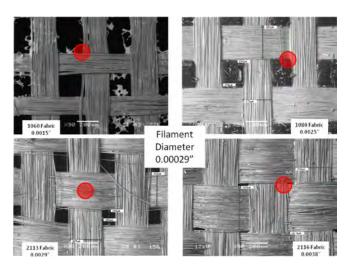

UV laser parameters are selected by drilling test arrays of microvias that are assessed and judged by how visually clean the target pads appeared as viewed by optical microscopy. The diameter and copper appearance of the exposed target pad were compared to the microvia entry diameter and outer layer copper. The test array contained enough microvias to establish parameters aggressive enough to account for the variation in laminate glass content. Figure 9 shows examples of typical glass fabric yarn density. A 0.006"-diameter microvia drawn as a red circle is provided for reference. Glass density was greatest at fabric knuckle locations where warp and weft yarns overlapped, and least in the weave openings between the glass yarns. The variation in glass density in the beam path required parameters set aggressive enough to completely clear all the microvias and to accommodate localized material thickness variations typically encountered in multilayer panel fabrication. Material considerations ensure that some microvias receive too much laser energy.

The UV ablation of copper produced a visually modified copper target pad surface that failed frequently when used in stacked micro-

Figure 8: UV laser-drilled 3-mil diameter microvia after electroless copper at 30° tilt, 1000x magnification.

vias. SEM views of the ablated copper surface of the target pad revealed structures that looked like melted copper, copper flow patterns, sputtered copper, and recast copper <sup>[3]</sup>. The structures present in UV-ablated copper target pads are not present on target pads following CO<sub>2</sub> laser ablation. UV-ablated copper filled microvias were more fragile than those formed by other laser processes.

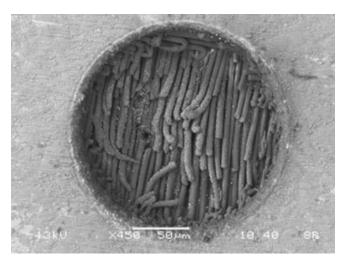

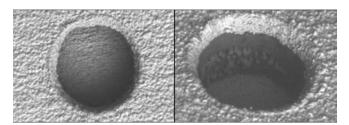

Figures 10 and 11 show two different UVablated microvias that compare different UV beam parameter settings and their effect on the target pad. In Figure 10, the UV beam settings produced a smoother target pad surface compared to the UV parameters used in Figure 11. In Figure 10, a concentric circular structure

Figure 9: Typical glass fabric yarn styles used in microvia construction. The red circle represents a 6-mil diameter microvia for reference.

Figure 10: SEM SE (secondary electron) view of UV laserdrilled microvia with gentle UV ablation parameters.

is visible at location C that looks like copper waves propagating from the smoother copper B region. These features were produced by the action of the UV beam repeatedly trepanning in pulses over the copper target pad. Copper waves propagated from the center of the target pad as the beam repeatedly punched the central region. A chain of copper craters at arrow A located at the perimeter of the target pad follows the UV beam pitch pattern. Both pictures show that copper melted, flowed, and solidified to form these patterns. Similar copper melt structures were also present on the rim around the copper edge of the outer layer copper around the entrance of the microvia. The change in copper morphology by the action of the UV laser beam shown in the SEM pictures are the unusual features seen at the demarcation of Figure 3 associated with fractures. These features were only present on the target pads of microvias touched by the UV laser beam.

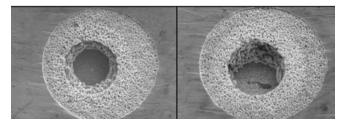

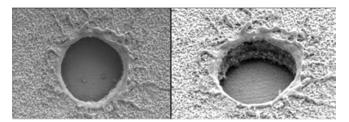

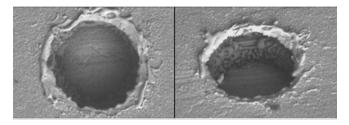

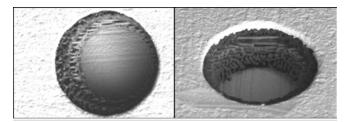

SEM analysis revealed more detail than optical microscopy. Additional SEM photographs were taken of samples fabricated by the UV- $CO_2$  laser, the  $CO_2$  laser used in the etched oversized window and conformal mask processes, the  $CO_2$  laser used in LDD, and the UV laser. The pictures are provided to inspire further discussion. Figures 12 shows views of UV- $CO_2$  laser-drilled microvias at 0° and 30° tilt. The UV laser initially opens a window in the copper foil and ablates a little bit into the epoxy glass (Figure 13).

Figure 11: SEM BSE (backscattered electron) view of UV laserdrilled microvia with aggressive UV ablation parameters.

Figure 12: SEM SE view of UV-CO<sub>2</sub> laser-drilled microvia at 0° tilt (L) and 30° tilt (R).

Figure 13: SEM SE view at 0° tilt of UV-CO<sub>2</sub> laser-drilled microvia after the UV laser drill step opened a window in the copper foil and before the  $CO_2$  laser completes the microvia ablation to the target pad.

The CO<sub>2</sub> laser then removes the remaining epoxy glass material and leaves a very thin resinous film as it reflects off the copper target pad <sup>[2]</sup>. The initial UV laser step leaves a copper burr of melted and recast copper as it clears

the foil copper. A burn mark is visible on the outer layer copper foil surrounding the microvia. Copper droplets and spheres were also scattered on and around the microvia. Some of the tips of the glass fibers were melted and fused together. The target pad was undisturbed because the UV laser never touched the target pad.

Figure 14 shows views after desmear and electroless process of a microvia from the same manufacturer. The process did not remove the melted and recast copper burr from the rim of the microvia opening. After desmear, the glass fibers protruded more from the microvia sidewall. The glass fabric influenced the texture of the sidewall because of the localized glass fiber density. No visual copper anomalies were seen on the target pad.

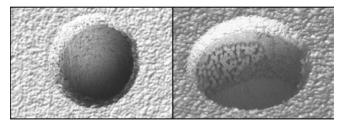

Figure 15 shows microvias from a manufacturer that etched a 245- $\mu$ m oversized copper window in the copper foil and then drilled the microvia with a 100- $\mu$ m diameter CO<sub>2</sub> laser. The oversized window exposed the laminate to allow the CO<sub>2</sub> laser to drill the microvia. The 245- $\mu$ m copper window was slightly smaller than the 250- $\mu$ m capture pad that eventually capped the filled microvia. The copper surface and rim of the chemically etched copper foil were clean and well defined since no UV laser

Figure 14: SEMs SE view at 0° tilt of UV-CO<sub>2</sub> laser-drilled microvia after desmear and electroless process at 0° tilt (L) and 30° tilt (R).

Figure 15: SEM view of  $CO_2$  laser-drilled microvia inside chemically etched oversized copper window at 0° tilt (L) and 45° tilt (R).

was used. This process exposed a substantial amount of bare laminate around the microvia. There was some discoloration visible on the target pad, but no melted and recast copper damage. The discolorization was due to a thin residual film that remained on the target pad surface. This phenomenon occurs in all  $CO_2$  laser processes.

Shown in Figure 16 are views of the oversized window with the  $CO_2$  laser-drilled microvia after desmear and electroless copper.

Desmear removed the thin resin film from the target pad, caused the glass fibers to protrude more from the microvia sidewall and increased the resin texture exposed in the copper window. Electroless copper plated directly over the bare laminate inside of the window. Most of the capture pad formed over the bare laminate with only a small portion overlapping the copper foil. Chemically deposited copperto-laminate adhesion is less than the adhesion of laminated copper foil. The diameter of the window was selected to accommodate the cumulative alignment tolerance necessary to make sure the CO<sub>2</sub> laser-drilled the microvia within the window. No target pad melting and recast of copper was visible.

Figure 17 shows views of a  $CO_2$  laser-drilled microvia through a conformal copper mask. The copper etched window diameter in this process was the same or slightly smaller than the  $CO_2$  beam diameter. No laminate surface was exposed. The window masked the oversized  $CO_2$  laser beam and therefore defined the microvia diameter. The edge and surface of the copper foil were clean and well-formed since copper was not melted and recast. No target pad melted and recast copper was visible.

Figure 16: SEM view of CO<sub>2</sub> laser-drilled microvia inside chemically etched oversized copper window after desmear and electroless copper at 0° tilt (L) and 30° tilt (R).

Software YELO

Yield Enhancing Layout Optimizer

- O Optimizes board layouts within minutes

- Cuts back CAM cycle time & cost by up to 30%

- O Lowers technology class improving manufacturability

- Reduces scrap and delivers a more reliable product

- O Return on Investment within the first year

#### Need a Gerber Viewer?

Ucamco, caretaker of the Gerber format, presents its new Reference Gerber Viewer. Use this free online tool to view and/or check your generated/received Gerber jobs.

- Reads X2 attributes containing PCB fabrication data - Imports Excellon and NC drill files

Go ahead and link your site to https://gerber.ucamco.com

UcamX

Read more -

Software

Gerber Viewer

New ground-breaking CAM Software

- O For Rigid, Flex and HDI PCBs

- O New Graphical User Interface with Workspaces

- Optimal performance using Parallel Processing

- Multi Job Processing via load balanced Sessions

- Support for Gerber version 2 (X2) format

For more information please contact info@ucamco.us, call (415) 508-5826 or check out our website at www.ucamco.com

Figure 17: SEM view of  $CO_2$  laser-drilled microvia aligned to a chemically etched conformal copper window at 0° tilt (L) and Figure 17. SEM view of  $CO_2$  laser-drilled microvia aligned to a chemically etched conformal copper window at 0° tilt (L) and 45° tilt (R).

Figure18: SEM view of CO<sub>2</sub> laser-drilled microvia aligned to a chemically etched conformal copper window after desmear and electroless copper at 0° tilt (L) and 45° tilt (R).

Figure 18 shows views of the CO<sub>2</sub> laser-drilled microvia through the conformal mask process following desmear and electroless copper metallization. After desmear, the glass fibers appeared to protrude more from the microvia sidewall. The electroless copper deposit peeled from the melted tips of the glass fibers. No laser-induced copper target pad modification was visible.

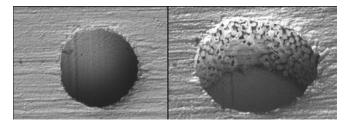

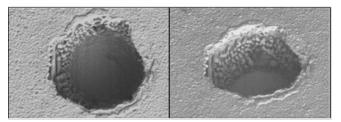

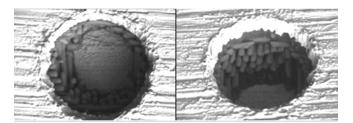

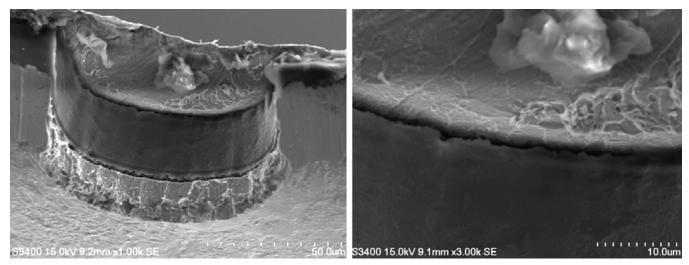

Figure 19 shows views of the  $CO_2$  LDD microvia process. The microvia was formed by direct  $CO_2$  laser ablation through oxide treated 9 micron thick copper foil. The microvia diameter and roundness depended on the  $CO_2$  beam diameter and quality. In this case, the outer layer copper foil showed melted and recast copper surrounding the microvia opening, but no  $CO_2$  laser-induced melting and recast of copper on the target pad.

Figure 20 shows the CO<sub>2</sub> LDD microvias after mechanical brush scrub, desmear, and electroless copper metallization. The brushing operation was completed after laser drill and was necessary to remove the surface oxide before the next process to prevent contamination of equipment and chemistry. Brushing was also the best

Figure 19: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil at 0° tilt (L) and 45° tilt (R).

Figure 20: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil after mechanical brush scrub, desmear, and electroless copper at 0° tilt (L) and 45° tilt (R).

Figure 21: SEM view of CO<sub>2</sub> laser direct drilled microvia through oxided 9-mm copper foil from another supplier illustrating variation in beam quality at 0° tilt (L) and 45° tilt (R).

practical method to remove the melted and recast copper that surrounded the microvia. The brushing process left directional brush marks in the copper foil. Brush marks visible on the target pad were created before the current layer was laminated. No other CO<sub>2</sub> laser-induced copper target pad modification was visible.

Figure 21 shows views of a CO<sub>2</sub> LDD laserdrilled microvia from another supplier. A similar process was used to oxide the copper foil. The roundness of the microvia was directly related to the roundness and uniformity of the CO<sub>2</sub> laser beam. A substantial amount of ablated outer layer copper was melted and recast around the rim of the outer layer of the mi-

Figure 22: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil after mechanical brush scrub, desmear, and electroless copper at 0° tilt (L) and 45° tilt (R).

Figure 23: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil from another supplier illustrating better beam quality at 0° tilt (L) and 45° tilt (R).

crovia. No CO<sub>2</sub> laser-related melted and recast copper was visible on the target pad.

Shown in Figure 22 are images of the CO<sub>2</sub> LDD drilled microvia after desmear and electroless metallization. No copper foil brush marks were visible from the deburr process used to remove the surface oxide and the laser formed copper burr.

Figure 23 shows a microvia from another supplier's  $CO_2$  LDD microvia process. The outer layer copper foil was oxidized before LDD ablation. The microvia roundness was better than the  $CO_2$  beam quality of the previous supplier's LDD formed microvia. Melted and recast copper were formed around the rim of the outer layer copper.

Figure 24 shows the CO<sub>2</sub> LDD drilled microvia after desmear and electroless copper. No brush marks were visible following the deburr process used to remove the oxide and recast copper burr. However some of the copper foil around the rim was damaged, which changed roundness of the microvia. No melted and recast copper anomalies were formed on the target pad.

Figure 25 shows CO<sub>2</sub> LDD microvias from another supplier. A substantial amount of melted

Figure 24: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil after mechanical brush scrub, desmear, and electroless copper at 0° tilt (L) and 45° tilt (R) showing copper foil damage.

Figure 25: SEM view of  $CO_2$  laser direct-drilled microvia through oxided 9-mm copper foil from another supplier showing variation in degree of laser-induced surface copper recast at 0° tilt (L) and 45° tilt (R).

Figure 26: SEM view of CO<sub>2</sub> laser direct-drilled microvia through oxided 9-mm copper foil after mechanical brush scrub, desmear, and electroless copper at 0° tilt (L) and 45° tilt (R) showing brush marks on the copper foil.

and recast copper was spread on the outer layer around the microvia.

The roundness of the microvia matched the  $CO_2$  beam quality. The microvia sidewall shows melted and fused tips of glass fibers—a condition typically present with  $CO_2$  laser ablation of glass-reinforced dielectric material. Brush striations can be seen on both the outer layer copper foil and target pad. No melted or recast copper was visible on the target pad.

Figure 26 shows SEMs of the  $CO_2$  LDD microvia after desmear and electroless copper metallization. Brush marks were still visible.

Figure 27: SEM view of CO<sub>2</sub> laser-drilled microvia inside slightly oversized chemically etched copper window illustrating degree of alignment at 0° tilt (L) and 45° tilt (R).

Figure 28: SEM view of CO<sub>2</sub> laser-drilled microvia inside slightly oversized chemically etched copper window after desmear and electroless copper at 0° tilt (L) and 45° tilt (R).

Figure 27 shows SEMs of a microvia that was  $CO_2$  drilled within a slightly oversized copper etched window. In this process, the  $CO_2$  beam diameter was only slightly smaller than the copper window diameter therefore the  $CO_2$  beam defined the microvia diameter. The window diameter was smaller than the window diameter used in the process shown in Figure 15. Less laminate was exposed therefore a greater portion of the capture pad was formed over the copper foil, which provided a better anchor into the laminate. The chemically etched windows in copper foil did not require a deburr process. No melted or recast copper was produced on the target pad.

Figure 28 shows the oversized window and CO<sub>2</sub> laser-drilled microvia after desmear and electroless copper.

Figure 29 are SEMs of a UV laser-drilled microvia. The UV beam parameters were selected to minimize target pad damage. Just a small amount of UV-induced melted and recast copper was visible at 12:00 on the target pad in Figure 45. Substantial brush stroke striations were visible on the outer layer copper foil.

Figure 29: SEM view of UV laser-drilled microvia with parameters minimizing target pad damage at 0° tilt (L) and 45° tilt (R).

Figure 30: SEM view of UV laser-drilled microvia after desmear and electroless copper at 0° tilt (L) and 45° tilt (R). Example of microvia formed in location crossing glass yarns.

A small amount of melted and recast copper was visible around the rim of the microvia. No visible glass fibers were melted or fused together. Figure 30 shows the UV laser-drilled microvia after desmear and electroless copper metallization. Melted and recast copper was visible around the rim of the microvia. The desmear operation included a glass etch step that etched away a substantial amount of the glass fibers. No glass fibers were observed protruding from the microvia sidewall. Small cracks were visible in the electroless copper deposit on the microvia sidewall.

The gentler UV laser parameter left less melted and recast copper on the target pad and produced a greater microvia sidewall taper that substantially reduced the microvia contact area to the target pad. The UV laser parameters were set aggressively enough to account for the heaviest glass content and thickest dielectric variation across the laminate to make sure the microvia was fully formed. Microvia target pads located in the openings between the glass yarns and in thinner dielectric region received too much UV ablation.

## freedom of design

## 1502

Isola's RF/MW products provide superior solutions to your RF/MW challenges.

## RF/ MICROWAVE HIGHLY ENGINEERED MATERIALS

#### Astra<sup>®</sup> MT77

Astra® MT77is an ultra low-loss dielectric constant for 77 GHz automotive radar and sensor designs, long antennas, DAS & CPE antennas, feed networks and millimeter wave frequency applications and is a cost-effective alternative to PTFE.

#### I-Tera® MT40

I-Tera® MT40 is a very low Dk Df resin system up to 20 GHz. Used in daughter card, back-plane and hybrid designs, it's a highly reliable system for sequential lamination, lead-free assembly, blind and buried via and CAF sensitive designs.

#### **TerraGreen**<sup>®</sup>

TerraGreen® is a halogen-free Low Dk Df resin system engineered for such high performance applications as power amplifier boards for 4G LTE base stations, Internet infrastructure and cloud computing.

#### IS680 / IS680 AG

IS680 laminate materials exhibit exceptional electrical properties which are very stable over a broad frequency and temperature range. Suitable for many of today's commercial RF/ microwave printed circuit designs. IS680 AG offers an ultra-low Df, making it an extremely cost-effective alternative to PTFE.

© 2019 ISOLA GROUP. ALL RIGHTS RESERVED.

#### RF/MICROWAVE • AEROSPACE & DEFENSE • AUTOMOTIVE & TRANSPORTATION

FOR MORE INFORMATION

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

The SEMs in Figure 31 are of the UV laserdrilled microvia from another supplier. The images show a significant amount of melted and recast copper on the target pad. The rim of the outer layer copper foil was melted and recast. The laser beam pitch was visible on the rim and sidewall of the microvia.

Figure 32 shows the UV laser-drilled microvia after desmear and electroless copper. Some melted and recast copper is visible around the rim of the microvia. Also visible is the extent of melted and recast copper on the target pad.

Figure 33 shows pictures of a UV-CO<sub>2</sub> laserdrilled microvia. Melted and recast copper was visible around the rim of the outer layer copper foil and at the target pad. The tips of the glass fibers were melted and some were fused together.

Figure 34 shows the UV-CO<sub>2</sub> laser-drilled microvia after desmear and electroless copper. The UV laser did not drill a perfect circle. Also, there was some misregistration between the UV and CO<sub>2</sub> laser beams. The electroless copper deposit appeared to be cracking and flak-

ing off the glass fibers. Some melted and recast copper was visible on the target pad, which suggested either very aggressive initial UV parameters were used that allowed the UV beam to pierce the dielectric and hit the target pad, or a UV clean-up process was used after  $CO_2$  ablation.

Figure 35 shows a UV-CO<sub>2</sub> laser-drilled microvia from another supplier. A melted and recast copper burr was formed around the rim of the microvia, but no melted or recast copper was observed on the target pad.

Figure 36 shows the UV-CO<sub>2</sub> laser-drilled after desmear and electroless copper. Electroless copper cracked and peeled off the melted tips and fused glass fibers.

The SEMs show that copper target pad surface structure is different for UV and  $CO_2$  lasers. The UV laser leaves melted and recast copper on the target pad, but the  $CO_2$  does not. The high-power  $CO_2$  LDD laser does this only on the entry copper that is not the source of failures that form during reflow assembly.

Reflow-tested samples compared UV-CO<sub>2</sub> (supplier A) and UV (supplier B) laser-drilled

Figure 31: SEM view of UV laser-drilled microvia from another supplier with parameters that modified the morphology of target pad 0° tilt (L) and 15° tilt (R).

Figure 32: SEM view of UV laser-drilled microvia from another supplier after desmear and electroless copper at 0° tilt (L) and 15° tilt (R). UV parameter modified the morphology of the target pad.

Figure 33: SEM view of UV-CO<sub>2</sub> laser-drilled microvia at 0° tilt (L) and 45° tilt (R) with recast copper around the rim of the UV-formed copper window.

Figure 34: SEM view of UV-CO<sub>2</sub> laser-drilled microvia after desmear and electroless copper at 0° tilt (L) and 45° tilt (R). Example of slight misregistration between UV and  $CO_2$  beams.

Figure 35: SEM view of UV-CO<sub>2</sub> laser-drilled microvia from another supplier at 0° tilt (L) and 45° tilt (R) with a recast copper burr around the rim of the UV-formed copper window.

microvias. Figure 37 shows probability plots comparing the two different laser-drilled microvia responses to reflow assembly thermal stress. Samples were subjected to 30 lead-free reflow cycles with peak temperature to 245°C. The Tg of the laminate was 175°C. The probability plot of temperature (L) recorded the temperature when an open was detected. The probability plot of reflows (R) plotted reflow cycles to failure. Both the mean failure temperature and cycles to failure for UV-drilled microvias failure were lower than means for UV-CO, laser-drilled microvias. These results suggest that UV laser-modified copper surfaces produced weaker microvia interfaces. This finding is important because many microvias formed by UV-CO, laser processes today add a UV laser cleaning step [4]. Unknown is the extent of change in copper morphology by the UV copper surface cleaning step and its effect on reflow survivability.

Figure 36: SEM view of UV-CO<sub>2</sub> laser-drilled microvia after desmear and electroless copper at 0° tilt (L) and 45° tilt (R).

#### Conclusions

Stacked microvias solve PWB circuit congestion driven by increased silicon content, density of input/output paths to accommodate functionality, and smaller footprints. It was observed that fabricators' ability to produce reliable stacked microvias varied. Stacked microvias fracture during the reflow assembly process. Stacked microvia fractures were observed at interfaces between the copper fill and target pad. Staggered microvias, however, did not fail.

Presented material focused on the visual condition of the copper surface of the target pad immediately after laser drill. There is significant variation in the final surface morphology of the target pad after laser drill among the different techniques used by PWB fabricators. UV lasers created visible copper morphology changes not observed with the various  $CO_2$  laser processes. UV laser-modified

Figure 35: SEM view of UV-CO<sub>2</sub> laser-drilled microvia from another supplier at 0° tilt (L) and 45° tilt (R) with a recast copper burr around the rim of the UV-formed copper window.

copper morphology was reported to increase copper hardness and decrease ductility <sup>[3]</sup>. The features—those identified in the cross-sections and SEM photographs through which fractures formed and propagated during assembly reflow thermal stress—coincided with failures. Chemical species analysis at the copper surface of the target pad of an actual microvia after laser drill was not possible due to microvia sidewall, outer layer copper, and sample preparation interference. Further investigations are encouraged.

Probability plots of UV-CO<sub>2</sub> and UV laserdrilled microvias indicate the UV laser-drilled ones frequently fail during the first reflow pass while stacked microvias formed by CO<sub>2</sub> laser processes survived up to 30 reflow assembly cycles. This suggests the UV modified copper surface of the target pad results in a weak interface that fractures during reflow assembly.

Until the root cause of stacked microvia failures is determined and problem solved, staggered microvias must be used for mission critical and high-hazard environments. The window for staggered microvias is closing as the reduction in pitch and increased circuit density forces the use of stacked microvia constructions. **PCB007**

#### References

1. Magera, J., et al., "IPC-WP-023," May 2018.

2. Inaba, R., Kawamura, T., Akahoshi, H., Arai, K., "Studies on CO<sub>2</sub> Laser Drilling: Formation Mechanisms of Residual Thin Materials at the Bottom of Laser Via," *IEEE Transaction on Electronic Packaging Manufacturing*, Vol. 24, No. 1, January 2001.

3. Duley, W. W., UV Lasers: Effects and Applications in Materials Science, University of Waterloo, Ontario, Cambridge University Press, 1996.

4. Zhang, J., Wang, Y., Cheng, P., Lawrence Yao, Y., "Effect of Pulsing Parameters on Laser Ablative Cleaning of Copper Oxides," *Journal of Applied Physics*, Vol. 99, No. 1, 2006.

This paper was first presented at the IPC APEX EXPO 2019 Technical Conference and published in the 2019 Technical Conference Proceedings.

Jerry Magera is a senior staff chemical engineer in the Motorola Solutions Quality and Reliability Group and the vice chairman of the IPC D-32 Thermal Stress Test Methodology Subcommittee.

**J.R. Strickland** is a senior quality manager with Motorola Solutions Inc. in the Applied Technology Business Unit.

#### A Tribute to Greg Beck

Recently, our industry lost one of its veterans—Greg Beck, owner of Beck's Light Gauge Aluminum Company. He passed away unexpectedly in Lake Zurich, Illinois, on May 2, 2019. He was a passionate and committed executive who built a successful business around thin-gauge steel and aluminum processing for high-technology appli-

cations.

The company was founded by George Beck, Greg's father, who was also very prominent in the industry. Last year, Greg and his company joined the Insulectro family of companies through acquisition. Greg's pioneering work with American-sourced aluminum was a perfect fit for Insulectro's line of business. We appreciated Greg's enthusiasm for the blending of the businesses and his guidance and direction as he stayed on to continue his extraordinary work.

"On behalf of all my fellow teammates, we celebrate Greg's life. We salute the successes Greg accomplished for our industry, and we pay tribute to his visionary legacy which will remain a guiding light in our business. Insulectro will name its light-gauge metal processing line in both our Chicago-area and our Orange County, California, facilities in honor of Greg," Insulectro President and CEO Patrick Redfern commented. "Our thoughts and prayers continue to be with Greg's family and friends, and the business colleagues who knew him and worked with him and recognized his genius." (Source: Insulectro)

#### Having trouble keeping up with front-end demand? **We have people for that.**

Here are six ways that outsourcing CAM and related front-end work can help manufacturers not only stay in business but also help them thrive:

- Increased on-demand capacity

- Improved automation

- Faster turn-around times

- Reduce costs

- Improved quality

- Ability to build redundancy in critical areas

We deliver the highest quality PCB CAM and Mechanical CAD engineering services to customers around the world.

Find out how we can help you >

### Interconnect Reliability Correlation With System Design and Transportation Stress

#### Feature by Dr. Paul Wang, Vincent Weng, and Dr. Kim Sang Chim MITAC INTERNATIONAL INC.

#### Abstract

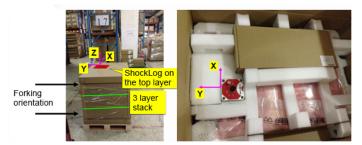

Interconnect reliability-especially in BGA solder joints and compliant pins, which are subjected to design parameters—is very critical to ensure product performance at predefined shipping conditions and user environments. Plating thickness of the compliant pin and the damping mechanism of electronic system design are key success factors for this purpose. In addition, transportation and material handling process of a computer server system will be affected by shock under certain conditions. Many accessory devices in the server computer system tend to become loose, resulting in poor contact or solder intermittent interconnect problems due to the shock load from the transportation and material handling processes.

In this article, design variables—such as pin hard gold plating thickness, motherboard locking mechanism, and damping structure design—are experimented and reviewed. Also,

a shock measurement device is used to realtime monitor the acceleration, duration, and direction of shock in large stationary or moving systems in transportation and transferring process. There were two transportation routes from Fushan, China, to Sezimovo, Czech Republic, through the China and Russia border by train and returned by sea cargo through the Mediterranean, Arabic, and South China Seas in which a product package was embedded with a shock measurement device. The collected force data of g-force can be used to calculate the shock energy level,  $\Delta V$ . The comparison between the value of  $\Delta V$  and shock energy tested in the lab can be used to judge whether a system design can sustain and cause contact interconnect problems in the transportation and transferring process. These design variables and stresses can be evaluated by drop test or vibration test to ensure system functional integrity is achieved.

#### Introduction

Reliability of BGA solder joints and compliant pin interconnects is critical to ensure product performance is maintained at predefined

INTERNATIONAL SUPPLIES

## **Machines for Printed Circuit Boards**

| Spray Coatings & Ovens                                                                                                                                                                                                                       | Drilling & Routing Systems                                                                                                                                                                         | Prep, Plating & Finishing                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Precision Spray Coating<br/>+/-5µm Thickness Control</li> <li>Up to 6 Colors on Demand</li> <li>Self Cleaning Spray Guns</li> <li>System Fully Automated<br/>with Process Control Logs</li> <li>To Minute FAST TACK OVEN</li> </ul> | <ul> <li>Optical Drilling &amp; Routing</li> <li>X-Ray Assisted Drilling &amp; Routing</li> <li>X-Ray Optimizer</li> <li>Marking &amp; Traceability</li> <li>Automated Flash-rout/Bevel</li> </ul> | <ul> <li>Pumex &amp; Scrubbex</li> <li>30 + Years of Service</li> <li>Digital Process Controls<br/>Deliver Precision,<br/>Accuracy &amp; Repeatability:</li> <li>DES &amp; SES Lines</li> <li>MecEtch &amp; Multibond</li> <li>Direct Metalization</li> <li>OSP &amp; ENIG</li> <li>Electroless Tin/Silver</li> </ul> |

ec

Figure 1: Example of partial loose contact of a daughter card from a press-fit connector.

shipping conditions and user environments. Many electronic devices—such as network cards HDDs in the server system—tend to become loose, resulting in poor contact problems due to the severe shock from the transportation and material handling processes. Different design variables—such as hard gold plating thickness on the pin, motherboard locking mechanism, and damping plate—are experimented and reviewed in this article. A shock measuring device was used to monitor in real-time the acceleration, duration, and direction of shock in large stationary or moving systems in the transportation and transferring process.

Poor contact issues happened on some models of desktop, AIO, and server computer systems. After removing the top cover of a computer system, some accessories—such as memory and NIC cards—were found to be partially disengaged from their normal interconnect positions (Figure 1). An example of a contact inter-

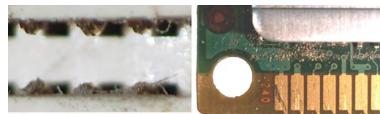

Figure 2: Dust and fiber accumulated in DIMM slot (L) and particles found near DIMM contact pads (R).

connect defect rate for a specific experimental test vehicle is shown in Table 1. In most of the cases, these contact problems may not be permanent but can be quickly resolved by double insertion of the interconnect system.

Although not the main topic of this study, another source of contact interconnect problems <sup>[1]</sup> is coming from particles or fibers from raw material, manufacturing, or the user environment can be observed from time to time in DIMM socket pins and circuit board contact pads. These foreign materials can create a barrier for proper contact between pad and socket (Figure 2). In one extreme case, soft white plastic particles were smeared on the contact surface, creating a risk of intermittent contact or open circuit (Figure 3). FTIR organic chemical analysis indicated that the fibers were rayon/ cellulose, which is a common material from various sources-such as cloth and gloveswhich are difficult to clearly implicate in a failure. However, the white particles are most likely polyethylene from plasticizer—a fatty acid that poses an interconnect concern (Table 2).

To avoid the accumulation of fibers and particles on contact pads, there are many changes required in environment control and management for sensitive interconnect devices, such

| Model XXX to location Y  | 20xx/6 to 20xx/4 | May | Jun      | Jul | Aug      | Defect Rate |

|--------------------------|------------------|-----|----------|-----|----------|-------------|

| Total tested Qty         | 2265             | 229 | 119      | 207 | 155      | 2975        |

| HDD poor contact Qty     | 22(0.97%)        | 0   | 0        | 0   | 1(0.65%) | 23(0.77%)   |

| NIC/SSL poor contact Qty | 8(0.35%)         | 0   | 1(0.84%) | 0   | 0        | 9(0.30%)    |

| Mem poor contact Qty     | 0                | 0   | 4(3.36%) | 0   | 0        | 4(0.13%)    |

| Cable poor contact Qty   | 1(0.04%)         | 0   | 0        | 0   | 0        | 1(0.03%)    |

| Total poor contact Qty   | 31(1.37%)        | 0   | 5(4.2%)  | 0   | 1(0.65&) | 37(1.24%)   |

Table 1: Defect rate of a series of computer server systems.

Figure 3: Close-up view of particles on DIMM contact pads.

as press-fit pins and optical modules. The use of particle counters is getting popular in particulate control on the manufacturing floor along with connector vacuuming, cleaning, and reseating/inserting an edge card. Again, in most cases, these contact problems may not be permanent but can be quickly resolved by double insertion of the interconnect system to provide a clean contact interconnect interface.

#### Approach

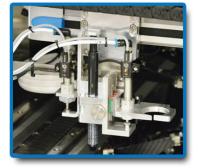

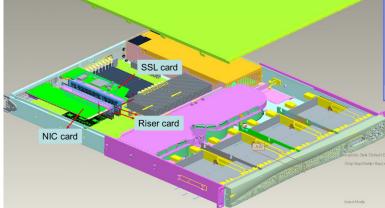

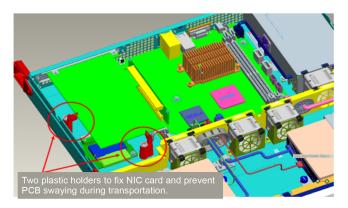

In this study, a realistic test vehicle (Figure 4) is designed with a commercially available press-fit connector of various sources on to a motherboard with full electrical function. A riser card is plugged into the press-fit connector that serves as an interface for NIC and SSL card interconnect. The following three design variables were experimented on in addition to the pallet of test vehicles with an installed shock measurement device were shipped

Figure 4: Test vehicle with press-fit connector and riser card interface for NIC and SSL interconnect.

through two shipping routes as train and sea cargo to see the correlation to the function failure of the test vehicle:

- Damping plate for NIC and SSL cards

- Hard gold plating thickness

- Locking mechanism for motherboard

#### **Results and Discussion**

#### **Design Variable Change**

Several design variables to improve the press-fit interconnect quality are considered to be tested in the shipping routes and during material handling. Some design changes were made specifically to solve the NIC/SSL poor contact issue.

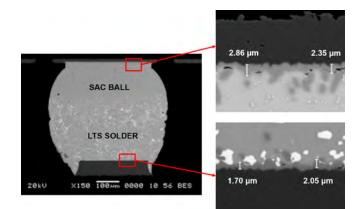

First, the plating thickness in various press-fit connectors on the test vehicle is measured. As shown in Tables 3 and 4, the gold (Au) plating thickness on some connectors is in the 1-microinch range, and on the other, is more than

| Visual<br>Appearance | FTIR Match<br>to Library | FTIR Attribution                                                  | Comment                                                                                                                                                                                                                                |

|----------------------|--------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tan fiber            | 70%                      | Rayon/cellulose                                                   | Common material, multiple sources. Rarely causes a problem (at least that can be isolated.)                                                                                                                                            |

| White particles      | 1. 92%<br>2. 91%         | <ol> <li>Ethyl triacontanoate 98</li> <li>Polyethylene</li> </ol> | <ol> <li>Plasticizer, fatty acid, possible constituent of bulk;<br/>low melting point (soft), 0.86 g/cm3</li> <li>Not common use in electronic components. Softness<br/>poses concern and is clearly engaged with contacts.</li> </ol> |

Table 2: Chemical analysis of foreign material on contact pads.

| Cards       | Model xxx        | Plating | Model xxx                                  | Plating | Model Y      | Plating | Model X                    | Plating |

|-------------|------------------|---------|--------------------------------------------|---------|--------------|---------|----------------------------|---------|

| Riser board | SN#ss(Riser PCB) | 15µ"    | SN#xxx-Riser<br>PCBx8tox8 30µ" SN#xxx Rise |         | SN#xxx Riser | 1µ"     | SN#xxx( Riser<br>PCB)      | 30µ"    |

|             |                  | ioμ     | SN#xxx-Riser PCB<br>8tox4                  | 30µ"    | connector)   | 14      | SN#xxx(Riser<br>connector) | 1µ"     |

| ЫММ         | SN#xxx           | 15µ"    | SN#xxx                                     | 20µ"    | SN#xxx       | 45.4    | SN#xxx                     | 45.0    |

| socket      | SN#xxx           | 15µ"    | SN#xxx                                     | 20µ"    |              | 15µ"    |                            | 15µ"    |

Table 3: Hard gold plating thickness of various interconnect devices.

| DESCRIPTION | PART                 | CONTACT PLATING            | MODEL | SUPPLIER |

|-------------|----------------------|----------------------------|-------|----------|

| TF-CON; SBU | 64-BIT 184 PIN PCI-X | Gold Flash (1µ" gold min.) | А     | 1        |

|             | 184 PIN              | 15µ" Gold min.             | В     | 2        |

|             | 184PIN               | 15µ" Gold min.             | С     | 3        |

| TF-CON; SBU | 98 PIN PCI-X         | 30μ" Gold min.             | D     | 4        |

|             | 98 PIN PCI-X         | 30µ" Gold min.             | E     | 5        |

|             | 98 PIN PCI-X         | 30μ" Gold min.             | F     | 6        |

| TF-CON; SBU | 164 PIN PCI-X        | 15μ" Gold min.             | G     | 7        |

|             | 164 PIN PCI-X        | 15μ" Gold min.             | н     | 8        |

|             | 164 PIN PCI-X        | 15μ" Gold min.             | I     | 9        |

Table 4: Example of plating thickness of press-fit connector.

15 microinches. By comparing the Au thickness on the connector pins in Tables 2 and 3, it shows that the Au thickness on some connectors is only 1 microinch and is more than 15 microinches on other connectors. The Au thickness measured on the poor-contact NIC/ SSL (Table 4) is also less than 15 microinches. It is thus seen that the probability of poor contact is much larger on connectors with 1-microinch Au plating than that on connectors with 15 microinches.

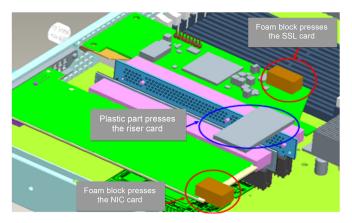

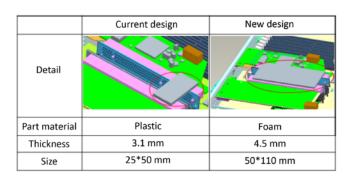

Second is the increase in damping plate area and thickness. In the original system, there were no damping plates on the riser card and NIC/SSL card. Changing the damping material from plastic to more elastic foam material helped to enhance the damping effect of the system to overcome external shock load. The new foam will continue in contact with the riser card with no gap between the foam and riser card. It can prevent the riser card from coming out of connectors under transportation stress. In the current design, the riser card was pressed by one plastic part and the NIC/ SSL card were pressed by foam (Figure 5). The exact thickness of the foam damping plate is based on the following tolerance analysis.

The tolerance analysis (TA) conducted on the stack of mechanical parts indicates that there is some tolerance among different mechanical parts when the top cover is assem-

Figure 5: Foam plates added to enhance the damping effect.

#### Electronics Coatings for the Digital Era

EMP110 Universal Direct Image Soldermask

- Widely used in medical, military and automotive applications

- Reputation for robustness and reliability

- Meets or exceeds high reliability standards

EMP110 Universal DI Soldermask is extensively used in production on the full range of direct image technologies on the market as well as offering a fast, tack-free exposure with conventional contact printers.

T +44 (0)1732 811118 info@electrapolymers.com www.electrapolymers.com

| CATS 1   |               |       |              |          | y Tolerano  | e Stack-    |          | Outputs | Report    |           |                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------------|-------|--------------|----------|-------------|-------------|----------|---------|-----------|-----------|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dimensio | ons & Tole    |       | N-Normal     | U-Unifor |             |             | Six S    | Sigma   |           | Measure   | ed Data        | Assembl | y Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Name     | Nominal       | ± Ti  | Distribution | T=±nØ    | σι          | Ср          | k        | Cpk     | σi        | Mean      | O <sub>1</sub> |         | Specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A        | 36.54         | 0.250 | N            | 3.00     | 0.08333     | 1.33        | 0.00     | 1.33    | 0.062657  |           |                |         | Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |